7-Segment LED Display

advertisement

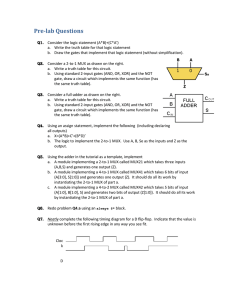

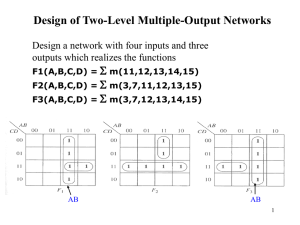

7-Segment LED Display DD: Section 5.1-5.2 Mano: Section 3.10 Topics • • • • • Using always @() Using Case Staetment Wire Versus reg Mux Use Mux to display one bit at a time always statement The sensitivity list contains a list of all signals that will affect the outputs generated by the always block. always @(*) * in the sensitivity list will automatically include all signals on the right side of your statements always @(*) can be used when you want your elements to change their values as one or more of its inputs change. always@ can be used with either non-blocking statement (if you want to execute statements in parallel) or blocking statement (if you want to execute statements sequentially) Why using always @(*) (incorrect!) (Desirable) case the number preceding : indicates the value of the case parameter. (=, implies that blocking statements are used) ‘hA means “A” in hex numbers. 7’b0000001 means 7 binary numbers with a sequence equal to 0000001 default The default statement is necessary since Verilog actually defines four possible Values for each bit: 0 1 Z (high impedance) X (unknown value) reg • All outputs generated by the always block must be declared to be of type reg. • Reg is used to suggest that the values behaves like a variable that might be stored in a register. wire Legal Uses of the wire reg Legal Uses of reg When wire and reg are Interchangable Test Bench for hex7seg_case.v Multiplexer • 2-to-1 mux • 4-to-1 mux 2-to-1 mux • A 2-input mux is controlled by a single control line s. • If s=0, y=a and y=b if s=1. Implementation 4-to-1 Mux 4-to-1 Mux (Creating a 4 x 1 MUX from 2 x 1 MUX) Multiplexing 7-Segment Displays If s[1:0]=00, then x[3:0]. If s[1:0]=01, then x[7:4]. If s[1:0]=10, then x[11:8]. If s[1:0]=11, then x[15:12]. Use Quad 4-to-1 mux Get values for an[3:0] from btn[3:0] so that only one LED is displayed.