Xilinx FPGAs:Evolution and Revolution

advertisement

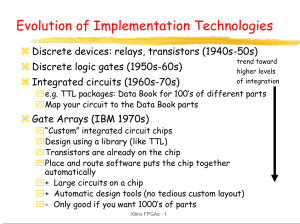

Xilinx FPGAs:Evolution and Revolution Evolution results in bigger, faster, cheaper FPGAs; better software with fewer bugs, faster compile times; coupled with better technical support. Innovative architectural and circuit features with advancements in design methodology - modular team based design & internet based configuration method: resulting in Revolution. A Decade of Progress Xilinx FPGAs : An Endless Journey XC2000 7.5K, 50MHz XC5200 0.5 micron 16K, 50MHz 50K-1M, 200MHz 4M, 250MHz 40K-8M, 420MHz 10M, 420MHz 1.5K XC3000 XC3100 XC4000 0.5 micron SPARTAN 0.35, 0.25 m VIRTEX 0.22micron SPARTAN-II 0.22 micron VIRTEX-E 0.18micron SPARTAN-IIE 0.18micron VIRTEX-II 0.15 micron VIRTEX-II PRO 0.13micron 85K, 80 MHz 100MHz+ 40K 200K, 200MHz 300K, 200MHz+ Xilinx FPGAs - Generic Features High Performance at different voltages Footprint Compatibility - Devices within each family are compatible. Low power consumption/high performance Integrated Software Technology independence - EDIF, VHDL, Verilog, SDF interfaces. XC2000 First FPGA Family from Xilinx. Two members: XC2064 1000 Gates XC2018 1500 Gates Ext. Crystal Oscillator. No Tri State Buffers. XACT 1.0 Development System. XC2000 Max.Logic Gates Max. CLB Flip-flop Max. I/O Pins Max. I/O Flip-Flop 1500 100 74 74 XC3000 Replaces TTL, MSI and other PLD logics. Integrates complete subsystem into single Package. System clock Speed up to 50 MHz. On-chip crystal Oscillator. Low-Skew Clock Nets. Over 20 different Packaging Options Interface to popular design Environment like Mentor, Cadence and View Logic. XC3000 CLB XC3100A Ultra-high-speed Family with six members. XC3195 in 22 X 22 CLB array size. Compatible with XC3000. Error checking of configuration bit stream. XC4000 CLB XC4000 Family Features Synchronous Single and Dual-Port RAM Internal Three-state buffers. JTAG Boundary Scan System performance to 80 MHz 0.5 µ SRAM Process Technology XC4000 Sub-Families Version Max. logic Gates XC4000XL 3k-85k XC4000EX 28k, 36k XC4000E 3.0-25k Max. I/O Voltage 448 320 256 3.3 5 5 XC5200 Low Cost FPGA Family. System Features: - Fast Arithmetic Functions - High Performance Clock Network - Highly routable - Easy Pin Locking - Fast wide Functions - Three-state buffers - JTAG - Performance up to 50 MHz. Resource Comparison Xilinx Spartan/XL FPGAs Xilinx 4000 Series Heritage Advanced Process Technology 100 MHz+ performance On-chip SelectRAM Software v4.2i Core solutions Small die size Low cost packaging Low test cost Total Cost Management Total Cost Management Leading edge process technology Smallest die size of any FPGA with on-chip RAM Focused package offering Low-power architecture allows use of highest volume plastic packages Streamlined test flow Lower cost test hardware Built-in self test features and shorter test times Optimized manufacturing flows Spartan-XL Family Advanced 0.35m Process Transistor gates 0.35u Allows 3.3 V supply All other features 0.25u Small size Low capacitance Performance Chip Combines 3.3 V operation with 0.25u benefits Spartan Speed Grades Higher speed grade = higher performance XL-5 E-1 -4 E-2 -3 XC4000E Spartan XL-4 -3 -4 XC5200 Spartan-XL What’s missing in Spartan? No asynchronous RAM Only RAM16(32)X1S, RAM16X1D, ROM16X1 No edge decoders No DECODEx No wired-AND No WANDx or WOR2AND Mode pins not usable as I/O No MD0, MD1, MD2 Virtex - features Densities from 50 K to 1M system gates. System performance up to 200 MHz. Multi-standard Select IO interfaces. Built-in clock-management circuitry - Four DLLs - Four Low-skew global Clock Distribution Net Hierarchical Memory System. Dedicated Multiplier Support. Spartan-II - features Densities as high as 200K gates. Streamlined features based on Virtex architecture. Very Low Cost LUT Distributed RAM and Block RAM support. Dedicated Multiplier support. 4 DLLs Virtex/Spartan-II CLB 1 CLB holds 2 slices Each slice has two sets of Four-input LUT Carry & Control Any 4-input logic function Or 16-bit x 1 RAM Or 16-bit shift register Fast arithmetic logic Multiplier logic Multiplexer logic Storage element Latch or flip-flop Set and reset True or inverted inputs Sync. or Async. Control Virtex/Spartan-II DLLs Improve Clock Networks DLL1 Manage Multiple System Clocks Deskew Clocks on Chip DLL3 Generate Clocks (Multiply, Divide, or Shift) DLL2 Deskew Clocks on Board Cascade DLLs DLL4 Convert Clock Levels using Select I/O Delay locked loops synchronize on-chip and board level clocks Virtex-E – what’s added? Up to 4 million system gates 2-4X more Block RAM 8 DLLs Differential I/O signaling (LVDS/BLVDS) some new speed grades. Spartan-IIE - features Density 50-300K Supports LVDS 4 DLLs VCCINT – 1.8V More speed grades than Spartan-II. Less packaging Options. Virtex-II All Xilinx FPGAs contain the same basic resources CLBs contain combinatorial logic and register resources IOBs interface between the FPGA and the outside world Programmable interconnect Other resources Three-state buffers Global clock buffers Boundary scan logic Virtex-II devices contain additional resources Block SelectRAM Dedicated Multipliers Digital Clock Manager (DCM) CLB Tile COUT COUT TBUF TBUF Slice S3 Slice S2 Switch Matrix SHIFT Slice S1 Slice S0 CIN Fast Connects CIN Slice Structure Slice 0 LUT Carry PRE D Q CE CLR LUT Carry PRE D Q CE CLR Mult-AND and dedicated Multiplier too SRL16 DDR Registers. Fast Carry Logic Digitally Controlled Impedance Connecting Function Generator F6 Slice S0 F5 Slice S1 F5 F7 Slice S2 F5 F6 Slice S3 F5 F8 CLB Select I/O Allows direct connections to external signals of varied voltages and thresholds Optimizes the speed/noise tradeoff Saves having to place interface components onto your board Differential signaling standards LVDS, BLVDS, ULVDS LDT Distributed and Block Select RAM LUT Slice LUT LUT RAM16X1S D WE WCLK A0 O A1 A2 A3 RAM32X1S D WE WCLK A0 O A1 A2 A3 A4 RAM16X1D D WE WCLK A0 SPO A1 A2 A3 DPRA0 DPO DPRA1 DPRA2 DPRA3 Dedicated Multiplier Block Eighteen-bit 2’s complement signed operation Optimized to implement Multiply / Accumulate functions Multipliers are physically located next to block SelectRAM 18 x 18 Multiplier Output (36 bits) 4x4 signed ~255 MHz 8x8 signed ~210 MHz 12x12 signed ~170 MHz 18x18 signed ~140 MHz DCM Up to twelve DCMs per device Located on top and bottom edges of the die Driven by clock input pads DCMs provide: Delay-Locked Loop (DLL) Digital Frequency Synthesizer (DFS) Digital Phase Shifter (DPS) Digital Spread Spectrum (DSS) Up to four outputs of each DCM can drive onto global clock buffers All DCM outputs can drive general routing Challenges to accelerate Processing performance Very Large Single Task requires Parallel Processing Types of Challenges Multiple Tasks Multiple Solutions Parallel Processing Using Multiple Processors Parallel Processing in Hardware • High performance • lower cost • low complexity Multiple Processors on Multiple Tasks • Specific task focus • Scalable Virtex-II Pro Addresses All Processing Tasks Fabric for parallel Fabric for parallel processing in hardware processing in hardware •Uunmatched Performance •Uunmatched Flexibility Up to four 300MHz PowerPCs Up to four 300MHz PowerPCs for multiple processing for multiple processing Virtex-II Virtex-II Pro Fabric Pro Fabric Logic Capacity and Features Virtex II Pro Leads all the way Supply Voltage XC4000 and Spartan families use a 5V supply. The-XL families use 3.3 V supply. Virtex and Spartan-II use 2.5V supply. Virtex-E uses 1.8 V. Virtex-II and Virtex-IIPro uses 1.5 V Xilinx Development System XACT 1.0; 2.0 ... 6.0 Xilinx-NeoCAD Merge M 1.0 M2.0i....M5.1i THE FUTURE……. In 2005, FPGAs will be built on 70nm-Cu process; will implement 50 million system gates; with 2 billion transistors on-chip; with 10 layers of copper metal; with embedded processors running at 1 GHz clock rate; with direct interface to 10 Gbps serial data. URLs www.xilinx.com www.fpga-faq.com www.optimagic.com www.datasheetlocator.com Newsgroup comp.arch.fpga