1_Francois_Kapp

All things DBE…

Francois Kapp

Sub-system Manager: DBE

Francois.kapp@ska.ac.za

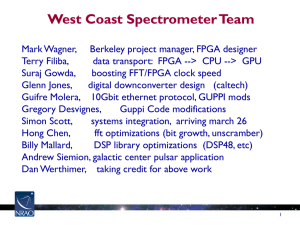

On behalf of the DBE team present and past...

S Rajan, E Bauermeister, A Rust, L Sofeya, P Gibbs, S Malan, W New, R van Rooyen, A Barta, A Martens, J

Manley, P Prozesky, V Moss, D George

What we do…

Outline

• Context

• CASPER

• HW Tools

• SW Tools

• Community

• KAT-7

• KAT-7 DBE

• MeerKAT

• MeerKAT Requirements

• MeerKAT System Architecture Aspects

• MeerKAT Cost

• MeerKAT Schedule

Context

• We are engineers…

Context

• We use acronyms like:

• PCB, FPGA, ROACH, MSSGE, PFB, ADC, DBE…

Context

• We typically add them together…

+ =

+ =

Context

• and we keep doing this…

+

=

Context

• And sometimes we use multiplication…

16 x

=

CASPER

• CASPER – Collaboration for Astronomy Signal

Processing and Electronics Research

• Started at U.C. Berkeley

• Trying to create the “PC” of RA

• Re-configurable computing

• Use low cost commodity hardware (common to many observatories)

• Develop few platforms quickly

• Upgrade often

• Accelerate the application development

CASPER Generic Architecture

ROACH

CASPER and ROACH

CASPER, ROACH and MIC?

ROACH in the future

CASPER SW/FW/GW Tools ..1

• MSSGE Toolflow

• Matlab/Simulink/System Generator/Embedded Development Kit

• But…

• Current Matlab/Simulink tool-flow is becoming unstable and is not scaling well with FPGA size -> we need a new solution

• MyHDL: Python based tool to simulate python code and convert it to Verilog or VHDL

• Designing a set of DSP libraries using combination of Verilog and MyHDL

(Python)

• Implementing a Python framework to manage design simulation and synthesis of Radio Astronomy Instruments on FPGA hardware

• Wesley New - poster

CASPER SW/FW/GW Tools ..2

• SPEAD

• Streaming Protocol for Exchange of Astronomical Data

• High “speed” data protocol

• https://casper.berkeley.edu/wiki/SPEAD

• KATCP

• A text based language for devices on the KAT network

• Now: ?request, !reply, #inform

• Future: would like to describe complex tasks in KATCP fashion

• Need:

• A way to describe tasks (statemachines)

• An Interpreter

• Sets of modules containing operations and conditions

• Meet ?sm – Adam Barta to handle a proper introduction – poster

CASPER SW/FW/GW Tools ..3

• BORPH

• Berkeley Operating system for ReProgrammable Hardware

• http://www.eee.hku.hk/~hso/borph.html

• Corr – Python library for CASPER packetised Correlators

• Linux Driver work

• Automated Gateware Discovery Using Open Firmware

• Research framework to describe FPGA designs, facilitate detection by

OS, interaction using conventional device drivers.

• Specific to KAT digital backends

• Provides an alternative approach to reduce time and effort spent on writing software for each piece of gateware generated

• Shanly Rajan – talk

CASPER Community

• https://casper.berkeley.edu/

• Workshops, mini workshops, mailing lists and friendly ghosts

KAT-7 ASC

22

Inside KAT-7 ASC

GPS Rubidium Clock

Network Switch

RFE Stage 7

DBE ROACH Board

Fibre Patch Panels

CSS Sun Servers

KAT-7 DBE

MeerKAT

MeerKAT – Phases

Phase 1

(current planning)

2016

Phase 2

Estimated completion date

Frequency bands (GHz) 1-1.75

2018

0.58 – 1.015

8-14.5

RF bandwidth (MHz)

Sampling frequency (GSPS)

Processed bandwidth (MHz)

Max baseline (km)

850

~2

850

8

6500

~15?

6500?

50?

• All current planning for phase1 – funded, well defined

• Subsequent phases not finalized, but considered in design

• Phase 2

• Added Receivers (frequency upgrade)

• Added antennae (baseline upgrade)

MeerKAT Subsystems on antenna

Antenna structures

?

Receivers

• Move the Digitisation up the signal chain and onto the Antenna (close to the feed)

• Feed selector

• Sub-arrays mean that different feeds can be selected on different antennae

• Signals transported to the KAPB digitally

• Time and Frequency References to be distributed

Digitiser

MeerKAT DBE

MeerKAT Digitiser

MeerKAT TFR

• Time and Frequency Reference Sub-system

• Distributes a Reference Clock and Synchronisation Pulse

• For phase 2:

• Must compensate for thermal and mechanical effects in fibre

• Buried 1m deep, but exposed at antenna

• Cable wrap effects

• Measure round-trip phase

• Compensate by controlling clock phase or in correlator

MeerKAT DBE Cost

MeerKAT DBE Cost ..2

MeerKAT Schedule

MeerKAT Schedule

• 2013 – Dish 1

• Start with ROACH2 based test system, prototype Digitiser

• Build up to:

• 5 (end 2014, ROACH2)

• 20 (end 2015, ROACH2)

• Full 64 (2016, ROACH3)

• ROACH3 into production – 2013

• Final Digitiser Qualification 2013

• System acceptance end 2016

• And then there’s phase 2...

• And SKA?