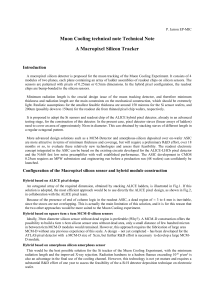

Active Pixel Sensor Circuit

advertisement

CMOS Active Pixel Sensors: An Introduction Zeynep Dilli, Neil Goldsman, Martin Peckerar, Nibir Dhar Active Pixel Sensors (adapted from El Gamal et al. and Yadid-Pecht et. al.) Active Pixel Sensor Circuit • Simple version: 3 transistors (pixel reset, source follower, access), one photodiode • Not shown: Row read circuitry, a timed buffer connected to v_out and activated a set time after pixel access Active Pixel Sensor Circuit • Operation: – Reset transistor gate pulsed, photodiode junction cap. charged up, source follower output follows – Photocurrent starts discharging, SF output follows – Access transistor gate pulsed, output cap.charged up – Bias current discharges output voltage linearly until the set read time for v_out • Operation: – Reset gate pulsed, photodiode charged up, SF output follows – i_pf discharges diode cap., SF output follows – Access gate pulsed, output cap. charged up – i_bias discharges output until the set read time for v_out Active Pixel Sensor Circuit • Design Features: – Small circuit, just three transistors per pixel: Large fill factor possible – Photodiode operation isolated from readout circuit – Flexibility in design with respect to timing design vs. power consumption vs. readout speed vs. resolution – Converts current information from photodiode to voltage information, e.g. to be read by an A/D Active Pixel Sensor Circuit • Design issues: – Transistor sizes should be as small as possible for the maximum photodiode/pixel ratio (“fill factor”) – Transistor sizes should be chosen carefully for enough current, SF gain, and isolation of SF output from the pixel output – Higher bias current: readout needs to be a smaller time after access is pulsed; timing gets tighter, reset period can be set smaller – Larger reset period: Better resolution, tighter readout timing required Active Pixel Sensor Circuit • Can model photodiode with junction cap. and ideal current source in parallel