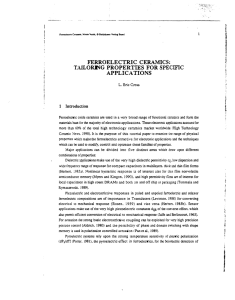

Highly reliable ferroelectric layer P(VDF-TrFE) for amorphous a-IGZO(InGaZnO) memory device Sang-yun KWON* 19-7, Yeonnam-ro 5-gil, Mapo-gu, Seoul, Republic of Korea E-mail: aenoc0410@yonsei.ac.kr 1. Introduction Amorphous In-Ga-Zn-O (a-IGZO) is being used more often as the active channel material in thin-film transistors (TFTs) because of its many benefits, which include low fabrication temperature, excellent mobility, low threshold voltage (Vth), minimal subthreshold swing (SS), and wide area uniformity.1 These exceptional properties are expected to cause a-IGZO to replace conventional amorphous Si as a channel material. However, instability under bias stress is a problem, especially for unpassivated bottom gate type TFTs. Exposure to ambient environmental conditions, moisture, absorption of oxygen and water, and post-fabrication processes that cause damage to exposed back channels can all reduce reliability.2 As we have previously shown, moisture can act as a shallow donor or induce the creation of water-related defects that function as electron traps in order to affect the negative bias thermal instability of a-IGZO TFT. We also looked into how adsorbed water affected the back channel of an unpassivated TFT and found that the thickness of the water molecules affected their capacity to donate electrons or form acceptor-like traps.3 They also showed how the adsorbed oxygen in the back channel acts as an electron acceptor, resulting in a positive Vth shift (Δ Vth).4 P(VDF-TrFE), an organic ferroelectric crystalline polymer, has garnered a lot of interest because of its lead-free advantages and ease of use. Its process limit in crystalline film thickness, which is nearly fixed at ~100 nm, is a long-standing disadvantage, nevertheless. As a result, any ferroelectric memory field-effect transistor (FeFET) based on P(VDFTrFE) has always had an operating voltage greater than 10 V. Here, Pt and Au gates are produced with creatively thinned ~20 nm P(VDF-TrFE) crystalline layers, enabling FeFETs with amorphous IGZO channels to function with a pulse of at least 3 V. After the initial formation of a 5 nm-thin crystalline seed layer, P(VDF-TrFE)-brush, spin-coating is used to create such a thin crystalline layer. The de-wetting issue of P(VDF-TrFE)-solution during spin-coating is successfully inhibited by this ultrathin P(VDF-TrFE)-brush, 1 resulting in good surface-energy matching and pinhole-free conformal coating of classical P(VDF-TrFE). Consequently, a-IGZO nonvolatile memory FETs may operate at 3–4 V pulses with no loss of leakage current. These figures can be considered among the lowest reported levels. As a ferroelectric capacitor, P(VDF-TrFE), one of the organic ferroelectric crystalline polymers, has been thoroughly researched up to this point. It is mostly utilized as a ferroelectric gate to switch channels using gate voltage pulses that exceed the coercive electric (E)-field. Specifically, the crystalline P(VDF-TrFE) polymer film is easy to work with and maintains good ferroelectric memory properties through good dipole switching. This could make it a good choice for a wide range of semiconductor channels, including organic semiconductors5, nanowires, amorphous or polycrystalline oxide6, and even twodimensional (2D) materials. In terms of remnant polarization characteristics, the organic ferroelectric layer may not be as good as well-grown inorganic layers7. However, its lead-free advantages and ease of use have garnered widespread interest. The ferroelectric P (VDF-TrFE) layer's most inescapable and long-standing disadvantage, however, is that as thickness decreases, the quality of the crystalline film decreases since films thinner than 100 nm frequently exhibit pinholes and lose their crystallinity as a result of spin-coating7. The ferroelectric switching for nonvolatile memory operation cannot be lower than ~5 V with 100 nm theoretically because its coercive electric-field (Ec) is known to be ~0.5 MV/cm. In practice, however, the record states that 8–10 V is an operation voltage to achieve effective dipole switching for the 100 nm ferroelectric polymer8. 2. First-Order Heading To investigate the properties of the semiconductor IGZO, which makes up the transistor, and the P(VDF-TrFE) ferroelectric layer, which has a high memory property. After fabrication of n-type a-IGZO memory, use probe station to manage erase-program performance measurements. 2 Figure 1. (a) (a) Producing O2 plasma etching process on rare a-IGZO substrate (b) Blue print of completely fabricated n-type a-IGZO memory device (b) 4. Experimental Section/Methods n-type memory device fabrication. — To use the SiO2-covered IGZO on the glass substrate and Si buffer layer as a contact material, dry etching with RIE in a O2 plasma environment is conducted first to expose a 10 nm thick IGZO for deposit. The source and drain electrodes are a stack of 15 nm thick Au produced via DC magnetron sputtering and shaped with the lift off technique. The IGZO damaged by etching is healed for around 30 seconds in an ozone atmosphere at 150°C. On the a-IGZO TFT, the passivation was first spin-coated for 60 seconds at 3000 rpm. To evaporate the methyl ethyl ketone (MEK, 2-butanone) solvent, prebaking was done for 60 seconds at 100°C. To cure the passivation material, the TFTs were post-baked for one hour at 150°C in an ambient atmosphere. Figure 1 shows the final passivated a-IGZO TFT structure. Finally, to enhance adhesion, Al2O3 is deposited using the ALD process at a thickness of 5 nm. The Pt top gate is designed using the lift off approach and deposited using DC magnetron sputtering deposition at a thickness of 30 nm. Every TFT was exposed to an annealing process in a glove box with N2 just for three minutes at a temperature of 200◦C. The top gate bottom contact structure will be present in the manufactured TFTs. 3 References [1] T. Kamiya, K. Nomura, and H. Hosono, Sci. Technol. Adv. Mater., 11, 044305 (2010) [2] D. H. Kang, H. Lim, C. J. Kim, I. H. Song, J. C. Park, and Y. S. Park, Appl. Phys. Lett., 90, 192101 (2007). [3] K.-H. Lee, J. S. Jung, K. S. Son, J. S. Park, T. S. Kim, R. Choi, J. K. Jeong, J.-Y. Kwon, B. Koo, and S. Lee, Appl. Phys. Lett., 95, 232106 (2009). [4] J.-S. Park, J. K. Jeong, H.-J. Chung, Y.-G. Mo, and H. D. Kim, Appl. Phys. Lett., 92, 072104 (2008). [5] R. Naber, B. De Boer, P. Blom, D. De Leeuw, Appl. Phys. Lett. 87 (2005). [6] S.M. Yoon, S. Yang, C. Byun, S.H.K. Park, D.H. Cho, S.W. Jung, O.S. Kwon, C. S. Hwang, Adv. Funct. Mater. 20 (2010) 921–926. [7] Y.Y. Choi, K. Kwak, J.W. Seo, M. Park, H. Paik, J.Y. Lee, J. Hong, K. No, J. Appl. Polym. Sci. 132 (2015). [8] S.J. Kang, I. Bae, Y.J. Shin, Y.J. Park, J. Huh, S.-M. Park, H.-C. Kim, C. Park, Nano Lett. 11 (2011) 138–144. 4