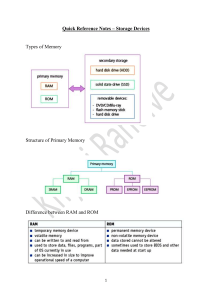

NUST College of Electrical & Mechanical Engineering Subject MICROPROCESSOR SYSTEMS Lab No. 02 Interfacing Of RAM in Proteus Name_Malaika (473129) , Mehreen Mubashir (461052) Syndicate_B Degree_45-EE Lecturer_Sir Ali Date_03/02/2025 Problem Statement Design a schematic that loads data from ROM to RAM & perform given tasks Objective ● To understand the connection of RAM with a microcontroller in a simulated environment. ● To learn about memory addressing, control signals, and data read/write operations. ● To analyze and troubleshoot RAM interfacing errors using Proteus. Introduction Interfacing Random Access Memory (RAM) with a microcontroller or processor is essential for expanding memory capacity and improving system performance. This experiment focuses on simulating RAM interfacing using Proteus, a widely used electronic design automation (EDA) software. Importance of RAM Interfacing ● RAM provides temporary storage for data and instructions during execution. ● Enhances system performance by enabling faster access to frequently used data. ● Essential for memory expansion in embedded and microcontroller-based applications. Components Required: 1. 2. 3. 4. 5. 6. 7. 74ls163 counter Logic State 27C512 ROM IS61C1024AL-12JI RAM 7SEG-BCD NOT GATE Binary Files Circuit Diagram: Procedure: ➢ Keep Counter ENP, ENT, and MR high (1). ➢ Control Load using another logic state. ➢ Connect Clock to the CLK pin and CE2 of RAM. ➢ Link the Counter output to the RAM & ROM input, grounding unused address pins (A4-A15). ➢ Connect ROM CE & OE to RAM WE, and use inverted logic of WE for RAM OE. ➢ This setup allows RAM to read from ROM when ROM is enabled; otherwise, RAM outputs stored data. ➢ RAM uses the same pins for both reading and writing. ➢ ROM loads data from a BIN file, requiring only file access in ROM. Task 01: Write 0-9, a-z,A-Z in ROM. Sol: For that we add separate bin files as shown below one by one into ROM Task 02: Move data from ROM to RAM Sol: 1) Connect output lines of ROM to input/output lines of RAM & connect CE and OE of ROM to WE of RAM and invert of WE to OE of RAM as in circuit diagram. 2) Note: Enabler pins should be considered , as they are active low logic inverts. 3) When WE of RAM is enabled , it will store data from ROM. Task 03: Display the following as output of RAM 3A at 000FH 3E at 0000H 20 at 0001H 5C at 0002H 09 at 0003H 5D at 0004H 30 at 0005H 31-39 at 0006H-000FH Sol: For this purpose make a unique bin file having data. ➢ In order to store 3A in 000FH, the counter input remains 1. ➢ Data will be written in the bin file in such a manner that it will store given codes in the required address. ➢ Now just access this bin file in ROM and RAM display output as 3A at 000FH 3E at 0000H 20 at 0001H 5C at 0002H 09 at 0003H 5D at 0004H 30 at 0005H 31-39 at 0006H-000FH Conclusion This lab demonstrated RAM interfacing in Proteus, covering memory addressing, control signals, and data operations. The simulation helped in understanding circuit design and troubleshooting, essential for embedded systems and digital electronics.