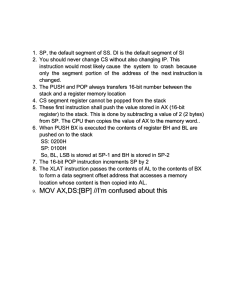

Microprocessor Programming and Interface Dr. Saad Qasim Khan Assistant Professor CIS Department NEDUET saadqasimkhan@neduet.edu.pk Special Addressing Mode • There is a special addressing mode that does not appear in Tables 4– 2, 4–3, or 4–4. It occurs whenever memory data are referenced by only the displacement mode of addressing for 16-bit instructions. • Examples are the MOV [1000H],DL and MOV NUMB,DL instructions. • The first instruction moves the contents of register DL into data segment memory location 1000H. • The second instruction moves register DL into symbolic data segment memory location NUMB. Lecture 11 2 Special Addressing Mode • Whenever an instruction has only a displacement, the MOD field is always a 00 and the R/M field is always 110. • As shown in the tables, the instruction contains no displacement and uses addressing mode [BP]. • You cannot actually use addressing mode [BP] without a displacement in machine language. • The assembler takes care of this by using an 8-bit displacement (MOD=01) of 00H whenever the [BP] addressing mode appears in an instruction. This means that the [BP] addressing mode assembles as a [BP+0], even though a [BP] is used in the instruction. Lecture 11 3 Lecture 11 4 Lecture 11 5 Segment MOV Instructions • If the contents of a segment register are moved by the MOV, PUSH, or POP instructions, a special set of register bits (REG field) selects the segment register. Lecture 11 6 Lecture 11 7 PUSH/POP • The PUSH and POP instructions are important instructions that store and retrieve data from the LIFO (last-in, first-out) stack memory. • The microprocessor has six forms of the PUSH and POP instructions: register, memory, immediate, segment register, flags, and all registers. • The PUSH and POP immediate and the PUSHA and POPA (all registers) forms are not available in the earlier 8086/8088 microprocessors, but are available to the 80286 through the Core2. Lecture 11 8 Lecture 11 9 PUSH Instruction Lecture 11 10 Lecture 11 11 POP Instruction Lecture 11 12 LOAD-EFFECTIVE ADDRESS • There are several load-effective address instructions in the microprocessor instruction set. • The LEA instruction loads any 16-bit register with the offset address, as determined by the addressing mode selected for the instruction. • The LDS and LES variations load any 16-bit register with the offset address retrieved from a memory location, and then load either DS or ES with a segment address retrieved from memory. Lecture 11 13 LEA • The LEA instruction loads a 16- or 32-bit register with the offset address of the data specified by the operand. • By comparing LEA with MOV, we observe that LEA BX,[DI] loads the offset address specified by [DI] (contents of DI) into the BX register; MOV BX,[DI] loads the data stored at the memory location addressed by [DI] into register BX. Lecture 11 14 Example Lecture 11 15 LEA / LDS / LES Lecture 11 16 Lecture 11 17 The End Lecture 11 18