8085 Microprocessor: Architecture, Organization, and Instructions

advertisement

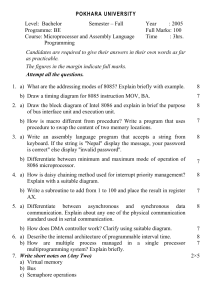

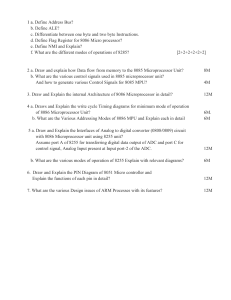

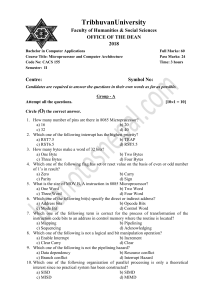

BSc Part III (H) / CC-10H Microprocessor Chapter 1 8085 microprocessor: Architecture and Organization 1. Introduction Features of 8085 8085 was developed by INTEL corporation in 1976. 8085 is an 8-bit processor. It has 8-bit data line and 16-bit address line. It works with 5V, 1A DC. It is made by NMOS technology. It works on the principle of Von Neumann Architecture. It is a 40 pin IC. Software and Programs Softwares are some set of programs designated to do a specific task or some multiple tasks. A program is a part of software that does a specific mathematical operation. A program is a set of instructions. The instructions are written using some protocols called language; it may be written in low or high level languages. Language and Translators Machine Level Language Computer hardware understands only the presence or absence of electricity. So the instructions given to the computer in 1s and 0s are called Machine Level Language. The advantages and disadvantages of such language are stated as follows. Advantage of Machine Level Language Memory requirement is less, since it is written only in 1s and 0s. Disadvantages of Machine Level Language It is written by 1s and 0s only so coding programs using that is very difficult, programs are very long. The programs are difficult to debug or detect errors. Looping cannot be done easily. Programs are highly dependent on circuit protocols, so they are not portable. Complex codes can not be written. Assembly Level Language With time it was observed that the computer applications were ever increasing and a better, reliable method of programming was highly necessary so that the problem of Machine Level Language was overcome. The programs written on ‘Alpha-Numeric’ syntaxes are called Assembly Level Language. The advantages and disadvantages of such language are stated as follows. Advantages of Assembly Level Language Programs are easy to write. Programs are easy to debug and detect errors. Looping can be done easily. Disadvantage of Assembly Level Language Complex codes can not be written. Modular programs cannot be done. Size of ALPs are large. High Level Language The programs written in English-like syntaxes are called high level language. Examples: C, C++, JAVA, Python, C#, R, Pearl, BASIC, PASCAL, COBOL, etc. Advantages of High Level Language Error detection and debugging are easy. Programs are easy, compact to write Programs are not dependent on circuit protocols, so they are portable. Disadvantages of High Level Language Memory size is large Programmers must be trained. Translators The system software within the computer that converts user/programmer understandable language to binary notations is called translator. Assembler: This module translates Assembly Level Language to Machine Level LAnguage. Compiler: Compiler is a module that reads high level language line by line, and detects error (if any) and converts to machine understandable format. Interpreter: Interpreter is a module that reads high level language all at once; detects error at the end, converts to binary format. It is faster than the compiler. 2. 8085 Architecture and Organization Computer Organization deals with the way that various hardware components are connected together to form a computer system. Computer Architecture is concerned with the structure and behavior of the computer as viewed from the programmer's perspective. A programmer must aware of the machine codes what a particular machine is capable of doing. (i) Functional Block Diagram of 8085 (ii) ALU: The circuit that solves all the arithmetic and logical operations within the CPU is called the arithmetic and logic unit. The ALU of 8085 can perform - addition, subtraction, increment, decrement, logical bit wise shift, bitwise AND, OR, NOT, XOR. (iii) General Purpose Register: A register is a sequential digital circuit, formed by flip flops to store data temporarily. The general purpose register of 8085 are of 8bit size, they are used by the programmers to load variables or data to execute any task. The general purpose registers of 8085 are B, C, D, E, H and L. In order to deal with 16 bit data, in 8085 there was a provision of using register pairs. The pairs are BC, DE and HL. the HL pair serves as one input of ALU, that means the result after any 16 bit operation goes to the HL pair. (iv) Stack and Stack pointer Stack is a special part of the memory where users or programmers can load data temporarily. Stack works on the principle of LIFO (Last in first out). The stack pointer is a 16bit register that holds the address of the topmost item of stack. (v) Accumulator It is a special 8-bit register that serves as one input of the ALU. That is, while executing any arithmetic or logical operation it deals with the content of the accumulator and the result goes to the accumulator. Example: to execute ADD B; this means the content of B register is added with the content of Accumulator, the result goes in the accumulator. (vi) Instruction Register At first the program or the instructions are written in the RAM (primary memory) from there the instructions are fetched to the CPU and the CPU decodes the instructions to do the necessary job. The instruction register basically stores the meaningful data for a particular instruction. (vii) Program Counter It is a special 16-bit register that holds the memory address for the next instruction to be executed. Say the processor is executing a program as follows Memory address opcode 2000H 06H 2001H 15H The time, when 06 is executing, then the PC loads the next instruction’s address i.e. address of 15H (2001H). (viii) Timing and Control Unit CPU has got a module called timing and control unit, which sends the control signals to the ALU so that it works accordingly. The signal is dependent on the instruction given. (ix) System Bus The metallic conductors used to connect different modules of a computer are called bus. System bus means data bus, address bus and control bus. Data bus loads the data while data transfer takes place from memory to register/CPU or between registers, peripherals to CPU. Address bus loads the memory address while any flow of data. Control bus allows the flow of control signals from timing and control unit to ALU. (x) Flag Flags are nothing but some flip flops that may be set or reset depending on certain situations. 8085 has got 5 flags. D7 D6 D5 D4 D3 D2 D1 D0 S Z x AC x P x CS ● ● ● ● ● Carry Status Flag: After any arithmetic or logical operation, if the result has got a carry (or overflow) then the carry flag is set to 1, else it remains 0. Parity Fag:After any arithmetic or logical operation, if the result has got even number of 0s then parity flag is set to 1, else it remains 0. Auxiliary Carry Flag: After any arithmetic or logical operation,if a carry is generated in the 4th bit, then the auxiliary carry flag is set to 1, else it remains 0. Zero Flag: After any arithmetic or logical operation, if the result becomes 0, then Zero flag is set to 1, else it remains 0. Sign Flag: After any arithmetic or logical operation, if the result is negative then sign flag is set to 1, else it remains 0. When all the 5 flags are viewed together as a 8bit word, it is called PSW or Program Status Word. the content of the accumulator and the PSW together can be used in stack operations. (xi) Temporary Register It is a special 8bit register, used by the ALU while doing any operation, this register is not accessible to the user. 3. Instruction Sets An instruction is a command given to the computer to perform a specific operation. In 8 8085 microprocessor we have 8 data lines so a total of 2 instructions can be formed. These instructions can be classified into 5 major branches. They are explained as follows: ● Data Transfer Group: the instructions that are used to transfer the data from one register to the other or register to any memory or vice versa is called Data Transfer Group of instructions. Here the content of any flag remains unaffected. Examples: MOV B,C this means the data from C register is transferred to B register and the previous data is not lost. MVI B, 09H this means the data 09H is moved immediately to the register B. STA 8050H this means the data from the accumulator is stored in the memory location 8050H. LDA 8051H this means the data from 8051H location is loaded into the accumulator. Q. Write an ALP to take two data from the user and swap them. Say the user has given the first data in 8050H location and the next data in 8051H location. We need to swap it. Assembly Level Program Algorithm Comments Program Load accumulator with the data in 8050H location Acc has 1st number LDA 8050H Move the data from accumulator to register B B gets the 1st number MOV B,A Load accumulator with the data in 8051H location Acc has the 2nd number LDA 8051H Store the accumulator content in 8050H 8050H holds 2nd number STA 8050H Copy the content of B into Accumulator Acc has the 1st data MOV A,B Store the accumulator content in 8051H 8051H holds 1st number STA 8051H begin end HLT Result: Input Output Memory Address Data Memory Address Data 8050H 05H 8050H 09H 8051H 09H 8051H 05H ● Arithmetic Group: the instruction that is used to perform any arithmetic operations like addition or subtraction or increment/decrement is called Arithmetic Group of instruction. Here the content of flags may change. Examples: INR B this means the content of B register is incremented by 1. ADD C this means the content of C register is added with the accumulator and the result is in the accumulator. Q. Write an ALP to add two 8bit numbers given by the user, store the result in some location. Say the user gives two numbers in 8050H and 8051H respectively, the sum will be stored in 8052H location. Assembly Level Program Algorithm Comments Program Load the first number from 8050H location to accumulator Acc has the 1st number LDA 8050H Move the data from the accumulator to register B B register gets 1st number MOV B,A Load the second number from 8051H location to accumulator Acc has the 2nd number LDA 8051H Add the content of accumulator with the content of B register, result in accumulator A= A+B ADD B Store the content of accumulator (sum) in memory address 8052H 8052H location holds the sum STA 8052H begin end HLT Result: Input Output Memory Address Data Memory Address Data 8050H 05H 8052H 0EH 8051H 09H ● ● ● Logical Group: the instruction by which the microprocessor can perform logical operations like AND,OR,NOT,XOR, Shift are called logical group of instruction. Branch Controlled Group The instruction that deals with looping or jumping. Eg conditional and unconditional jump. Machine Controlled Group The instruction used to perform machine operations like HLT or any interruption. 4. Addressing modes The method or the conventions used to identify or address any instruction are called addressing mode. The addressing mode of 8085 are as follows: ● Immediate addressing: The operand (or the data on which the task has to be executed) is mentioned in the instruction. Eg: MVI B, 09H This means the operand 09H is already mentioned within the instruction MVI B Eg: ADI 05H - add 05H immediately with acc Eg: ANI 06H - and 06H immediately with acc ● ● Direct addressing The set of instructions that deals with the address directly Eg: LDA 2050 This means the data of 2050 goes into acc directly. Register direct addressing The instructions where the microprocessor deals with registers and the operand is mentioned within the registers. Eg: MOV B, C - this means the data of C register is transferred to B register, and the data within C register is the operand that directly gets transferred. ● Indirect addressing Here the data doesn't get manipulated directly. The address is specified and the operation takes place with the data of the address. In other words if we implement LXI H, 2050H - this means 20H and 50H are loaded into H and L registers respectively. If we execute MOV A,M after that means the data within the address specified in HL pair goes to acc. In order to perform loop operations or array programs indirect addressing takes less time and space instead of direct. ● Implicit addressing There are certain instructions with only 1byte data. There is no operand. Eg: XCHG - the data in HL and DE gets exchanged ● Explicit addressing It is basically the instruction that are responsible for jump or stop. 5. Use of subroutine and stack ● Subroutines It is often observed that doing large programs is difficult to understand as well as to debug. So a large program is divided into some subdivisions. Such sub-divisions are capable of doing a particular work only and they are written from specific locations. The subdivisions are basically linked with the main program. These subdivisions are basically subroutines. They are just like function calling concepts. Memory address Mnemonics Operands 2000H --------- -------- 2001H -------- -------- 2005H CALL 2050H 2006H ----- ---- 2007H HLT Comments 2002H 2003H 2004H Program control goes to the 2050H location SUBROUTINE 2050 ---- ----- 2051 ---- ----- 2052 RET The last value is returned to the main program By using the CALL instruction, the Program Counter gets the control of the subroutine and execution of subroutine gets started; when RET is executed it gets back to the main program. ● Stack Stack is a special part in the main memory of the computer. It is allocated at last of the memory space. If general purpose registers are all in use in that case stack could be used as a temporary data storage location. Stack uses the concept of LIFO (last in- first out) the register used to point the address of the topmost stack is called SP (stack pointer) Chapter 2 Communication with 8085 1. Programs 2. Address and data bus The word BUS comes from a greek word meaning highway or any transportation medium. The internal parts of the computer must be connected so that data can get transferred. The memory, IO and CPU are connected by such buses. The bus is basically a set of conducting wires through which information gets transferred parallely. Data Bus: through this data or opcode gets transferred. In 8085 there are 8 data bus Address Bus: through this the address gets transferred. In 8085 there are 16 address lines. Control Bus: through this the timing and control signals pass from the control unit. The set of these three bus are called system bus. The number of address line = 16; each cell has 8 bit information. 16 So we can address 2 such cells each of 8bit (1byte) 6^ 10 = 2 x 2 bytes = 64 x 1024 bytes = 64 kB Including RAM and ROM as well as other peripherals 8085 has 64KB of memory space. 3. Control signals Some special output pins are there in 8085; they are RD’, WR’, IO/M’ When the microprocessor is reading something from the memory or IO device then RD’ = 0 else it is 1 When the microprocessor is writing something on the memory or IO device then WR’ = 0 else it is 1 When the microprocessor is accessing the memory part then IO/M’ = 0 When the microprocessor is accessing the IO part then IO/M’ = 1 8085 has got 4 control signals generated by the above mentioned special output pins. They are MEMR, MEMW, IOR, IOW. Outputs from 8085 Control Signals RD’ WR’ IO/M’ MEMR’ MEMW’ IOR’ IOW’ COMMENT 0 1 0 0 1 1 1 Microprocessor reads data or opcode from memory 1 0 0 1 0 1 1 Microprocessor writes data or opcode into memory 0 1 1 1 1 0 1 Microprocessor reads data or opcode from IO device 1 0 1 1 1 1 0 Microprocessor writes data or opcode into IO devices ● Memory read operation is done when IO/M’ = 0 and RD’ = 0; if any one of them is 1; MEMR’ = 1 ● ● ● So OR gate is used That is RD’ and IO/M’ is passed through OR gate. Memory write operation is done when IO/M’ = 0 and WR’ = 0; if any one of them is 1; MEMW’ = 1 So OR gate is used That is WR’ and IO/M’ is passed through OR gate. IO read operation is done when IO/M’ = 1 and RD’ = 0 So IO/M’ is complemented and OR gate is used That is RD’ and complement of IO/M’ is passed through OR gate. IO write operation is done when IO/M’ = 1 and WR’ = 0 So IO/M’ is complemented and OR gate is used That is WR’ and complement of IO/M’ is passed through OR gate. *Bubbled NAND means OR gate 4. Status signals The pins s1 and s0 are the status pins of 8085. The information from these two output pins specifies the status of 8085. Q: How can a microprocessor distinguish between opcode and data? Let us consider MVI B, 06H. Here opcode of MVI B is 06 as well as the data is also 06. The microprocessor can distinguish between the two based on the status signals. When is is executing MVI B, s1 and s0 are 11 this means opcode is fetched. When the data comes it becomes 01. 5. Demultiplexing of AD bus 8085 has got 16 address lines (A0-A15) so that 64kB can be addressed. Out of the 16 bit address the lower 8-bit is dual purpose. That is AD0-AD7 behaves both as a lower address and data line. This is called demultiplexing of AD bus. ★ Role of ALE ALE is a special pin of 8085, it goes high (1) during the first clock of the machine cycle. It remains low (0) during the remaining part of the machine cycle. ALE means the address latch enable. When ALE=1 the lower 8-bit of the AD bus behaves as address line When ALE=0 the lower 8-bit of AD bus behaves as data lines. ★ Need for AD bus demultiplexing (i) cost - if the AD bus is dual purposed, the cost of the microprocessor is reduced (ii) power consumption - smaller the IC size or less the number of pins the power consumption is less. ★ How demultiplexing is done The D-Latch shown has 8-units of D flip-flops. The ALE is connected to the clock of all the D flip-flops. When the clock of D flip flop is 1 (ALE=1) the inputs given to the D line will go to the next state output. When ALE=1 the AD bus hence works as address line. Else the AD bus is bypassed as a data-line. 6. Instruction cycle The programs or the instructions are written on the primary memory. The microprocessor fetches each and every instructions line-by-line, then it decodes it finally executes it. The steps carried out by the CPU process a particular instruction is called instruction cycle. It is classified into two parts: ● Fetch cycle - the steps carried out by the CPU to fetch an instruction from the memory to the processor is called fetch cycle. It is the 1st machine cycle of any instruction processing. An instruction is of two parts, the first part is the opcode ● and then we have data. When the opcode is fetched from the memory it goes to the instruction register via the data bus. When the data bus is active ALE=0. Execution cycle - The steps carried out by the CPU to decode then execute any fetched instruction is called execution cycle. It is the second machine cycle of any instruction. When the fetched instruction (opcode) comes into the instruction register it gets decoded by the instruction decoder. The decoder decodes the instruction and sends some control signal to the ALU. the ALU gets the data through the data bus and the ALU hence performs the specified task and stores the result in the accumulator. In other words; IC = FC + EC 7. Machine cycle The steps carried out by the CPU to perform any specific operation like opcode or data fetch or decode or execute is called machine cycle. FC or EC are types of machine cycle. During the 1st clock of the machine cycle the ALE=1 and AD bus sends a lower 8-bit address, else ALE=0 AD bus transmits data. 8. T-State It is basically a clock pulse. For each machine cycle 3T states are needed that means 3 clock pulses are needed for each MC. But for fetching (FC) 3 T states are there for normal operation. Also an extra clock pulse is needed since the memory and the CPU may not match at the same speed. So a total of 4T states are there in FC. The extra T state is called wait cycle. 9. Timing diagram It is the pictorial way of understanding any instruction and its working. It has got the voltage levels for some significant pins of 8085. It explains all the individual machine cycles responsible for execution of a particular instruction. Refer: Timing diagram of MVI instruction - GeeksforGeeks Explain the timing diagram for MVI B, 56H Memory Address Mnemonics Operands Opcodes Comments 2050H MVI B 45H 06H 45H is loaded into register B immediately 2051H 2050H - 06H (opcode) 2051H - 45H (data) 45H Chapter 3 DATA TRANSFER SCHEMES https://1drv.ms/p/s!BOcHv-v779ZDkgaSk1sAAkDB7FXW?e=o22AiO Chapter 4 Memory Mapping and interfacing 8085 can be used to address 64kB memory. The 16 address lines are connected via some decoding circuits to the memory. The address lines may also be connected to some io device also. Some addresses will be designated to deal with io devices as well. Interfacing means connecting the 8085 IC with some other peripherals (input/output or memory) The interfacing can be done by two ways. The ways are basically mapping. 1. IO mapped IO - same address can be used for both IO and memory device. IO/M’ is used to distinguish them. When IO/M’=1 it uses IO devices else it uses memory devices. Here it is applicable for large computers. 2. Memory-mapped IO - some addresses are specified for memory and some for IO. it is valid for small systems. The addresses are like memory devices. Say 0000-6000 means IO rest means memory. IO devices are accessed like memory. Chapter 5 PPI 8255 8255 is a programmable peripheral interface IC that is used along with 8085 to connect IO devices. Features of 8255 1. It is a 40 pin IC that uses 5V 2. It is made in NMOS logic 3. It has 3 ports port A, B and C each 8bit 4. It has 3 modes 0, 1 and 2 5. 8 common data lines purpose No of pin Data line 8 Port A 8 Port B 8 Port C upper 4 Port C lower 4 Power (Vcc) 1 Power (Gnd) 1 RD’ 1 WR’ 1 Address line 2 S1 s0 2 Modes of 8255 8255 uses three modes 1. Mode 0: it is a simple I/O mode, it can use all three ports (PA, PB or PC) as both input or output port. 2. Mode 1: it is a strobed I/O mode, port C acts as the strobe (enable line) based on the content of port C (PC3, PC6, PC7) it can use port A or B input or output. 3. Mode 2: it is a strobed bidirectional mode that acts as the combination of mode 0 or 1. Ports of 8255 1. Port A - 8 bit (I/O) Can work in mode 0, 1 and 2 2. Port B - 8bit (I/O) Can work in mode 0 and 1 3. Port C -(I/O/Strobe) 3.1. Port C upper - 4bit 3.2. Port C lower - 4bit Can work only in mode 0 Control word of 8255 It is an 8bit word, given by the programmer to the 8085 so that it can understand what port of 8255 to use and in what mode. 7 6 5 BSR or 8255 (0 for BSR) Mode selection of port A (mode 0=00, mode 1=01, mode 2=10) 4 3 2 1 0 Port A 1 = input 0= output Port C (upper) 1 = input 0= output Mode of port B (0 or 1) Port B 1 = input 0= output Port C (lower) 1 = input 0= output Q. Make the control word of 8255 such that Port A - output Port B-output Port C (upper)-input Port C (lower) - output 7 1 6 0 5 4 3 2 1 0 0 0 1 0 0 1 So the CW of 8255 is 1000 1001 = 89H Q. Make the control word of 8255 such that Port A - input Mode - 1 Port B - output Port C upper - input Port C lower - strobe 7 6 1 0 5 4 3 2 1 0 1 1 1 1 0 0 or 1 So the CW of 8255 is BCH or BDH. BSR Mode BSR stands for Bit-Set-Reset. It sets or resets only the particular pin of the port C. the BSR bit pattern is as follows: 7 BSR or 8255 BSR=0 8255=1 6 x 5 4 3 2 x x Bit pattern of port c 1 0 1=set 0=reset Design a square wave using microprocessor In this problem we use a particular pin of port C as output. For some time the pin will remain set, for some time it will remain reset. To initialize the 8255 IC, at first we need to inform the microprocessor to use 8255 as mode 0, port c (output) . For that a CW has to be given to the accumulator. Here the CW is 7 6 5 4 3 2 1 0 1 0 0 0 0 0 0 0 CW = 80H This has to be given to the accumulator. Say we use the pin 1 of port C for set or reset BSR to set pin 1 of port C 7 6 0 0 5 4 3 2 1 0 0 0 0 0 1 1 5 4 3 2 1 0 0 0 0 0 1 0 So the BSR word is 03H. BSR to reset pin 1 of port C 7 0 6 0 So the BSR word is 02H Main Program LABELS GO: CODE COMMENT MVI A,80H The control word is loaded to the acc. OUT CWR 80h is transferred to the control word register so that the microprocessor can understand what mode or port to use MVI A, 03H Port PC1 is set CALL DELAY A delay program is called so that 8255 can transfer 1 for some amount of time MVI A, 02H Port PC1 is reset CALL DELAY A delay program is called so that 8255 can transfer 0 for some amount of time JMP GO The set and reset of pc1 is made into an infinite loop Delay Program LABELS L1 CODE COMMENT MVI B, FF FF is loaded in B register DCR B B is decremented JNZ L1 Loop continues till B = 0 RET Returns to the main program after spending some time. . Interrupt of 8085 What is interrupt? (1) When a microprocessor is executing a current task, and if some instruction or voltage trigger is given externally to disturb the ongoing work, such an external disturbance is called an interrupt. Why interrupts are important? (2) During the early 70s, the microprocessors were not equipped with a provision of multi core and not even pipelining so to deal with multitasking, interrupts were used. When a processor is interrupted it pauses its ongoing work and can do another work provided by the interrupt. What are the types of interrupts? (4) Interrupts are mainly classified into two types: 1. Hardware interrupt: If the interruption is done by any voltage pulse such an interrupt is called hardware interrupt. It is classified into: 1.1. Maskable: the hardware interrupt that can be enabled or disabled by the programmer is called maskable interrupt. Eg: RST 7.5, RST 6.5, RST 5.5 1.2. Non Maskable: the hardware interrupt that cannot be enabled or disabled by the programmer is called nonmaskable interrupt. They are always in an active state. Eg: TRAP and INTR 2. Software interrupt: If a programmer writes some code and for that the main program gets interrupted such commands are software interrupts. Eg: RST 0, RST 1, .. 8 3. Vectored The interrupts having a call location are called vectored interrupts. Eg: RST 7.5, RST 6.5, RST 5.5. 4. Non Vectored The interrupts having no call location are called non-vectored interrupts. Eg: TRAP Describe how interrupt works. (5) Define SIM and RIM What is the priority of interrupt? TRAP>RST 7.5>RST 6.5>RST 5.5>INTR What is a pending interrupt?