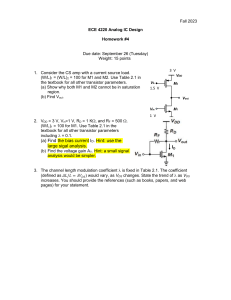

DC Characteristics of a CMOS Inverter • • A complementary CMOS inverter consists of a p-type and an n-type device connected in series. The DC transfer characteristics of the inverter are a function of the output voltage (Vout) with respect to the input voltage (Vin). • The MOS device first order Shockley equations describing the transistors in cut-off, linear and saturation modes can be used to generate the transfer characteristics of a CMOS inverter. • Plotting these equations for both the n- and p-type devices produces voltagecurrent characteristics shown below. IV Curves for nMOS PMOS IV Curves DC Response • • DC Response: Vout vs. Vin for a gate Ex: Inverter – When Vin = 0 -> Vout = VDD – When Vin = VDD -> Vout = 0 – In between, Vout depends on transistor size and current – By KCL, we that Vin Idsn = |Idsp| – We could solve equations – But graphical solution gives more insight VDD Idsp Idsn Vout Transistor Operation • • Current depends on region of transistor behavior For what Vin and Vout are nMOS and pMOS in – Cutoff? – Linear? – Saturation? nMOS Operation Cutoff Vgsn < Linear Vgsn > Saturated Vgsn > Vdsn < Vdsn > VDD Vin Idsp Idsn Vout nMOS Operation Cutoff Vgsn < Vtn Linear Vgsn > Vtn Saturated Vgsn > Vtn Vdsn < Vgsn – Vtn V > V – V dsn gsn tn VDD Vin Idsp Idsn Vout nMOS Operation Cutoff Linear Saturated Vgsn < Vtn Vgsn > Vtn Vgsn > Vtn Vdsn < Vgsn – Vtn V > V – V dsn gsn tn VDD Vgsn = Vin Vdsn = Vout Vin Idsp Idsn Vout nMOS Operation Cutoff Vgsn < Vtn Vin < Vtn Linear Vgsn > Vtn Vin > Vtn Vdsn < Vgsn – Vtn Vout < Vin - Vtn Saturated Vgsn > Vtn Vin > Vtn Vdsn > Vgsn – Vtn Vout > Vin - Vtn VDD Vgsn = Vin Vdsn = Vout Vin Idsp Idsn Vout pMOS Operation Cutoff Vgsp > Linear Vgsp < Saturated Vgsp < Vdsp > Vdsp < VDD Vin Idsp Idsn Vout pMOS Operation Cutoff Vgsp > Vtp Linear Vgsp < Vtp Saturated Vgsp < Vtp Vdsp > Vgsp – Vtp Vdsp < Vgsp – Vtp VDD Vin Idsp Idsn Vout pMOS Operation Cutoff Vgsp > Vtp Linear Vgsp < Vtp Saturated Vgsp < Vtp Vdsp > Vgsp – Vtp Vdsp < Vgsp – Vtp VDD Vgsp = Vin - VDD Vdsp = Vout - VDD Vtp < 0 Vin Idsp Idsn Vout pMOS Operation Cutoff Vgsp > Vtp Vin > VDD + Vtp Linear Vgsp < Vtp Vin < VDD + Vtp Vdsp > Vgsp – Vtp Vout > Vin - Vtp Saturated Vgsp < Vtp Vin < VDD + Vtp Vdsp < Vgsp – Vtp Vout < Vin - Vtp VDD Vgsp = Vin - VDD Vdsp = Vout - VDD Vtp < 0 Vin Idsp Idsn Vout I-V Characteristics • Make pMOS wider than nMOS such that bn = bp Vgsn5 Vgsn4 Idsn Vgsn3 -Vdsp Vgsp1 Vgsp2 -VDD 0 VDD Vdsn Vgsp3 Vgsp4 Vgsp5 -Idsp Vgsn2 Vgsn1 Current vs. Vout, Vin Idsn, |Idsp| Vin0 Vin5 Vin1 Vin4 Vin2 Vin3 Vin3 Vin4 Vin2 Vin1 Vout VDD Load Line Analysis • For a given Vin: – Plot Idsn, Idsp vs. Vout – Vout must be where |currents| are equal. Idsn, |Idsp| Vin0 Vin5 Vin1 Vin4 Vin2 Vin3 Vin3 Vin4 Vin2 Vin Vin1 Vout VDD VDD Idsp Idsn Vout Load Line Analysis • Vin = 0 Vin0 Idsn, |Idsp| Vin0 Vout VDD Load Line Analysis • Vin = 0.2VDD Idsn, |Idsp| Vin1 Vin1 Vout VDD Load Line Analysis • Vin = 0.4VDD Idsn, |Idsp| Vin2 Vin2 Vout VDD Load Line Analysis • Vin = 0.6VDD Idsn, |Idsp| Vin3 Vin3 Vout VDD Load Line Analysis • Vin = 0.8VDD Vin4 Idsn, |Idsp| Vin4 Vout VDD Load Line Analysis • Vin = VDD Vin0 Idsn, |Idsp| Vin5 Vin1 Vin2 Vin3 Vin4 Vout VDD Load Line Summary Idsn, |Idsp| Vin0 Vin5 Vin1 Vin4 Vin2 Vin3 Vin3 Vin4 Vin2 Vin1 Vout VDD DC Transfer Curve • Transcribe points onto Vin vs. Vout plot Vin0 Vin5 Vin1 Vin4 Vin2 Vin3 Vin3 Vin4 Vin2 Vin1 Vout VDD VDD A B Vout C D 0 Vtn VDD/2 Vin E VDD+Vtp VDD Operating Regions • Revisit transistor operating regions Region nMOS A B C D E pMOS VDD A B Vout C D 0 Vtn VDD/2 Vin E VDD+Vtp VDD Operating Regions • Revisit transistor operating regions Region nMOS pMOS A Cutoff Linear B Saturation Linear C Saturation Saturation D Linear Saturation E Linear Cutoff VDD A B Vout C D 0 Vtn VDD/2 Vin E VDD+Vtp VDD Beta Ratio • • • If bp / bn 1, switching point will move from VDD/2 Called skewed gate Other gates: collapse into equivalent inverter VDD bp 10 bn Vout 2 1 0.5 bp 0.1 bn 0 Vin VDD DC Characteristics of a CMOS Inveter • • • • The DC transfer characteristic curve is determined by plotting the common points of Vgs intersection after taking the absolute value of the p-device IV curves, reflecting them about the xaxis and superimposing them on the n-device IV curves. We basically solve for Vin(n-type) = Vin(p-type) and Ids(n-type)=Ids(p-type) The desired switching point must be designed to be 50 % of magnitude of the supply voltage i.e. VDD/2. Analysis of the superimposed n-type and p-type IV curves results in five regions in which the inverter operates. • Region A occurs when 0 leqVin leq Vt(n-type). – – – – • The n-device is in cut-off (Idsn =0). p-device is in linear region, Idsn = 0 therefore -Idsp = 0 Vdsp = Vout – VDD, but Vdsp =0 leading to an output of Vout = VDD. Region B occurs when the condition Vtn leq Vin le VDD/2 is met. – Here p-device is in its non-saturated region Vds neq 0. – n-device is in saturation • Saturation current Idsn is obtained by setting Vgs = Vin resulting in the equation: I dsn bn 2 Vun Vtn 2 CMOS Inverter DC Characteristics CMOS Inverter Transfer Characteristics • In region B Idsp is governed by voltages Vgs and Vds described by: V gs Vin VDD and Vds Vout VDD V VDD I dsp b p Vin VDD Vtp Vout VDD out 2 2 Recall that : I dsn I dsp • bn 2 Vin Vtn 2 b p Vin VDD Vtp Vout VDD Vout VDD 2 2 • Region D is defined by the inequality VDD Vin VDD Vtp 2 • p-device is in saturation while ndevice is in its non-saturation region. bp Vin VDD Vtp 2 ; Vin Vtp VDD I dsp 2 AND Region C has that both n- and p2 devices are in saturation. Vout I dsn b n Vin Vtn Vout ; Vin Vtn • Saturation currents for the two 2 devices are: • Equating the drain currents allows us bp to solve for Vout. (See supplemental Vin VDD Vtp 2 ; Vin Vtp VDD I dsp 2 notes for algebraic manipulations). AND b 2 I dsn n Vin Vtn ; Vin Vtn 2 CMOS Inverter Static Charateristics • • • • In Region E the input condition satisfies: • Vin VDD Vtp VD The p-type device is in cut-off: Idsp=0 The n-type device is in linear mode Vgsp = Vin –VDD and this is a more positive value compared to Vtp. Vout = 0 nMOS & pMOS Operating points A Vout =Vin-Vtp B D Output Voltage • Vout =Vin-Vtn Both in sat nMOS in sat pMOS in sat C D 0 Vtp Vtn E VDD/2 VDD+Vt VD p D