Electronics I Assignment: Transistor Amplifiers & MOSFET Biasing

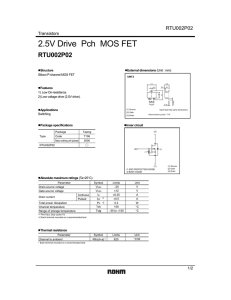

advertisement

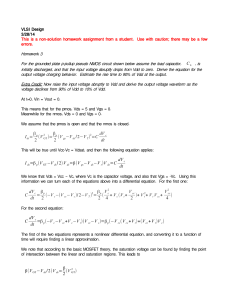

by applying a dc voltage3 VGS , and the input signal to be am the dc bias voltage VGS . The output voltage is taken at the dr The DC Bias Point The dc bias current ID can be found thus, College of Engineering | Department of Electrical Engineering ELE 241: Electronics I Spring 2024 Assignment 5 Due Date: 12th May 2024 1 1 2 2 ID = kn (VGS − Vt ) = kn VO 2 2 where we have neglected channel-length modulation (i.e., VOV = VGS − Vt is the overdrive voltage at which the MOSF voltage at the drain, VDS , will be (Before 11:59 pm, submit online) VDS = VDD − RD ID To ensure saturation-region operation, we must have VDS > VOV Note: Please use the cover sheet provided on iLearn and staple it with the assignment papers Furthermore, since the total voltage at the drain will have a together. on VDS , VDS has to be sufficiently greater than VOV to allow swing. 1. (6.23 in 7th ed.) VDD iD RD vDS vgs " ! VGS " vGS Figure 7.10 Conceptual c the MOSFET as a small-si ! Fig. 7.10 3 Practical biasing arrangements will be studied in Section 7.4. 2. (6.24 in 7th ed.) Reference: Questions are taken from “Microelectronic Circuits” 7th Ed, Sedra & Smith. 1 College of Engineering | Department of Electrical Engineering 3. (6.59 in 7th ed.) 4. (6.92) 460 Chapter 7 Transistor Amplifiers VDD RD 0 ID RG ID ! VDS ! VGS " " Figure 7.50 Biasing the MO resistance, RG . Fig.7.50 Biasing Using a Drain-to-Gate Feedback Res circuit biasing arrangement utilizing a feedback resi gate is shown in Fig. 7.50. Here the large feedback range) forces the dc voltage at the gate to be equal to we can write VGS = VDS = VDD − which can be rewritten in the form VDD = VGS + RD which is identical in form to Eq. (7.137), which des discussed above [that in Fig. 7.48(a)]. Thus, here t increases, then Eq. (7.140) indicates that VGS must causes a decrease in ID , a change that is opposite in Thus the negative feedback or degeneration provide constant as possible. The circuit of Fig. 7.50 can be utilized as an amplif the gate via a coupling capacitor so as not to disturb th The amplified output signal at the drain can be cou via a capacitor. We considered such an amplifier cir EXERCISE Reference: D7.33 Design the circuit in Fig. 7.50 to operate 2at a dc drain curre Questions are taken from “Microelectronic Circuits” 7th Ed, Sedra & Smith. ′ 2 kn W/L = 1 mA/V , Vt = 1 V, and λ = 0. Use a standard 5% r actual values obtained for ID and VD . Ans. RD = 6.2 k"; ID ≃ 0.49 mA; VD ≃ 1.96 V College of Engineering | Department of Electrical Engineering 5. (6.122 in 7th ed.) Reference: Questions are taken from “Microelectronic Circuits” 7th Ed, Sedra & Smith. 3