Informe Comparador Digital: Diseño y Simulación

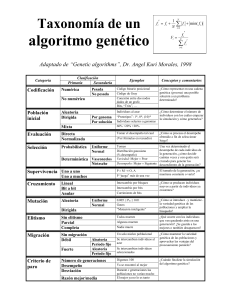

advertisement

INFORME Nº 3. Comparador. IF471- B SISTEMAS DIGITALES Jose Manuel Huamani Bonifacio, jmhuamanib@uni.pe Universidad Nacional de Ingeniería, Facultad de Ciencias 03/04/2024 Resumen En este informe, nos centraremos en entender cómo funciona un comparador de dos números. Comenzaremos mostrando un comparador simple con solo 1 bit para cada número. Luego, exploraremos cómo expandirlo para manejar números de 2 bits cada uno. Finalmente, demostraremos cómo simular su funcionamiento utilizando el programa Proteus. 1. Objetivos 1.1 3. Procedimiento experimental Realizar la tabla de verdad de un comparador y luego realizar el circuito lógico y simular en Proteus. Para empezar a desarrollar un diagrama comparador de 2 números de 2 bits cada uno hallaremos su tabla de verdad y sus gráficos correspondientes. 2. Fundamento teórico • Un circuito digital comparador realiza la comparación de dos palabras A y B de N bits tomadas como un número entero sin signo e indica si son iguales o si una es mayor que otra en tres salidas A = B, A > B y A < B. Solo una de estas salidas estará a 1 y las demás estarán a 0 dependiendo de los valores de las entradas. [1] A 0 0 1 1 B 0 1 0 1 A>B 0 0 1 0 Tabla 1 A=B 1 0 0 1 Comparador A > B B2 B1 A2 A1 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 A<B 0 1 0 0 Gráficamente seria de la siguiente manera. Tabla 2. Figura 1. Comparador de dos números de 1 bit cada uno 1 A>B 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0 Realizamos el mapa K para 4 entradas: ̅̅̅̅ A2 ̅̅̅ A1 ̅A̅̅2̅A1 A2 A1 0 1 0 0 1 0 0 1 1 0 0 0 Tabla 3. ̅̅̅ B2 ̅̅̅ B1 ̅̅̅2 B1 B B2 B1 B2 ̅̅̅ B1 Realizamos el mapa K para 4 entradas: A2 ̅̅̅ A1 0 0 0 0 ̅̅̅ B2 ̅̅̅ B1 ̅̅̅ B2 B1 B2 B1 B2 ̅̅̅ B1 ̅̅̅̅ A2 ̅̅̅ A1 0 1 1 1 ̅A̅̅2̅A1 0 0 1 1 A2 A1 0 0 0 0 A2 ̅̅̅ A1 0 0 1 0 Tabla 5. Por Lo tanto, tendremos la siguiente ecuación: Por Lo tanto, tendremos la siguiente ecuación: ̅̅̅ B2 A2 + ̅̅̅ B2 ̅̅̅ B1 A1 + B2 ̅̅̅ B1 A2 A1 ̅̅̅2̅ + B2 A2 ) B2 ̅A̅̅2̅ + B1 ̅̅̅ A1 (A Simplificando: ̅̅̅ ̅̅̅2 + B2 A2 ) B2 A2 + ̅̅̅ B1 A1 (B Figura 1. Comparador A < B (1111) Figura 1. Comparador A > B (0011) 4. Aplicaciones • • Comparador A < B B2 B1 A2 A1 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 A<B 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 Los comparadores digitales se utilizan en una amplia variedad de aplicaciones, desde la electrónica hasta la mecánica. Algunas de estas aplicaciones incluyen: Control de procesos industriales Control de motores eléctricos Control de sistemas de iluminación Control de sistemas de climatización • Tabla 4. 2 Comparadores de ventana: Los comparadores de ventana son una variante de los comparadores digitales. Estos comparadores comparan una señal con dos valores de referencia diferentes y determinan si la señal está dentro de un rango de valores entre los dos valores de referencia. Los comparadores de ventana se utilizan a menudo en aplicaciones de control, donde se necesita detectar si una señal está dentro de un rango de valores aceptables. • Comparadores de desigualdad: Los comparadores de desigualdad son otro tipo de comparador digital. Estos comparadores comparan dos señales digitales y determinan si son diferentes. Si las señales son diferentes, el comparador produce una salida indicando que las señales son diferentes. Los comparadores de desigualdad se utilizan a menudo para detectar errores en sistemas digitales. • Comparadores de igualdad: Los comparadores de igualdad son similares a los comparadores de desigualdad, pero en lugar de detectar si las señales son diferentes, detectan si son iguales. Si las señales son iguales, el comparador produce una salida indicando que las señales son iguales. Los comparadores de igualdad se utilizan a menudo en sistemas de comunicaciones digitales para detectar si se han producido errores en la transmisión de datos.[2] 5. Conclusiones • Se logro realizar la tabla para un comparador de 2 números de 2 bits, obtener su ecuación lógica y simularlo debidamente. 6. Referencia • [1]Anónimo. Comparador lógico . https://personales.unican.es/manzanom /planantiguo/edigitali/compg4_09.pdf • [2]TELCOMblog. 21 de setiembre del 2023. Comparador digital. https://telcomplus.org/comparadordigital/ 3 INFORME Nº 4. Sumador. IF471- B SISTEMAS DIGITALES Jose Manuel Huamani Bonifacio, jmhuamanib@uni.pe Universidad Nacional de Ingeniería, Facultad de Ciencias 05/04/2024 Resumen En este informe nos centraremos en el diseño y simulación de un sumador de 8 bits utilizando el software Proteus. Nuestro objetivo es verificar la efectividad de nuestro circuito para sumar dos números de 8 bits cada uno. 1. Objetivos 1.1 𝑋 = 𝐴⨁(𝐵⨁𝐶𝑖𝑛 ) Para Cout se tiene: Diseñar circuitos sumadores para 2 números binarios de 8 bits, simular 𝑋 = 𝐴𝐵 + 𝐴𝐶𝑖𝑛 + 𝐵𝐶𝑖𝑛 en Proteus y verificar los sumadores. Entonces que pasaría si el Cin es 0, si esto sucede nuestro primer circuito se reduce a la siguiente expresión: 2. Fundamento teórico Un sumador binario es básicamente un sistema digital que realiza operaciones aritméticas en números binarios, como la suma. Para simplificar y comprender mejor el concepto, vamos a construir un sumador binario para sumar dos números de 1 bit cada uno. Esto nos permitirá crear una tabla que ilustrará cómo funciona este proceso. [1] A 0 0 0 0 1 1 1 1 In B 0 0 1 1 0 0 1 1 𝑋 = 𝐴⨁𝐵 𝐶𝑖𝑛 = 𝐴𝐵 Entonces cuando Cin es 0, vamos a obtener lo siguiente: Out Cin 0 1 0 1 0 1 0 1 Tabla 1 Cout 0 0 0 1 0 1 1 1 X 0 1 1 0 1 0 0 1 Figura 1. Ahora para los siguientes bits tenemos: Ahora obtenemos la ecuación: ̅̅̅̅ 𝑋 = 𝐴̅𝐵̅𝐶𝑖𝑛 + 𝐴̅𝐵𝐶𝑖𝑛 + 𝐴𝐵̅𝐶 𝑖𝑛 + 𝐴𝐵𝐶𝑖𝑛 Reduciendo: Figura 2. 1 3. Procedimiento experimental Dentro de los 7 circuitos restantes: Ahora que hemos explorado el sumador para dos números de un bit, daremos un paso adelante y realizaremos la suma de dos números de 8 bits cada uno. Para facilitar la comprensión, utilizaremos un ejemplo con dos bits, que nos servirá como guía para extender el proceso a 8 bits. Figura 6. 4. Aplicaciones • Con el sumador de 1 bit podemos construir otros tipos de circuitos, tales como un multiplicador a un restador. • El circuito integrado producido por Motorola, tenemos sumadores binarios de 4 bits, estos presentan acarreo de entrada y salida para la conexión en paralelo. Figura 3. Se puede ver que el acarreo de entrada está conectada a tierra, entonces el primero circuito lógico sería como la figura 1. Mientras que los otros 7 circuitos serían armados como la figura 2. Armamos el sumador de 8 bits en el programa Proteus, la cual viene dada por el siguiente circuito: 5. Conclusiones • Hemos completado exitosamente el diseño del circuito en el programa Proteus para sumar dos números de 8 bits cada uno. 6. Referencia • Figura 4. Primer circuito lógico suma: Figura 5. 2 [1] Artículo: Sumador binario. Disponible en: https://wilaebaelectronica.blogspot.com /2017/01/ sumador-binario.html