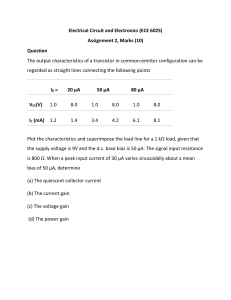

UNDERSTANDING MOSFET Abstract The purpose behind writing this article is to make it easy to understand the physics and working of a MOSFET. This article focuses on explaining every important aspect in the working of a MOSFET. How does the charge transfer take place? What is the inversion layer and how is it created? How does the energy band diagram of MOS layer look like? What happens to energy bands under external bias? The answers to all these questions are given in this article. Harsh Choudhary harshchoudharyhc20@gmail.com Index 1. Introduction 2 2. MOSFET Structure 3 3. Working of a MOSFET 4-6 4. Energy Band Diagram 7-10 5. Energy band diagram under applied bias 11-12 6. Flat band voltage 13 7. Body bias effect 13 1|Page Understanding MOSFET Introduction MOSFET stands for Metal Oxide Semiconductor Field Effect Transistor. It is a gate – insulated field effect transistor. Its mechanics are such that it is used as a voltage controlled current source device. It is a 4-terminal device – drain, gate, source and body. Drain and source cannot be distinguished, since the device is symmetrical. You can call any one terminal drain and another source. To avoid confusion, source is the terminal that provides the carriers. For example, in NMOS, if we apply positive potential to one terminal (say, 3V), and negative potential to one terminal (say, -3V), the electrons flow towards the positive 3V terminal. -3V terminal is providing the charge carriers therefore it is called the source. Also note that current flows from drain(+3V) to source(-3V) in NMOS and vice versa in PMOS. There are two types of MOSFETs – NMOS and PMOS. In NMOS, the channel (inversion layer created by applying external bias) is made up of electrons and in PMOS, it is made of holes. 2|Page MOSFET Structure In the figure, the gate is made up of heavily doped polysilicon. A layer of SiO2 insulates the gate from substrate. The source and drain regions are also heavily doped. The substrate is lightly doped. The ‘W’ of the device is the width as shown (inside the plane) and ‘L’ is the length of the device. L=L’-2.X where x is the side diffusion. This side diffusion happens during fabrication. 3|Page Working of a MOSFET (Here, the working of the N-MOSFET has been explained) Creating the channel Firstly, there should be a channel through which the charges can flow. To create this channel, we apply a potential to the gate terminal. Suppose we start increasing the potential from zero to positive side. The positive charges in the lightly doped p type substrate (p- sub) will start to repel from the gate as shown in fig. 3. As they repel away, they leave behind the negative charge. This transfer of charge depends on the amount of potential we apply at the gate. So, the amount of negative charge formed near the oxide – semiconductor interface mirrors the gate potential. 4|Page The process of forming the channel by applying an external bias to change the material from extrinsic ptype to intrinsic and then to extrinsic n-type is a continuous process. As the negative charge is present towards the gate and the positive charge carriers are repelled down, it forms a depletion region as shown in fig. 4. This will not form the required channel as there are no carriers present. There is only negative charge present which is formed as positive carriers were repelled down leaving behind negative charge. As we increase the voltage from zero, the material at the surface of oxide and semiconductor interface is initially p-type extrinsic (because of doping of substrate material). Then it turns to intrinsic as we increase the voltage. And finally, it turns to extrinsic n-type. When the material is intrinsic, increasing the gate voltage starts the ‘inversion’ of material. From now on, electrons are majority charge carriers. When the material is extrinsic, which means that when the concentration of electrons at the surface is equal to the concentration of holes of the substrate, we say that the ‘inversion’ has reached. The minimum gate potential required to create an inversion region for the conduction of charge carriers across the device is called the threshold voltage of the transistor. When this level of inversion is achieved, the 5|Page transistor is called ‘moderately inverted’. Increasing voltage further will make the inversion stronger leading to ‘strong inversion’. But where do the charge carriers come from? The charge carriers come from the heavily doped source and drain regions. As we increase the gate voltage after depletion region is formed, when the voltage is sufficiently high, electrons will flow from source to drain, creating a channel of charge carriers. Also, one thing to be noted here, this flow of electrons to form the channel, this does not happen at the threshold voltage. Even when the concentration of electrons is not equal to concentration of holes, that is, even when gate potential is slightly less that threshold voltage, this conduction will happen. It also has a name for it, it is called subthreshold conduction! It is called a second order effect. 6|Page Energy Band Diagram Fig. 5shows the energy band diagram of p type semiconductor. Also, the energy is defined negative because, suppose you want to take out an electron from silicon, then you will have to give some energy to it. So, we say that the energy of electron is negative when we want to strip away an electron from a material. Important terms Eo is the vacuum level Ec is the conduction band Ev is the valence band Ei is the intrinsic energy level Ef is the fermi energy level. ϗ - Electron affinity (fixed for a material) φ - Work function Forbidden energy gap or band gap of semiconductor Eg Energy difference between conduction band and valence band of semiconductor. Fermi energy level Ef Highest energy level that an electron can obtain at absolute zero temperature. Since the fermi energy level is close to valence band in PMOS, this means that probability of finding an electron near conduction band is less than the probability of finding a hole near valence band. Electron affinity ϗ 7|Page Energy difference between conduction band and vacuum. Work function φ Energy difference between fermi energy level to vacuum. Bulk potential αb Energy difference between Ei and Ef. Equations k = Boltzmann’s constant Na = Acceptor concentration in p-type semiconductor ni = Intrinsic carrier concentration T = Temperature αb = (kT / q) * loge (Na / ni) q * αb = Ei - Ef q * φSi = (Eg / 2) + q * αb + q * ϗsi q * ϗsi = Eo - Ec 8|Page MOS is the metal, oxide and semiconductor substrate part of the MOSFET. Fig. 6 shows the energy band diagram of individual components of MOS. To draw the final energy band diagram, there are two things to remember 1. In an electronic circuit in thermodynamic equilibrium, the fermi level remains constant throughout its connected components. Therefore, the fermi energy level must be constant in MOS layer. Since as indicated in the diagram above, there is a difference in fermi level of metal and semiconductor. This difference is shown by φms. φms can be called the total amount of band bending required to make fermi energy level constant. In fig. 7 diagram, we have fixed the value of Ef and drawn the energy band diagram. 2. Second thing to remember is that the vacuum level cannot be discontinuous. Therefore, the vacuum level will bend. (Remember we have not applied any external bias while drawing this energy band diagram) Oxide layer The charge distribution is shown in fig. 8. There is the accumulation of positive charge in metal at metal oxide interface to make the net electric field zero inside the metal. The oxide layer acts as a capacitor. There will be an electric field inside the oxide. To know how much the vacuum level will bend in oxide, we have to find the voltage drop by integrating over electric field. 9|Page V = - ∫ Electric field The plate size of capacitor associated with oxide layer is big enough, so the electric field inside the oxide will be constant. Also, this will make the bending in oxide layer to be linear since electric field is constant. Now have we the energy band diagram as shown in fig. 9 in which fermi level is constant (we say thermodynamic equilibrium because there is negligible current flowing into the gate terminal) and vacuum level is continuous. 10 | P a g e Energy band diagram under applied bias We apply a positive voltage to the gate terminal of the device. In the metal, the energy of electrons will decrease. This is because of the externally applied bias. We need to apply more energy to remove the electron from the metal. But this doesn’t mean that the electron is now more bound to the metal. It just means that its energy has been reduced, but to remove an electron from metal, we will have to apply same energy as before. Work function of metal remains constant. Eo level will also shift downward along with Ef of metal as shown in fig. 10. Since the Eo level cannot be continuous, the bending in Eo will increase as shown by blue color level in fig. 10. 11 | P a g e Now the total bending is equal to φms + Vg(Gate voltage) φms + Vg = bending in oxide + bending in semiconductor Final energy band diagram under applied bias is shown in fig. 10 in blue color. It is already discussed that the material near the oxide - semiconductor interface is turned to n-type extrinsic for moderate inversion. So how much bending of bands is required to make the concentration of electrons at surface equal to hole concentration? Initially there is no depletion layer present. The holes are the majority charge carriers in the substrate. We apply a voltage at the gate to make the substrate intrinsic near the oxide – semiconductor interface. A band bending of αb is required to make the material intrinsic. If we increase the gate potential which bends the bands further by αb, then the material turns extrinsic. Therefore, the total band bending is 2 * αb is required to make the material extrinsic n-type near the oxide – semiconductor interface. After 2 * αb bending, increasing the gate voltage further does not increase the width of depletion region. It will only increase the electron density in the inversion layer. 12 | P a g e Flat band voltage It is defined as the voltage at which there is no electrical charge present in the oxide or at the oxidesemiconductor interface. The value of flat band voltage is simply the difference between the work function of metal and semiconductor. Body bias effect This is also a second order effect. It results in the change in the threshold voltage of the transistor when there is a voltage difference between the source and body terminals of the transistor. Suppose we apply a positive gate voltage less than Vth. The source is tied to ground. We then apply a positive voltage to the body terminal. This will cause forward body bias. Since the forward bias will increase the current flowing from gate to ground, it will increase the leakage current. Due to forward bias, the charge in the depletion region is decreased. The gate charge required to mirror the charge in the depletion region to reach inversion is reduced. Therefore the threshold voltage of transistor is reduced. This in turn also reduces the on time Ton of transistor. Since the threshold voltage is reduced, it takes less time to turn on the transistor. In the reverse bias case, depletion width is increased, so we have to apply more voltage to reach inversion. Therefore, threshold voltage is increased. Reverse bias results in less leakage current but increases the Ton of transistor. 13 | P a g e