VLSI ASSIGNMENT

NAME - HARSH RAJ

( ROLL NO.- 21BEC019 )

DECEMBER 2023

1

1.1

Experiment 01: Design and Simulation of a

2-Input NOR Gate

Aim:

The aim of this experiment is to design and simulate a 2-input NOR gate using

VLSI design tools. The objective is to understand the operation of a NOR

gate and gain practical experience in schematic design, simulation, and layout

creation.

1.2

THEORY

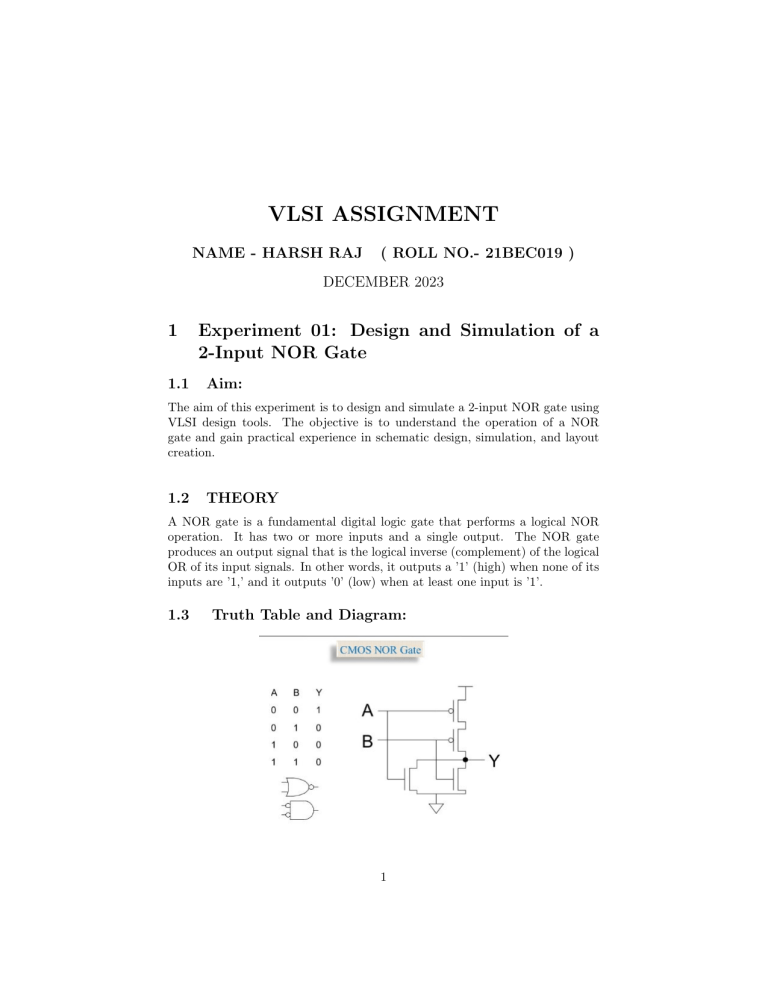

A NOR gate is a fundamental digital logic gate that performs a logical NOR

operation. It has two or more inputs and a single output. The NOR gate

produces an output signal that is the logical inverse (complement) of the logical

OR of its input signals. In other words, it outputs a ’1’ (high) when none of its

inputs are ’1,’ and it outputs ’0’ (low) when at least one input is ’1’.

1.3

Truth Table and Diagram:

1

1.4

Circuit Design:

1) A 2-input NOR gate comprises two NMOS transistors (M1 and M2) in parallel, forming the pull-down network. M1 and M2 are controlled by inputs A

and B. Their sources connect to ground (0 V), and drains go to the output node

(OUT).

2) The gate also includes two PMOS transistors (M3 and M4) in series to create

the pull-up network. M3 and M4 are also controlled by inputs A and B. Their

sources connect to the power supply voltage (Vdd), and drains are connected

to the output node (OUT).

1.5

SPICE CODE:

* SPICE3 file created from NOR.ext technology: scmos

.option scale=1u

.include techfile130.txt

.subckt nor A B Vdd Gnd Out

M1000 Gnd B Out Gnd nmos w=4 l=2

+ ad=40 pd=36 as=28 ps=22

M1001 Out B an 33 V ddpmosw = 9l = 2

+ ad = 45pd = 28as = 63ps = 32

M 1002OutAGndGndnmosw = 4l = 2

+ ad = 0pd = 0as = 0ps = 0

M 1003an 33 AV ddV ddpmosw = 9l = 2

+ ad = 0pd = 0as = 45ps = 28

.ends

1.6

SIMULATION CODE:

* SPICE3 file created from nor.ext - technology: scmos

.option scale=1u

.include techfile130.txt

.include NOR.spice

Vdd Vdd 0 1.2

Va A 0 PULSE(0 1.2 1n 1n 1n 50n 100n)

Vb B 0 PULSE(0 1.2 1n 1n 1n 100n 200n)

Xnor A B Vdd 0 Out nor

.control

tran 0.1n 400n

plot v(Out) v(A) v(B)

.end

2

1.7

SIMULATION GRAPH:

1.8

Layout Design (Using Magic) :

3

1.9

Conclusion:

In conclusion, the experiment successfully simulated a 2-input NOR gate using

SCmos technology. This hands-on experience in VLSI design and CMOS logic

deepened our understanding of digital circuits. The NOR gate’s functionality

was verified, highlighting its crucial role in digital systems. This knowledge

serves as a foundation for more complex designs, emphasizing the significance

of NOR gates in digital circuitry.

4

2

2.1

Experiment 02: Design and Simulation of a

2-Input NAND Gate

Aim:

The aim of this experiment is to design and simulate a 2-input NAND gate using

VLSI design tools. The objective is to understand the operation of a NAND

gate and gain practical experience in schematic design, simulation, and layout

creation.

2.2

THEORY

A NAND gate is a fundamental digital logic gate that performs a logical NAND

operation. It has two or more inputs and a single output. The NAND gate

produces an output signal that is the logical inverse (complement) of the logical

AND of its input signals. In other words, it outputs a ’0’ (low) when none of

its inputs are ’1,’ and it outputs ’1’ (high) when at least one input is ’1’.

2.3

Truth Table and Diagram:

2.4

Circuit Design:

A 2-input NAND gate comprises two NMOS transistors (M1 and M2) in series,

forming the pull-down network.

1) M1 and M2 are controlled by inputs A and B.

2) Their sources connect to the power supply voltage (Vdd), and drains are

connected to the output node (OUT). The gate includes two PMOS transistors

(M3 and M4) in parallel to create pull-up network.

3) M3 and M4 are also controlled by inputs A and B.

4)Their sources connect to ground (0 V), and drains go to the output node

(OUT).

5

2.5

SPICE CODE:

* SPICE3 file created from NanD.ext - technology: scmos

.option scale=1u

.include techfile130.txt

.subckt nand Va Vb Out Vdd Gnd

M1000 Vdd Vb Out Vdd pmos w=18 l=3

+ ad=342 pd=110 as=198 ps=58

M1001 an 5n 39V aGndGndnmosw = 10l = 3

+ ad = 110pd = 42as = 80ps = 36

M 1002OutV aV ddV ddpmosw = 18l = 3

+ ad = 0pd = 0as = 0ps = 0

M 1003OutV ban 5n 39Gndnmosw = 10l = 3

+ ad = 110pd = 42as = 0ps = 0

.ends

2.6

SIMULATION CODE:

.option scale=1u

.include techfile130.txt

.include NanD.spice

Vdd Vdd 0 1.2

Va Va 0 PULSE(0 1.2 0n 1n 1n 50n 100n)

Vb Vb 0 PULSE(0 1.2 0n 1n 1n 100n 200n)

Xnand Va Vb Out Vdd Gnd nand

.control

tran 0.1n 400n

plot v(Out) v(Va) v(Vb)

.endc

.end

6

2.7

SIMULATION GRAPH:

2.8

Layout Design (Using Magic) :

7

2.9

Conclusion:

n conclusion, this experiment effectively designed and simulated a 2-input NAND

gate. It offered valuable hands-on experience in VLSI design, CMOS logic, and

simulation techniques. The results verified the gate’s NAND operation, which

is fundamental in digital logic circuits. This knowledge can be applied to create

more intricate digital systems and serves as a foundational building block in the

realm of digital circuit design.

8

3

3.1

Experiment 03: Design and Simulation of a

2-Input XOR Gate

Aim:

The aim of this experiment is to design and simulate a 2-input XOR gate using

VLSI design tools. The objective is to understand the operation of an XOR

gate and gain practical experience in schematic design, simulation, and layout

creation.

3.2

THEORY

An XOR gate is a fundamental digital logic gate that performs a logical Exclusive OR (XOR) operation. It has two inputs and a single output. The XOR

gate produces an output signal that is ’1’ (high) when an odd number of its

inputs are ’1,’ and it outputs ’0’ (low) when an even number of inputs are ’1.’

It effectively represents inequality, where it is true when the inputs are different

and false when they are the same.

3.3

Truth Table and Diagram:

9

3.4

Circuit Design:

A 2-input XOR gate comprises two NMOS transistors (M1 and M2) connected

in a parallel arrangement, forming the pull-down network. M1 and M2 are controlled by inputs A and B. Their sources connect to ground (0 V), and drains

are connected to the output node (OUT).

The gate also includes two PMOS transistors (M3 and M4) in series to create the pull-up network. M3 and M4 are also controlled by inputs A and B.

Their sources connect to the power supply voltage (Vdd), and drains go to the

output node (OUT).

3.5

SPICE CODE:

* SPICE3 file created from 2xor.ext - technology: scmos

.option scale=1u

.include techfile130.txt

.subckt xor Va Vb Vab Vbb Vdd Out Gnd

M1000 Out Vbb Va Gnd nmos w=8 l=2

+ ad=128 pd=64 as=64 ps=32

M1001 Out Vbb Vab w3 5n 17pmosw = 8l = 2

+ ad = 128pd = 64as = 128ps = 64

M 1002V ddV aV abwn 27n 8pmosw = 8l = 2

+ ad = 128pd = 64as = 0ps = 0

M 1003V abV aGndGndnmosw = 8l = 2

+ ad = 120pd = 62as = 128ps = 64

M 1004OutV bV aw3 52 3pmosw = 8l = 2

+ ad = 0pd = 0as = 64ps = 32

M 1005V bbV bGndGndnmosw = 8l = 2

+ ad = 56pd = 30as = 0ps = 0

M 1006V ddV bV bbwn 2n 8pmosw = 8l = 2

+ ad = 0pd = 0as = 64ps = 32

M 1007OutV bV abGndnmosw = 8l = 2

+ ad = 0pd = 0as = 0ps = 0

.ends

3.6

SIMULATION CODE:

.option scale=1u

.include techfile130.txt

.include 2xor.spice

Vdd Vdd 0 1.2

Va Va 0 PULSE(0 1.2 1n 1n 1n 100n 200n)

Va0 Vab 0 PULSE(1.2 0 1n 1n 1n 100n 200n)

10

Vb Vb 0 PULSE(0 1.2 1n 1n 1n 200n 400n)

Vb0 Vbb 0 PULSE(1.2 0 1n 1n 1n 200n 400n)

Xxor Va Vb Vab Vbb Vdd Out Gnd xor

.control

tran 0.1n 800n

plot v(Out) v(Va) v(Vb)

.endc

.end

3.7

SIMULATION GRAPH:

3.8

Layout Design (Using Magic) :

11

3.9

Conclusion:

In summary, this experiment successfully designed and simulated a 2-input XOR

gate, providing practical insights into VLSI design, CMOS logic, and simulation

methodologies. The results affirmed the XOR gate’s operational characteristics,

a crucial element in digital logic circuits. The acquired knowledge enhances the

capacity to construct advanced digital systems, leveraging the XOR gate as a

fundamental building block in the field of digital circuit design.

12

4

4.1

Experiment 04: Design and Simulation of A

Inverter

Aim:

The aim of this experiment is to design and simulate a digital inverter using VLSI

design tools. The objective is to understand the operation of an inverter and

gain practical experience in schematic design, simulation, and layout creation.

4.2

THEORY:

1. An inverter is a fundamental digital logic gate with a single input and a

single output.

2. It produces the logical complement of its input, i.e., ’1’ (high) for ’0’ (low)

input and ’0’ (low) for ’1’ (high) input.

3. In practical implementation, it often uses an NMOS transistor, where input ’0’ turns the transistor on (output ’1’), and input ’1’ turns it off (output

’0’).

4.3

Truth Table and Diagram:

13

4.4

Circuit Design:

1) An inverter comprises a single NMOS transistor (M1) that forms the pulldown network. M1 is controlled by the input (IN). Its source connects to ground

(0 V), and the drain is connected to the output node (OUT).

2) The inverter also includes a single PMOS transistor (M2) in series to create

the pull-up network. M2 is controlled by the same input (IN). Its source connects to the power supply voltage (Vdd), and the drain goes to the output node

(OUT).

4.5

SPICE CODE:

* SPICE3 file created from inv.ext - technology: scmos

.option scale=1u

.include techfile130.txt

.subckt inv vdd gnd in out

M1000 out in vdd vdd pmos w=6 l=2

+ ad=30 pd=22 as=30 ps=22

M1001 out in gnd Gnd nmos w=6 l=2

+ ad=30 pd=22 as=30 ps=22

.ends

4.6

SIMULATION CODE:

SPICE3 file created from inv.ext - technology: scmos

.option scale=1u

.include techfile130.txt

.include inv.spice

Vdd vdd 0 1.2

Vin in 0 PULSE(0 1.2 2n 2n 2n 50n 100n)

Xinv vdd 0 in out inv

.control

tran 0.1n 300n

plot v(out) v(in)

.endc

.end

14

4.7

SIMULATION GRAPH:

4.8

Layout Design (Using Magic) :

15

4.9

Conclusion:

In summary, this experiment effectively designed and simulated a CMOS inverter, offering practical insights into VLSI design, CMOS logic, and simulation

techniques. The results validated the inverter’s operational characteristics, fundamental in digital logic circuits. This acquired knowledge enriches the ability

to construct sophisticated digital systems, recognizing the inverter’s pivotal role

as a foundational component in digital circuit design.

16

5

5.1

Experiment 05: Design and Simulation of D

Flip Flop

Aim:

The aim of this experiment is to design and simulate a D flip-flop using VLSI

design tools with transmission gates. The objective is to understand the operation of a D flip-flop based on transmission gates and gain practical experience in

schematic design, simulation, and layout creation while exploring the behavior

of transmission gate-based flip-flops.

5.2

THEORY:

1. A D flip-flop is a digital circuit that stores a single data bit.

2. It uses a clock signal to control data storage.

3. Transmission gates are employed in D flip-flops for data transfer.

4. Data is transferred based on the clock signal, allowing synchronized storage

and retrieval.

5. The flip-flop stores the input data on the clock signal’s transition.

6. D flip-flops are crucial for sequential digital circuits, ensuring controlled data

synchronization and storage.

5.3

Truth Table and Diagram:

17

5.4

Truth Table and Diagram:

5.5

Circuit Design:

A D flip-flop employs transmission gates to store and transfer data. It consists

of two main parts:

1. Data Transmission Stage:

a) The D input (D) is connected to one set of transmission gates.

b) Another set of transmission gates connects to the complement of the D input

(NOT D).

c) The clock signal (CLK) controls the transmission gates, allowing data to pass

through or be blocked.

d) Data is transferred from D to the flip-flop’s internal nodes when the clock is

enabled.

2. Latch Stage:

a) The flip-flop has two cross-coupled inverters (NOR or NAND gates) that

store data.

b) The data from the transmission gates is stored in these latches.

c) The cross-coupled inverters maintain the output state until the clock signal

triggers a new data transfer.

18

5.6

SPICE CODE:

* SPICE3 file created for a D Flip-Flop in scmos technology

.option scale=1u

.include techfile130.txt

.subckt transmissiong ate(inoutctrlgndvdd)

Mp outinctrlvddpmosw = 6l = 4ad = 48pd = 28as = 48ps = 28

Mn outinctrlgndnmosw = 6l = 4ad = 48pd = 28as = 48ps = 28

.ends

.subcktinverter(inoutgndvdd)

Mp outinvddvddpmosw = 6l = 2ad = 30pd = 22as = 30ps = 22

Mn outingndgndnmosw = 6l = 2ad = 30pd = 22as = 30ps = 22

.ends

.subcktdl atch(V ddGndClkClk0D0GndD)

Xtransg ate1 GndV ddClkClk0Dlatch1Out1

transmissiong ate

Xtransg ate0 GndV ddClk0ClkDlatch0Out0

transmissiong ate

Xinv0 Dlatch1D0GndV ddinv

Xinv1 D0Out1GndV ddinv

.ends

.subcktdf f (V ddGndClkClk0DD0Out)

Xdl atch0 V ddClkClk0D0GndDDl atch

Xdl atch1 V ddClk0ClkOutGndD0Dl atch

C0Clk0Gnd43.87f F

C1D0Gnd9.21f F

C2ClkGnd5.23f F

.ends

5.7

SIMULATION CODE:

.option scale=1u

.include techfile130.txt

.include dflipflop.spice

Vdd Vdd 0 1.2

Va Clk 0 PULSE(0 1.2 0n 1n 1n 100n 200n)

Vb Clk0 0 PULSE(1.2 0 0n 1n 1n 100n 200n)

Vc D 0 PULSE(0 1.2 0n 1n 1n 150n 300n)

Xdflipflop Vdd 0 Clk Clk0 D D0 Out dff

19

.control

tran 0.1n 1200n

plot v(Out) v(Clk) v(D)

.endc

.end

5.8

SIMULATION GRAPH:

5.9

Layout Design (Using Magic) :

20

5.10

Conclusion:

In conclusion, the hybrid design of a D Flip-Flop using D Latches and Transmission Gates offers an effective solution for digital circuit applications. The

combination of D Latches for data storage and Transmission Gates for controlled

data flow results in a versatile and efficient flip-flop design. This approach optimizes performance, minimizes propagation delays, and allows for flexibility in

meeting specific design requirements, emphasizing the importance of thoughtful

component selection in digital circuit design.

21

6

6.1

Experiment 06: FINITE STATE MACHINE

Aim:

To Develop a versatile Finite State Machine (FSM) system capable of handling

both Moore and Mealy machine models, along with specialized components for

sequence detection.

6.2

THEORY:

1)Moore Machine:

Implement a Moore machine with distinct states and associated outputs. Demonstrate the functionality of the Moore machine in a practical application, such

as a simple control system.

2) Mealy Machine:

Develop a Mealy machine with outputs that depend on both current states and

input signals.Showcase the advantages of Mealy machines in scenarios where

dynamic and immediate responses are required.

3)Moore Sequence Detector:

Create a Moore-based sequence detector capable of recognizing specific input

sequences.Illustrate the application of sequence detection in scenarios like pattern recognition or signal processing.

4) Moore Detector:

Design a Moore detector that responds to certain conditions in the system.Explore

how Moore detectors can be employed for event-driven applications, providing

outputs based on the system’s current state.v

6.3

Implementation Steps:

1)Define the system specifications and requirements.

2)Design the state diagrams for both Moore and Mealy machines.

3)Implement the FSM using a programming language or hardware description

anguage.

4)Test and validate the functionality of the Moore and Mealy machines separately.

5)Integrate the Moore sequence detector and Moore detector into the FSM

framework.

6)Demonstrate the FSM system in various scenarios to showcase its versatility.

22

6.4

VERILOG CODE OUTPUT GRAPH

6.4.1

MEALY MACHINE:

CODE:

module mealy (

input x, clk, rst,

output reg y

);

parameter zero = 1’b0;

parameter one = 1’b1;

// State registers

reg state, next_state;

always @(posedge clk or posedge rst) begin

if (rst) begin

state <= zero;

y <= 1’b0; // Reset output on reset

end

else begin

state <= next_state;

end

end

always @(x, state) begin // Explicit sensitivity list

case (state)

zero: begin

if (x) begin

next_state = one;

y = 1’b1;

end

else begin

next_state = zero;

y = 1’b0;

end

end

one: begin

if (x) begin

next_state = one;

y = 1’b1;

end

else begin

23

next_state = zero;

y = 1’b0;

end

end

// Add more states as needed

default: begin

next_state = zero;

y = 1’b0;

end

endcase

end

endmodule

OUTPUT GRAPH:

24

6.4.2

MEALY SEQUENCE DETECTOR :

CODE:

/*‘timescale 1ns/1ps

module seq_det_mealy (

input clk, rst, x,

output reg y);

reg [1:0] state, next_state;

parameter a = 2’b00, b = 2’b01, c = 2’b10;

always @(posedge clk or posedge rst) begin

if (rst) begin

state = a;

end

else begin

state = next_state;

end

end

always @(x, state) begin

case (state)

a: begin

if (x)

begin

next_state = b;

y=0;

end

else

begin

next_state = a;

y = 0;

end

end

b: begin

if (x)

begin

next_state = c;

y=0;

end

else

begin

next_state = a;

y=0;

end

end

c: begin

if (x)

25

begin

next_state = c;

y=0;

end

else

begin

next_state = a;

y = 1;

end

end

endcase

end

endmodule

OUTPUT GRAPH:

26

6.4.3

MOORE SEQUENCE DETECTOR :

CODE:

module seq_det_moore (

input clk, rst, x,

output reg y

);

reg [1:0] state, next_state;

parameter a = 2’b00, b = 2’b01, c = 2’b10, d = 2’b11;

always @(posedge clk) begin

if (rst)

state <= a;

else

state <= next_state;

end

always @(x, state) begin

case (state)

a: begin

if (x)

next_state

else

next_state

end

b: begin

if (x)

next_state

else

next_state

end

c: begin

if (x)

next_state

else

next_state

end

d: begin

if (x)

next_state

else

next_state

end

endcase

= b;

= a;

= c;

= a;

= c;

= d;

= b;

= a;

27

end

always @(state) begin

case (state)

a: y = 0;

b: y = 0;

c: y = 0;

d: y = 1;

endcase

end

endmodule

OUTPUT GRAPH:

28

6.4.4

TESTBENCH:

‘timescale 1ns/1ps

‘include "seq_det_moore.v"

module tb;

reg x, clk, rst;

wire y;

seq_det_moore DET(.x(x), .clk(clk), .rst(rst), .y(y));

always begin

clk <= 0;

#10;

clk <= 1;

#10;

end

initial begin

$dumpfile("xyz.vcd");

$dumpvars;

#300 $finish;

end

initial begin

rst <= 1;

#20 rst <= 0;

#20 x <= 1;

#20 x <= 1;

#20 x <= 0;

#20 x <= 1;

#20 x <= 0;

#20 x <= 1;

#20 x <= 1;

#20 x <= 1;

#20 x <= 1;

#20 x <= 1;

#20 x <= 1;

#20 x <= 1;

#20 x <= 0;

// Add a delay to let the simulation run for a while before finishing

#300 $finish;

end

endmodule

29

6.4.5

YOSYS DIAGRAM:

1) MEALY MACHINE:

2) MEALY SEQUENCE DETECTOR:

30

3) MOORE SEQUENCE DETECTOR:

31

7

7.1

Experiment 07: DECODER

Aim:

Design and implement a decoder circuit in Verilog using three different modeling styles - structural, behavioral, and dataflow. The project aims to explore and demonstrate a comprehensive understanding of these Verilog modeling

paradigms and their applications in digital circuit design.

7.2

THEORY:

1) Structural Model:

Develop a structural representation of the decoder using hierarchical modules.Utilize

basic logic gates (AND, OR, NOT) and multiplexers to create a modular and

well-organized structural model.

2) Behavioral Model:

Implement a behavioral model that describes the functionality of the decoder

using high-level constructs.Use procedural blocks (always, initial) and conditional statements to capture the decoder’s behavior in terms of input-output

relationships.

3) Dataflow Model:

Create a dataflow model to represent the decoder’s operation in terms of data

flow and concurrent assignments.Utilize continuous assignments and assign statements to express the functional dependencies within the decoder.

7.3

Implementation Steps:

1) Structural Model:

Define the module interfaces, inputs, and outputs.Instantiate lower-level modules for gates and multiplexers.Connect the instantiated modules to create the

hierarchical structure.Simulate and verify the structural model’s functionality.

2) Behavioral Model:

Define the module with inputs, outputs, and internal variables.Use procedural blocks to describe the desired behavior.Implement conditional statements to

capture the decoder’s logic.Simulate and verify the behavioral model’s correctness.

32

3) Dataflow Model:

Define the module with inputs, outputs, and intermediate signals.Use continuous assignments to express the dataflow relationships.Describe the decoder’s

logic in terms of signal assignments.Simulate and verify the dataflow model’s

functionality.

7.4

VERILOG CODE OUTPUT GRAPH

7.4.1

DECODER(STRUCTURAL):

CODE:

module decoder(input a,b,e,output [3:0]d);

wire b_bar,a_bar;

not n1(a_bar,a);

not n2(b_bar,b);

and #2 a1(d[0],a_bar,b_bar,e), a2(d[1],a_bar,b,e),

a3(d[2],a,b_bar,e), a4(d[3],a,b,e);

//and a2(d[1],a_bar,b,e);

//and a3(d[2],a,b_bar,e);

//and a4(d[3],a,b,e);

endmodule

OUTPUT GRAPH:

33

7.4.2

DECODER(BEHAVIORAL):

CODE:

module decoder(input A, B, E, output reg [3:0]D);

always @(A or B or E)

begin

case ({E,A,B})

3’b000: D = 4’b0000;

3’b001: D = 4’b0000;

3’b010: D = 4’b0000;

3’b011: D = 4’b0000;

3’b100: D = 4’b0001;

3’b101: D = 4’b0010;

3’b110: D = 4’b0100;

3’b111: D = 4’b1000;

endcase

end

endmodule

OUTPUT GRAPH:

34

7.4.3

DECODER(DATAFLOW):

CODE:

module decoder( input A, B, E, output [3:0]D);

assign

D[1] =

D[2] =

D[3] =

D[0] = ~A & ~B & E,

~A & B & E,

A & ~B & E,

A & B & E ;

endmodule

OUTPUT GRAPH:

7.5

TEST-BENCH:

module tb_decoder();

reg A,B,E;

wire [3:0]D;

decoder dec1(A,B,E,D);

initial

begin

$dumpfile("xyz.vcd");

$dumpvars;

#10 E<=1’b0; A<=1’b0; B<=1’b0;

#10 E<=1’b0; A<=1’b0; B<=1’b1;

#10 E<=1’b0; A<=1’b1; B<=1’b0;

35

#10 E<=1’b0; A<=1’b1; B<=1’b1;

#10 E<=1’b1; A<=1’b0; B<=1’b0;

#10 E<=1’b1; A<=1’b0; B<=1’b1;

#10 E<=1’b1; A<=1’b1; B<=1’b0;

#10 E<=1’b1; A<=1’b1; B<=1’b1;

#10 $finish;

end

always @(A or B or E)

$monitor("At TIME(in ns)=%t, A=%d B=%d E=%d D=%d", $time, A, B, E, D);

endmodule

7.6

YOSYS DIAGRAM:

36

8

8.1

Experiment 08: MEMORY

Aim:

Design and implement a memory module in Verilog capable of read and write

operations. The module includes an array of 64 4-bit registers, providing a

flexible and configurable memory space.

8.2

THEORY:

1) Configurability:

The memory module supports a flexible memory space with 64 registers, each 4

bits wide.Configurable for different memory requirements by adjusting the size

of the memory array.

2) Read and Write Operations:

Implements both read (rw=1) and write (rw=0) operations.During a read operation, the module outputs the data stored at the specified address (addr) During

a write operation, the module stores the input data (datain) at the specified address.

3) Enable Signal:

The en signal activates the memory operations. When inactive, the module

outputs a high-impedance state (4’bz).

8.3

Implementation Steps:

1) Declare a configurable memory array with appropriate bit width and size.

2) Utilize the always block to control read and write operations based on the

enable (en) and read/write (rw) signals.

3) Implement conditional statements to handle read and write cases within the

always block.

4) Ensure the module outputs the correct data based on the specified address

during read operations.

5) Simulate and verify the module’s functionality in a testbench environment.

37

8.4

VERILOG CODE OUTPUT GRAPH

8.4.1

MEMORY:

CODE:

module memory (

input en,

// Enable signal

input rw,

// Read/Write signal

input [3:0] datain, // Data input

input [5:0] addr,

// Address input

output reg [3:0] dataout // Data output

);

reg [3:0] mem [0:63]; // Declare a 64-word memory, indexed from 0 to 63

always @ (en, rw, addr) begin

if (en) begin

if (rw) // Read operation

dataout = mem[addr];

else // Write operation

mem[addr] = datain;

end

else

dataout = 4’bz; // Output is high impedance when en is not active

end

endmodule

OUTPUT GRAPH:

38

8.4.2

TEST BENCH:

‘timescale 1ns / 1ps

‘include "memory.v"

module tb(input CLK, RST_N);

parameter ADDR_WIDTH = 4;

parameter DATA_WIDTH = 16;

parameter DEPTH = 16;

reg clk;

reg cs;

reg we;

reg oe;

reg [ADDR_WIDTH-1:0] addr;

wire [DATA_WIDTH-1:0] data;

reg [DATA_WIDTH-1:0] tb_data;

integer i;

single_port_sync_ram #(.DATA_WIDTH(DATA_WIDTH)) u0 (.clk(clk), .addr(addr), .data(data), .

always #10 clk = ~clk;

assign data = !oe ? tb_data : ’hz;

initial

begin

$dumpfile("xyz.vcd");

$dumpvars;

{clk, cs, we, addr, tb_data, oe} <= 0;

repeat (2)

@(posedge clk);

for (i = 0; i < 2**ADDR_WIDTH; i= i+1)

begin

repeat (1)

@(posedge clk) addr <= i; we <= 1; cs <=1; oe <= 0; tb_data <=$random;

end

for (i = 0; i < 2**ADDR_WIDTH; i= i+1)

begin

repeat (1)

@(posedge clk) addr <= i; we <= 0; cs <= 1; oe <= 1;

end

#20 $finish;

end

endmodule

39

9

9.1

Experiment 09: FULL ADDER

Aim:

Design and implement a Full Adder circuit in Verilog using three different modeling styles - structural, behavioral, and dataflow. The project aims to explore and demonstrate a comprehensive understanding of these Verilog modeling

paradigms and their applications in digital circuit design.

9.2

THEORY:

1) Structural Model:

Develop a structural representation of the Full Adder using hierarchical modules.Utilize basic logic gates (AND, OR, XOR) to create a modular and wellorganized structural model.Implement lower-level modules for the individual

XOR, AND, and OR gates.

2) Behavioral Model:

Implement a behavioral model that describes the functionality of the Full Adder

using high-level constructs.Use procedural blocks (always, initial) and conditional statements to capture the Full Adder’s behavior in terms of input-output

relationships.Describe the sum and carry-out generation based on input signals.

3) Dataflow Model:

Create a dataflow model to represent the Full Adder’s operation in terms of

data flow and concurrent assignments.Utilize continuous assignments and assign

statements to express the functional dependencies within the Full Adder.Express

the logic relationships between inputs, outputs, and intermediate signals.

9.3

Implementation Steps:

1) Structural Model:

Define module interfaces and instantiate XOR, AND, and OR gates.Connect

modules hierarchically to create a structural representation.

2)Behavioral Model:

Define input and output ports in the module.Use procedural blocks to describe

Full Adder behavior based on input-output relationships.

3) Dataflow Model:

40

Define module ports.Express Full Adder’s operation using continuous assignments and functional dependencies.

4) Verification:

Simulate each model and verify correct sum and carry-out generation. Analyze and compare outcomes to assess modeling strengths and weaknesses.

9.4

VERILOG CODE OUTPUT GRAPH

9.4.1

ADDER(STRUCTURAL):

CODE:

‘timescale 1ns / 1ps

module full_adder( A, B, Cin, S, Cout);

input A, B, Cin;

output S, Cout;

wire p,q,r;

xor(p,A,B);

xor(S,p,Cin);

and(r,A,B);

and(q,p,Cin);

or(Cout,q,r);

endmodule

OUTPUT GRAPH:

41

9.4.2

ADDER(BEHAVIORAL):

CODE:

‘timescale 1ns / 1ps

module full_adder( A, B, Cin, S, Cout);

input wire A, B, Cin;

output reg S, Cout;

always @(A

begin

case (A |

3’b000:

3’b001:

3’b010:

3’b011:

3’b100:

3’b101:

3’b110:

3’b111:

endcase

end

or B or Cin)

B | Cin)

begin S =

begin S =

begin S =

begin S =

begin S =

begin S =

begin S =

begin S =

0;

1;

1;

0;

1;

0;

0;

1;

Cout

Cout

Cout

Cout

Cout

Cout

Cout

Cout

=

=

=

=

=

=

=

=

0;

0;

0;

1;

0;

1;

1;

1;

endmodule

OUTPUT GRAPH:

42

end

end

end

end

end

end

end

end

9.4.3

ADDER(DATAFLOW):

CODE:

‘timescale 1ns / 1ps

module full_adder( A, B, Cin, S, Cout);

input A, B, Cin;

output S, Cout;

wire x,y,z;

assign x = A ^ B ; // even one single expression can do.

assign y = x & Cin ;

assign z = A & B ;

assign S = x ^ Cin ;

assign Cout = y | z ;

endmodule

OUTPUT GRAPH:

43

9.5

TEST BENCH

odule test_full_adder(input CLK, RST_N);

reg A, B, Cin;

wire Sum, Cout;

full_adder full_adder1(A, B, Cin, Sum, Cout);

initial begin

$dumpfile("xyz.vcd");

$dumpvars;

#10

#10

#10

#10

#10

#10

#10

#10

A

A

A

A

A

A

A

A

=

=

=

=

=

=

=

=

1’b0;

1’b0;

1’b0;

1’b0;

1’b1;

1’b1;

1’b1;

1’b1;

B

B

B

B

B

B

B

B

=

=

=

=

=

=

=

=

1’b0;

1’b0;

1’b1;

1’b1;

1’b0;

1’b0;

1’b1;

1’b1;

Cin

Cin

Cin

Cin

Cin

Cin

Cin

Cin

#30 #10 $finish;

end

endmodule

9.5.1

YOSYS DIAGRAM:

44

=

=

=

=

=

=

=

=

1’b0;

1’b1;

1’b0;

1’b1;

1’b0;

1’b1;

1’b0;

1’b1;

10

Experiment 10: AND GATE

10.1

Aim:

Design a 2-input AND gate in Verilog to implement the logical AND operation

between two input signals.

10.2

THEORY:

An AND gate produces a high output (1) only when both of its inputs are high

(1). The logical operation is represented as Z = A B, where Z is the output

and A and B are the input signals.

10.3

VERILOG CODE OUTPUT GRAPH

CODE:

module and_gate2 (

input wire A,

input wire B,

output reg Z

);

always @(A or B) begin

Z = A & B;

end

endmodule

OUTPUT GRAPH:

45

10.4

TEST BENCH

module test_or(input CLK, RST_N);

reg A, B;

wire Y;

and_gate2 and1(A, B, Y);

initial begin

$dumpfile("xyz.vcd");

$dumpvars;

#10 A <= 1’b0; B<=1’b0;

#10 A <= 1’b0; B<=1’b1;

#10 A <= 1’b1; B<=1’b0;

#10 A <= 1’b1; B<=1’b1;

#30 #10 $finish;

end

endmodule

10.4.1

YOSYS DIAGRAM:

46

11

Experiment 11: 2 OR GATE

11.1

Aim:

Design a 2-input OR gate in Verilog to implement the logical OR operation

between two input signals.

11.2

THEORY:

An OR gate produces a high output (1) when at least one of its inputs is high

(1). The logical operation is represented as Z = A — B, where Z is the output

and A and B are the input signals.

11.3

VERILOG CODE OUTPUT GRAPH

CODE:

module or_gate2 (

input wire A,

input wire B,

output reg Z

);

always @(A or B) begin

Z = A or B;

end

endmodule

OUTPUT GRAPH:

47

11.4

TEST BENCH

module test_or(input CLK, RST_N);

reg A, B;

wire Y;

or_gate2 and1(A, B, Y);

initial begin

$dumpfile("xyz.vcd");

$dumpvars;

#10 A <= 1’b0; B<=1’b0;

#10 A <= 1’b0; B<=1’b1;

#10 A <= 1’b1; B<=1’b0;

#10 A <= 1’b1; B<=1’b1;

#30 #10 $finish;

end

endmodule

11.4.1

YOSYS DIAGRAM:

48

12

12.1

Experiment 12: INVERTER

Aim:

Design and simulate a 1-input inverter (NOT gate) in Verilog and verify its

functionality through a testbench.

12.2

THEORY:

An inverter, often referred to as a NOT gate, is a fundamental digital logic gate

that performs the logical operation of inversion.The logical expression for an

inverter is denoted as Z=AZ=A, where ZZ is the output and AA is the input.

12.3

VERILOG CODE OUTPUT GRAPH

CODE:

module inv(input A, output B);

assign B = ~A ;

endmodule

OUTPUT GRAPH:

49

12.4

TEST-BENCH

‘include "inv.v"

module test_inv(input CLK,RST_N);

reg A;

wire B;

inv inv1(A,B);

initial

begin

$dumpfile("xyz.vcd");

$dumpvars;

#10 A<=1’b1;

#10 A<=1’b0;

#10 A<=1’b1;

#10 A<=1’b1;

#10 A<=1’b0;

#10 A<=1’b1;

#10 A<=1’b0;

#10 A<=1’b1;

#10 $finish;

end

endmodule

12.4.1

YOSYS DIAGRAM:

50

13

13.1

Experiment 13: PROCESSOR

Aim:

Design and simulate a simple processor in Verilog that performs basic operations, such as addition and subtraction, based on instructions stored in memory.

The processor fetches instructions from memory, decodes them, executes the

corresponding operation, and stores the result back in memory.

13.2

THEORY:

1. Overview

- Processor: Core of a computer; performs operations on data.

2. Registers:

- Small, fast storage locations (e.g., ‘PC‘, ‘R0‘).

3. States and FSM:

- Operates in fetch, decode, execute, and store states.

4. Control Signals:

- ‘r‘ for read, ‘w‘ for write.

5. Instruction Execution:

- Fetches, decodes, and executes instructions.

6. Arithmetic Operations:

- Performs operations like addition and subtraction.

7. Program Counter (‘PC‘):

- Keeps track of the next instruction address.

8. Memory Interaction:

- Reads from and writes to memory.

9. Simulation and Verification:

- Simulates design for correctness.

10. Finite State Machine (FSM):

- Controls operation sequence.

11. Reset Mechanism:

- Initializes processor to a known state.

12. Data Flow:

51

- Data moves between registers and bus.

13. Clock Signal:

- Synchronizes processor operations.

14. On-Chip Memory:

- Stores instructions and data.

15. Processor Types:

- Varies in complexity (educational to commercial).

13.3

Implementation Steps:

1. Initialization:

- Set initial values for registers (R0, R1, R2, PC, IR).

- Start in the fetch state.

2. State Machine:

- Use a finite state machine (state, next_state).

- Define transitions based on opcode (IR) and control signals (r, w).

3. Memory Interaction:

- In fetch state, set ‘r‘ for memory read.

- In store state, set ‘w‘ for memory write.

4. Arithmetic Operations:

- Perform addition/subtraction per opcode.

5. Program Counter:

- Increment PC after each instruction.

6. Data Bus:

- Control data bus (data) based on read (‘r‘) or write (‘w‘) signals.

52

13.4

VERILOG CODE OUTPUT GRAPH

VERILOG CODE:

module processor(input clk, rst, inout [7:0] data, output r, w, output [7:0] P

reg [7:0] IR, R0, R1, R2, PC;

reg [7:0] tmp_data;

initial PC = 8’h00;

initial R0 = 8’h20;

initial R1 = 8’h15;

initial R2 = 8’h00;

initial IR = 8’h00;

reg [2:0] state, next_state;

reg r,w;

initial r = 0;

initial w = 0;

parameter

fetch = 3’b000, decode = 3’b001, execute_add = 3’b010, execute_sub = 3’b011, s

always @(posedge clk)

begin

if(rst) state = fetch;

else state = next_state;

end

always @(state)

case(state)

fetch:

begin

w <= 0;

r <= 1;

next_state = decode;

end

decode:

begin

#1

IR <= data;

#1

53

if(IR == 8’h55) next_state = execute_add;

else if(IR == 8’hAA) next_state = execute_sub;

else next_state = decode;

r <= 0;

end

execute_add:

begin

R2 <= R1 + R0;

next_state = store;

end

execute_sub:

begin

R2 <= R1 - R0;

next_state = store;

end

store:

begin

tmp_data <= R2;

w <= 0; // to write result back make w <= 1, but next instr gets corrupt

next_state = fetch;

PC <= PC + 1;

end

endcase

assign data = !r & w ? tmp_data : ’hz;

endmodule

54

OUTPUT GRAPH:

13.5

TEST-BENCH

//‘timescale 1ns / 1ps

‘include "instr_exec.v"

module memory(input clk,r, w, input [7:0] PC, inout [7:0] data);

reg [7:0] mem[2:0];

reg [7:0] tmp_data;

initial mem[0] = 8’h55;

initial mem[1] = 8’hAA;

initial mem[2] = 8’h00;

always @ (posedge clk) begin

if (w)

mem[PC] <= data;

end

always @ (posedge clk) begin

55

if (r)

tmp_data <= mem[PC];

end

assign data = tmp_data;

endmodule

module tb_instr_exec(input CLK, RST_N);

reg clk, rst;

wire r,w;

wire [7:0] PC;

wire [7:0] data;

memory M(clk,r,w,PC,data);

processor DUT(clk,rst,data,r,w,PC);

always

begin

clk <= 0;

#5;

clk <= 1;

#5;

end

initial

begin

$dumpfile("xyz.vcd");

$dumpvars;

#100 $finish;

end

initial

begin

rst <= 1;

#20 rst <= 0;

end

endmodule

56

13.5.1

YOSYS DIAGRAM

57