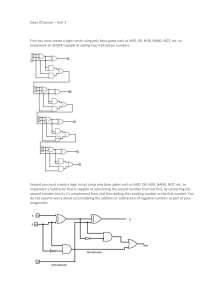

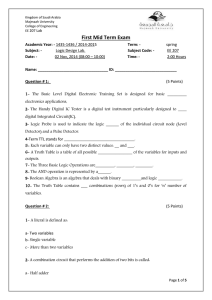

DIGITAL LOGIC DESIGN LAB (EET1211) LAB VI: Construct and Test Various Binary Adder and Subtractor Circuits. Siksha ‘O’ Anusandhan Deemed to be University, Bhubaneswar Name Registration No. Signature Marks: ______/10 Remarks: Teacher’s Signature I. OBJECTIVE: 1. Design, construct and test a Full Adder circuit. 2. Design, construct, and test a Half_Subtractor circuit using two ICs, 7486(XOR) and 7400(NAND). 3. Design, construct, and test a 2 bit Parallel Adder circuit. II. PRE-LAB For Obj. 1: a. Draw the circuit diagram for the function F. b. Obtain the truth table for all input combinations. For Obj. 2: a. Draw the circuit diagram for the function F. b. Obtain the truth table for all input combinations For Obj. 3: a. Draw the circuit diagram for the function F. b. Obtain the truth table for all input combinations III. LAB: Components Required: S. No Name of the Component Specification Quantity Observation: Conclusion: IV. POST LAB: 1. A Half-adder is characterized by a. Two inputs and two outputs b. c. Two inputs and three outputs d. Three inputs and two outputs Two inputs and one outputs 2. A 4-bit parallel adder can add a. Two 4-bit binary numbers c. Four bits at a time Two 2-bit binary number Four bits at a time b. d. 3. Two four bit numbers can be added using two full adders. Yes or No? Justify answer.