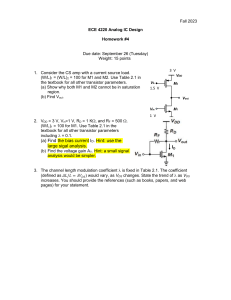

CMOS Comparators Offset Chapter 10 Figure 2 Chapter 10 Figure 03 • Finite mismatch in the input pair lead to input-referred offset in any differential amplifier or comparator • Offset can be cancelled by sampling it on a capacitor Offset cancellation • Illustrated here with ideal switches Chapter 10 Figure 6 Practical offset cancellation • MOS switches introduce charge injection Chapter 10 Figure 7 Fully-differential comparator • Reduces impact of charge injection, common-mode noise, etc. Chapter 10 Figure 10 Use of opamps as a comparator t Chapter 10 Figure 2 Chapter 10 Figure 4 • Opamps compensated for closed-loop stability have a slow dominant pole • Example 10.2: time constant of the amplifier is t = 1/2p1kHz = 0.16ms Opamps are slow when operated open-loop Speed-up of opamp • Compensation may be disconnected during open-loop operation • May provide a speedup of 10-100 x Chapter 10 Figure 5 Dynamic Comparators • Dynamic comparators use positive feedback to provide regenerative gain with much higher speed • They generally have less accuracy, more clock kickback, etc. than opamp-based comparators • They can be preceded by a preamplifier to improve their performance Chapter 10 Figure 14 Chapter 10 Figure 15 Dynamic Comparator Operation Chapter 10 Figure 18 Chapter 10 Figure 15 Small-signal model Chapter 10 Figure 16 Need for RS Latch • Dynamic comparators generally have a “Reset” phase to minimize hysteresis • Many applications will require them to be followed by a second latch stage that maintains the logic levels during the reset phase • Example: dynamic latch on the right • When Vltch is low, both Vout+ and Voutare pulled up high Chapter 10 Figure 19 Example RS Latches S VDD Q VDD VDD VDD Outp R Q A Outn A B O'Mahony, F. et al, "A 47 10 Gb/s 1.4 mW/Gb/s Parallel Interface in 45 nm CMOS," JSSC Dec. 2010 B Typical Dynamic Comparator Architecture Clock PreAmp Input Regenerative Positive-Feedback Latch Reference (sometimes) RS Latch Output Key Specifications • Energy consumed per comparison • Systematic offset • Hysteresis • Random offset • Input sensitivity • Comparator input-referred noise Energy per comparison IDD • Power consumption @ fclk: P = VDDIDD • For a dynamic comparator, one expects: P = fclk CeffVDD2 + Pstatic • Pstatic may include: fclk • Static power consumed in any preamplification stages • Leakage • Bias circuitry • Energy per conversion: Econv = Energy per sec / conv. per second = P / fclk • Assuming dynamic power dominates, we expect this to be relatively constant: Econv = CeffVDD2 • Worst case will likely be at small input amplitudes (due to longer regeneration period) and toggling outputs (to maximize dynamic activity on all nodes) D Vin VDD D Q Q Vout Offset & Hysteresis • Vin is a slow ramp • the comparator is being continuously clocked We expect the output to toggle on the first clock cycle after Vin crosses zero • If this doesn’t happen, the input voltage required to toggle the output is the offset • If the offset so observed is different when the input is increasing and decreasing, then • Offset is the average of the two • Hysteresis is the difference fclk Vin D Q D Q Vout Vout Hysteresis Observed with Vin increasing Observed with Vin decreasing • Hysteresis may be caused by: • Incomplete reset of the dynamic latch • Memory in the RS latch Voffset Vin Random Offset • Repeating the experiment over many Monte Carlo runs will yield a Gaussian distribution of offset observations • The mean offset observed is “systematic” offset; e.g. approximately -40mV on the right • Caused by asymmetries in the design, including layout parasitics • The standard deviation of the observed comparator offsets is caused by random mismatch fclk Vin D Q D Q Vout Sensitivity • When the input is very near the comparator’s trip point, it may take a long time before regeneration is complete • If the time to complete regeneration exceeds the clock period, the comparator is not able to resolve the input • Extreme case is when the output never resolves “Metastability” “Metastability” Chapter 10 Figure 18 fclk Input-referred noise • When the input voltage is precisely set to the comparator trip point, noise will sometimes cause the comparator output to resolve high, sometimes low • Repeating the exercise many times can provide statistical data to which may be fit a Gaussian distribution • The standard deviation of the Gaussian is the comparator’s input-referred rms noise • One must be careful to avoid the impact of input offset & hysteresis Vin (small) D D Chapter 10 Figure 1 Q Q Vout