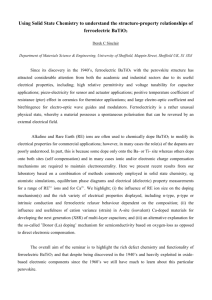

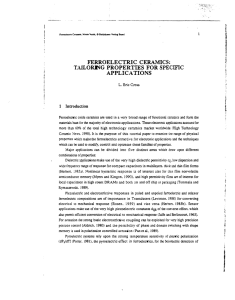

Journal of ELECTRONIC MATERIALS, Vol. 48, No. 10, 2019 https://doi.org/10.1007/s11664-019-07483-1 Ó 2019 The Minerals, Metals & Materials Society Effect of Ferroelectric Thickness Variation in Undoped HfO2-Based Negative-Capacitance Field-Effect Transistor BHASKAR AWADHIYA ,1,2 PRAVIN N. KONDEKAR,1,3 and ASHVINEE DEO MESHRAM1,4 1.—Nano-Electronics and VLSI Lab, Electronics and Communication Engineering Department, Indian Institute of Information Technology, Design and Manufacturing, Jabalpur 482005, India. 2.—e-mail: bhaskar.a@iiitdmj.ac.in. 3.—e-mail: pnkondekar@iiitdmj.ac.in. 4.—e-mail: 1612304@iiitdmj.ac.in Negative-capacitance field-effect transistors (NCFETs) are emerging devices which have shown huge potential to replace classical field-effect transistors because of their steep switching characteristic enabled by a ferroelectric stack. The negative capacitance in ferroelectrics results in a voltage step-up action which curtails the subthreshold swing below 60 mV/dec. The ferroelectric thickness is a key design parameter which governs the operation of such devices and resulting circuits. We examine herein for the first time the effect of the ferroelectric thickness of undoped HfO2-based negative-capacitance fieldeffect transistors on the device and circuit performance. Increasing the ferroelectric thickness yields higher gain but with increased probability of hysteresis. Also, depending upon the properties of the underlying transistor, at low overdrive voltage, increase in the ferroelectric thickness beyond a certain value may introduce a loss of saturation (negative differential resistance) in the drain characteristic of the NCFET. Also, we design an NCFET-based resistive load inverter and study the effect of thickness variation on the circuit performance. The results of the analysis show that increasing the thickness within a permissible limit increases the noise margin and reduces the power dissipation of the designed circuit. Key words: Negative-capacitance field-effect transistor (NCFET), negative differential resistance (NDR), ferroelectric–dielectric (FE–DE), subthreshold swing (SS) INTRODUCTION Scaling in conventional transistors has helped improve their switching speed, packing density, and cost. Despite all these advantages, it has instigated problems related to short-channel effects, high power dissipation, and increased leakage current of such device, deteriorating the ION =IOFF ratio of transistors. As the gate length of a transistor is reduced, the supply voltage ðVDD Þ and threshold voltage ðVTH Þ must be decreased proportionally to keep the overdrive ðVDD VTH Þ high. As a (Received January 19, 2019; accepted July 24, 2019; published online August 6, 2019) 6762 consequence, the leakage current ðIOFF Þ of the transistor starts to rise exponentially. Thus, to maintain the balance between overdrive and leakage current, the subthreshold swing of the transistor needs to be lowered. However, thermodynamics dictates that the subthreshold swing of a conventional metal–oxide–semiconductor field-effect transistor (MOSFET) is restricted by Boltzmann tyranny,1 which means that it is not possible to curtail the subthreshold swing below 60 mV/dec. This limitation in the subthreshold swing occurs because of current transport phenomena, which involves thermionic injection of electrons2–4 over the barrier. The subthreshold swing of MOSFETs cannot be scaled below 60 mV/dec, even if Cox tends to 1. There are two approaches to reduce the Effect of Ferroelectric Thickness Variation in Undoped HfO2-Based Negative-Capacitance Field-Effect Transistor subthreshold swing. The first is to modify the transport factor, i.e., the current transport phenomena in the channel. The tunnel field-effect transistor (TFET)5,6 and green transistors7 use the band-toband tunneling8 approach to reduce the subthreshold swing below 60 mV/dec, whereas the impactionization MOS technique9 uses impact ionization to achieve the same. However, the biggest disadvantage with tunnel field-effect transistors is that they suffer from the problem of low ON-current and ambipolarity, whereas the operating voltage for IMOS technology is very high. The second approach is to modify the body factor, i.e., reduce it to less than 1. This can be achieved by using nanoelectromechanical (NEM) relay devices10–12 or negativecapacitance field-effect transistors.13–15 In NEM relay devices, the point of instability between a mechanical and electrical force is utilized to obtain a supersteep subthreshold swing. However, these devices suffer from limitations in terms of voltage scaling and reliability. Negative-capacitance fieldeffect transistors utilize the property of negative capacitance16–21 to modify the body factor and hence achieve (SS) subthreshold swing below 60 mV/dec. An NCFET can be thought of as a baseline MOSFET having an external amplifier at the input of the gate terminal, which means that it does not alter the transport physics in the MOSFET and hence can benefit from all future material research aimed at improving the channel transport. It should be kept in mind that the ferroelectric thickness22 and temperature23 are important design parameters for NCFETs. Increasing the ferroelectric thickness results in a decrease of the ferroelectric capacitance, which in turn increases the amplification factor of the NCFET. However, it should be kept in mind that the NCFET becomes prone to negative differential resistance at higher ferroelectric thickness and lower gate bias, as discussed below. BASICS OF NCFET An NCFET can be considered as a classical FET with a passive gate voltage amplifier. It includes an additional ferroelectric oxide layer above the dielectric oxide, as shown in Fig. 1a. The ferroelectric oxide layer is considered as a capacitor connected in series with a classical FET. The ferroelectric capacitor is modeled as a voltage-dependent source, which is a function of the gate charge. All the simulation results presented herein are obtained by incorporating the parameters for undoped HfO2 into an existing model, available at nanoHUB. Amalgamating the BSIM424 model for a classical MOSFET and the Landau–Khalatnikov theory of negative capacitance25 in ferroelectrics results in the NCFET model. The dynamics of the ferroelectric can be explained by the Landau–Khalatnikov equation,26,27 which can be expressed as a charge versus voltage equation as shown in Eq. 1: 6763 Fig. 1. (a) Schematic of 32-nm NCFET. (b) Equivalent capacitor model of NCFET. VF ¼ aQF þ bQ3F þ cQ5F þ q dQF ; dt ð1Þ where q is a constant which depends on the ferroelectric material and the amplitude of the applied voltage16 and a, b, and c are anisotropy constants for ferroelectric materials. A schematic and capacitor model of a 32-nm NCFET are shown in Fig. 1a and b, respectively. From the capacitance model, an expression for VMOS (under steady state and when the ferroelectric is operating in the negative-capacitance region) can be written as VMOS ¼ AG ¼ VG ð2Þ VMOS ¼ AG VG þ AD VD ; ð3Þ jCF j ; jCF j CMOS þ jC VD ; 1 CMOS jCF j F jCMOS AD ¼ CD CD ; jCF j CMOS ð4Þ where AG and AD are the amplification factor and drain coupling factor, respectively. For nonhysteretic operation of an NCFET, jCF j CMOS must 6764 Awadhiya, Kondekar, and Meshram be greater than zero across the full span of operating bias.28 This leads to the requirements that AG > 0 and AD < 0. It is worth noting that an increase in the ferroelectric thickness increases the total capacitance of the MOSFET by a factor of AG . Hence, the total capacitance of an NCFET is greater than that of a conventional MOSFET, which may increase the delay if the damping constant is not properly optimized.29 Also, an increase in the ferroelectric thickness beyond a critical value introduces hysteresis30 and sometimes nonvolatility.31 Hence, it is advisable to maintain the thickness of the ferroelectric oxide below this critical thickness.32 The ferroelectric thickness at which jCF j becomes equal to CMOS is termed the critical thickness. Increasing tFE beyond tC introduces hysteresis into the device characteristics, where 2 Q0 : tC ¼ pffiffiffi 3 3 EC CMOS ð5Þ The critical thickness ðtC Þ is dependent on the total gate capacitance ðCMOS Þ associated with the underlying transistor and the properties of the ferroelectric material. Recent studies have shown ferroelectric behavior in doped HfO2,33 but here we consider undoped HfO2 as the ferroelectric material. Undoped HfO2, when deposited using physical vapor deposition (PVD), shows dielectric behavior, but when deposited using chemical vapor deposition (CVD) it shows ferroelectric behavior; using undoped HfO2 makes the deposition process easier and hence simplifies the process control. The remanent polarization ðPR Þ and coercive field ðEC Þ are considered to be 10 lC/cm2 and 1000 kV/cm, respectively,34,35 while the value of the anisotropy constant is obtained using the following relation mentioned in Ref. 36: pffiffiffi pffiffiffi 3 3 VC 3 3 VC and b ¼ ; ð6Þ a¼ 2 QO 2 Q3O where VC ¼ EC tFE is the coercive voltage and QO ¼ PR A is the remanent charge. DEVICE ANALYSIS To explain the operation of NCFET-based circuits, the device characteristics and their dependence on the ferroelectric thickness must be discussed. We study herein the VMOS –VG characteristics of NCFETs with different ferroelectric thicknesses, as shown in Fig. 2a. As the ferroelectric thickness is increased, VMOS becomes greater than VG due to the negative capacitance in the ferroelectric oxide. After exceeding the critical thickness, i.e., tFE ¼ 10 nm, hysteresis can be observed in the VMOS versus VG characteristic of the NCFET. Figure 2b shows the VFE –VG characteristics of NCFETs with different ferroelectric thicknesses, where VFE ¼ VG VMOS . As the thickness of the ferroelectric is increased, VFE starts decreasing and goes negative. After exceeding the critical thickness, hysteresis can be observed in the VFE –VG characteristic of the NCFET. Figure 2c shows the AG –VG characteristics of the NCFET, where AG ¼ @VMOS =@VG . Increasing the ferroelectric thickness increases the amplification factor up to 10 nm, after which hysteresis starts to appear in the internal voltage amplification characteristics. Figure 2d and e show the ID – VG and log ID –VG characteristics for the NCFET, respectively. It is clearly visible that, as tFE increases, the ON-current increases and the switching characteristic becomes steeper, because of the voltage amplification contributed by the ferroelectric oxide layer. Increase in the ON-current enhances the ION =IOFF for the NCFET, as presented explicitly in Table I. Figure 2f shows the subthreshold swing versus gate voltage characteristic of the NCFET. It is apparent that increasing the ferroelectric thickness (up to the critical thickness) reduces the SS of the device. Furthermore, the expression for the subthreshold swing37 of the NCFET is shown below, obtained using an equivalent capacitor model of the NCFET: Cdep 60 mV 1 1þ : ð7Þ SSNCFET ¼ dec AG Cox The results presented above clearly indicate the occurrence of hysteresis at tFE ¼ 15 nm, hence only results for ferroelectric thicknesses up to 10 nm are discussed below. Figure 3a shows the g0m –VG characteristics for the NCFET. The transconductance is defined as the variation in the drain current with respect to a variation in the gate voltage. Increasing the ferroelectric thickness leads to an increase in the amplification factor and hence the transconductance of the NCFET. An expression for the transconductance of the NCFET is shown in Eq. 8, clearly showing that the transconductance of the NCFET is greater than that of a MOSFET by a factor of AG . g0m ¼ @ID @ID @VMOS ¼ ¼ gm AG ; @VG @VMOS @VG ð8Þ where gm is the transconductance of the internal MOSFET, g0m is the transconductance of the NCFET, and AG is the amplification factor of the NCFET. Figure 3b shows the g0m2 –VG characteristics for the NCFET. The second-order transconductance is defined as the second-order variation in the drain current with respect to a variation in the gate voltage. The second-order transconductance of the NCFET is A2G times greater than that of the MOSFET, as seen from Eq. 9. @ 2 ID @ 2 ID @VMOS 2 g0m2 ¼ ¼ ¼ gm2 A2G ; ð9Þ 2 @VG @VG2 @VMOS Effect of Ferroelectric Thickness Variation in Undoped HfO2-Based Negative-Capacitance Field-Effect Transistor 6765 Fig. 2. (a) Variation of VMOS with VG for different values of tFE . (b) Variation of VFE with VG for different values of tFE . (c) Variation in internal voltage amplification ð@VMOS =@VG Þ with VG for different values of tFE . (d) ID –VG characteristics on linear scale for different values of tFE . (e) ID –VG characteristics on logarithmic scale for different values of tFE . (f) Subthreshold swing (SS) as a function of gate voltage ðVG Þ for different values of tFE . Table I. Threshold voltage and ON/OFF-current ratio with thickness variation in NCFET NCFET tFE tFE tFE tFE = = = = 0 nm 5 nm 10 nm 15 nm VTH (V) ION/IOFF 0.27 0.26 0.25 Hysteresis 5640.4 11063 17642 Hysteresis where gm2 is the second-order transconductance of the internal MOSFET, g0m2 is the second-order transconductance of the NCFET. The gate voltage at which the peak value of the second-order transconductance is obtained is the threshold voltage.38 The threshold voltage of the NCFET with different ferroelectric thicknesses is presented explicitly in Table I. Increasing the ferroelectric thickness leads to a leftwards shift of the peak value of the transconductance at lower gate bias, 6766 Awadhiya, Kondekar, and Meshram in VD , as seen in Fig. 5a. Hence, the current reduces with a positive incremental change in VD , thus the output characteristic exhibits negative differential resistance (NDR), primarily originating because of the dependence of the drain bias ðVD Þ with internal node bias ðVMOS Þ through the drain capacitance ðCD Þ. 2.2. For VOV ¼ 0:4 V, AG VG is the dominant factor and nullifies the effect of AD VD , hence an increase in VD leads to a small decrement in VMOS , as seen in Fig. 5b. Hence, NDR is not observed and the current saturation phenomenon is observed in the drain characteristics of the NCFET. 2.3. For VOV ¼ 0:9 V, AG VG becomes dominant and hence VMOS shows an even weaker dependence on VD , as seen in Fig. 5c, hence VMOS becomes large enough to impact VDSAT significantly. In general, VDSAT can be expressed as ðVMOS VTH Þa where a is an exponent that depends on the nature of the current saturation mechanism in the transistor,39 lying between 1 and 2. For larger values of a, as in the MOSFET case, it is observed that, for VOV ¼ 0:9 V, the current saturation phenomenon is observed. However, for even large values of VOV , VDSAT will exceed VDD , hence ID will fail to saturate. 0 0 Fig. 3. (a) gm –VG characteristics for different values of tFE . (b) gm2 – VG characteristics for different values of tFE . indicating a reduction in the threshold voltage with increasing ferroelectric thickness. However, when exceeding the critical thickness, hysteresis appears in the transfer characteristics, hence the threshold voltage estimation, in this case, is trivial. Figure 4a, b, and c show the ID –VD output characteristic of the NCFET at VOV ¼ 0:1 V, 0.4 V, and 0.9 V, respectively. Further discussion on the drain characteristics of the NCFET is presented below: 1. 2. At tFE ¼ 5 nm, jCF j dominates over CD , hence the amplification factor ðAG Þ will be dominant over the drain coupling factor ðAD Þ, so the internal node voltage is more dependent on the gate bias, thus the ID –VD behavior of the NCFET at lower ferroelectric thickness is similar to that of the baseline FET tFE ¼ 0 nm with larger ON-current, which is due to the voltage amplification effect. At tFE ¼ 10 nm; jCF j decreases and becomes comparable to CD , hence the amplification factor is comparable to the drain coupling factor, so the relative values of VD and VG control VMOS : 2.1. For VOV ¼ 0:1 V, AD VD dominates over AG VG , hence VMOS decreases with increase Figure 4d, e, and f show the g0ds –VD characteristics of the NCFET at VOV ¼ 0:1 V, 0.4 V, and 0.9 V, respectively. Further discussion on the g0ds –VD characteristics of the NCFET is presented below: 3. 4. At tFE ¼ 5 nm, g0ds decreases with increase in VD , therefore g0ds attains a small and positive value at higher value of VD , which is because of the saturation of the drain current with respect to VD . At tFE ¼ 10 nm, the behavior of the g0ds –VD characteristic is strongly dependent on the overdrive voltage in the NCFET. 4.1. For VOV ¼ 0:1 V, negative output conductance can be observed, which is caused by the negative differential resistance40 in the drain characteristics of the NCFET. A negative value of g0ds can also be described by a large negative value of the drain coupling factor ðAD Þ, as shown in Fig. 5d. 4.2. For VOV ¼ 0:4 V, g0ds decreases with an increase in the drain voltage. Furthermore, at higher value of VD , g0ds saturates, mainly because of the saturation in the drain characteristics of the NCFET. Also, the drain coupling factor ðAD Þ has a small negative value, as seen in Fig. 5e. Effect of Ferroelectric Thickness Variation in Undoped HfO2-Based Negative-Capacitance Field-Effect Transistor 6767 Fig. 4. (a) ID –VD characteristics with VOV ¼ 0:1 V for different values of tFE . (b) ID –VD characteristics with VOV ¼ 0:4 V for different values of tFE . 0 0 –VD characteristics with VOV ¼ 0:1 V for different values of tFE . (e) gds – (c) ID –VD characteristics with VOV ¼ 0:9 V for different values of tFE . (d) gds 0 –VD characteristics with VOV ¼ 0:9V for different values of tFE . VD characteristics with VOV ¼ 0:4 V for different values of tFE . (f) gds 4.3. For VOV ¼ 0:9 V, g0ds decreases with increase in VD . Furthermore, at VD ¼ 0:9 V, g0ds saturates, mainly because of the saturation in the drain characteristics. However, further increase in VOV may lead to nonsaturation in the g0ds –VD characteristic and g0ds decreases monotonically with an increase in VD . Also, the drain coupling factor ðAD Þ has an even smaller negative value, as seen in Fig. 5f. ANALYSIS OF NCFET-BASED RESISTIVE LOAD INVERTER Figure 6a and b show a schematic and the transfer characteristic of a resistive load inverter with RD ¼ 10k X. The voltage amplification ðAG Þ provided by the ferroelectric oxide enables steep switching in the voltage transfer characteristic of the resistive load inverter. Also, at tFE ¼ 5 nm and 10 nm, the gain of the NCFET increases, which in 6768 Awadhiya, Kondekar, and Meshram Fig. 5. (a) VMOS –VD characteristics with VOV ¼ 0:1 V for different values of tFE . (b) VMOS –VD characteristics with VOV ¼ 0:4 V for different values of tFE . (c) VMOS –VD characteristics with VOV ¼ 0:9 V for different values of tFE . (d) AD –VD characteristics with VOV ¼ 0:1 V for different values of tFE . (e) AD –VD characteristics with VOV ¼ 0:4 V for different values of tFE . (f) AD –VD characteristics with VOV ¼ 0:9 V for different values of tFE . turn increases the noise margin and hence provides better noise immunity to the circuit. The noise margin of a circuit is defined as its ability to endure noise without triggering fictitious changes in the output voltage. It is a quantitative measure of the noise immunity of the circuit. The noise margin can be computed from the dVout =dVin versus Vin characteristic of the resistive load inverter, which is shown in Fig. 6c. The applied input biases at which the slope of the voltage transfer characteristic is equal to 1 ðdVout =dVin ¼ 1Þ are VIH and VIL . Also, the value of the output at these points is VOL and VOH , respectively. The obtained values of VIH ; VIL ; VOH ; VIL ; NMH , and NML for tFE ¼ 0:5 and 10 nm are presented in Table II. NMH ¼ VOH VIH ; ð10Þ NML ¼ VIL VOL ; ð11Þ where NMH is the noise margin high and NML is the noise margin low. At tFE ¼ 5 nm and 10 nm, the Effect of Ferroelectric Thickness Variation in Undoped HfO2-Based Negative-Capacitance Field-Effect Transistor 6769 Fig. 6. (a) Schematic of NCFET-based inverter. (b) Voltage transfer characteristics of NCFET-based inverter. (c) Voltage gain ð@Vout =@Vin Þ versus Vin characteristics of NCFET-based inverter. (d) DC power consumption of NCFET-based inverter. Table II. Noise margin for resistive load inverter Parameter VIH (V) VIL (V) VOH (V) VOL (V) NMH (V) NML (V) 42.4% less compared with the MOSFET-based resistive load inverter ðtFE ¼ 0 nm). tFE = 0 nm tFE = 5 nm tFE = 10 nm CONCLUSIONS 0.4073 0.1215 0.8531 0.0671 0.4458 0.0543 0.2956 0.0984 0.8760 0.0433 0.5804 0.0551 0.1858 0.0894 0.8750 0.0337 0.6892 0.0557 We explore the effect of FE thickness variation on the characteristics of undoped HfO2-based NCFET devices and resulting circuits. The results clearly indicate that an increase in the ferroelectric thickness may lead to hysteresis in the transfer characteristic, which limits increase of the thickness beyond a critical value. Also, an increase in the thickness introduces NDR into the output characteristics of the NCFET at low overdrive voltage, which is responsible for a negative value of the output conductance in the g0ds –VD characteristics. The VMOS –VD and AD –VD characteristics of the NCFET are further discussed to provide understanding of the erratic behavior of the drain characteristics of the NCFET at different overdrive voltages. A resistive load inverter is designed using the NCFET, and its noise margin and power dissipation evaluated. It is observed that the NCFET-based circuit shows high immunity to noise, hence having a higher noise margin. Also, the noise margin high and noise margin low for the NCFET-based resistive load inverter have higher values compared with the NCFET-based resistive load inverter with tFE ¼ 0 nm. It is also observed that the resistive load inverter using the NCFET shows decreased leakage power. The results shown in Fig. 6d indicate a decrease in the leakage power for the NCFET-based resistive load inverter. For VIN ¼ 0 V, the NCFET-based resistive load inverters with tFE ¼ 5 nm and 10 nm exhibit leakage of 0.2247 lW and 0.1708 lW, respectively. Also the power dissipation for the NCFET-based resistive load inverter at tFE ¼ 5 nm and 10 nm is 24.6% and 6770 Awadhiya, Kondekar, and Meshram NCFET-based circuit consumes less power compared with the conventional MOSFET circuit. ACKNOWLEDGMENTS 20. The authors would like to thank Dr. Muhammad Abdul Wahab (Intel Corporation) and Prof. Muhammad Ashraful Alam (Purdue University) for providing the NCFET model available at nanoHUB. 21. 23. REFERENCES 24. 1. V.V. Zhirnov and R.K. Cavin, Nat. Nanotechnol. 3, 2 (2018). 2. M.S. Lundstrom, in 2006 IEEE International SOI Conference Proceedings, pp. 1–3 (2006). 3. S.M. Sze, Physics of Semiconductor Devices, 1st ed. (New York: Wiley, 1969). 4. A.M. Ionescu and H. Riel, Nature 479, 7373 (2011). 5. K. Boucart and A.M. Ionescu, IEEE Trans. Electron Devices. 54, 7 (2007). 6. A.C. Seabaugh and Q. Zhang, in Proc. IEEE, pp. 2095–2110 (2010). 7. K. Jeon, W.Y. P. Loh, C.Y. Patel, J. Kang, A. Oh, C. Bowonder, C.S. Park, C. Park, P. Smith, H.H. Majhi, R. Tseng, T.S.K. Jammy, T. Liu and C. Hu, in 2010 Symposium on VLSI Technology, pp. 121–122 (2010). 8. C. Zener, in Proceedings of Royal Society: A Mathematical, Physical, and Engineering Sciences, pp. 523–529 (1935). 9. K. Gopalakrishnan, P.B. Griffin, and J.D. Plummer, in Digest International Electron Devices Meeting, pp. 289–292 (2002). 10. N. Abele, R. Fritschi, K. Boucart, F. Casset, P. Ancey, and A.M. Ionescu, in IEEE International Electron Devices Meeting, 2005. IEDM Technical Digest, pp. 479–481 (2015). 11. F. Chen, H. Kam, D. Markovic, T.-J. K. Liu, V. Stojanovic, and E. Alon, in 2008 IEEE/ACM International Conference on Computer-Aided Design, pp. 750–757 (2008). 12. V. Pott, H. Kam, R. Nathanael, J. Jeon, E. Alon, and T.-J. King Liu, in Proc. IEEE, pp. 2076–2094 (2010). 13. G. Pahwa, T. Dutta, A. Agarwal, S. Khandelwal, S. Salahuddin, C. Hu, and Y.S. Chauhan, IEEE Trans. Electron Devices 63, 12 (2016). 14. S. Gupta, M. Steiner, A. Aziz, V. Narayanan, S. Datta, and S.K. Gupta, IEEE Trans. Electron Devices 64, 8 (2017). 15. A.I. Khan, U. Radhakrishna, S. Salahuddin, and D. Antoniadis, IEEE Electron Device Lett. 38, 9 (2017). 16. A.I. Khan, K. Chatterjee, B. Wang, S. Drapcho, L. You, C. Serrao, S.R. Bakaul, R. Ramesh, and S. Salahuddin, Nat. Mater. 14, 2 (2015). 17. G. Catalan, D. Jiménez, and A. Gruverman, Nat. Mater. 14, 2 (2015). 18. A.I. Khan, D. Bhowmik, P. Yu, S.J. Kim, X. Pan, R. Ramesh, and S. Salahuddin, Appl. Phys. Lett. 99, 11 (2011). 19. P.N. Kondekar and B. Awadhiya, in 2017 Joint IEEE International Symposium on the Applications of Ferroelec- 22. 25. 26. 27. 28. 29. 30. 31. 32. 33. 34. 35. 36. 37. 38. 39. 40. tric (ISAF)/International Workshop on Acoustic Transduction Materials and Devices (IWATMD)/Piezoresponse Force Microscopy (PFM), Atlanta, GA, (2017), pp. 45–47. H. Mehta and H. Kaur, Superlattices Microstruct. 111 (2017). H. Mehta and H. Kaur, IEEE Trans. Electron Devices 65, 2699 (2018). B. Awadhiya, P.N. Kondekar, and A.D. Meshram, Micro Nano Lett. 13, 10 (2018). B. Awadhiya, P.N. Kondekar, and A.D. Meshram, Superlattices Microstruct. 123, 306 (2018). BSIM Group in UC Berkeley. http://wwwdevice.eecs.berkele y.edu/bsim/?page=BSIM4. D.J.R. Appleby, N.K. Ponon, S.K.K. Kwa, B. Zou, P.K. Petrov, T. Wang, N.M. Alford, and A. O’Neill, Nano Lett. 14, 7 (2014). L.D. Landau and I.M. Khalatnikov, in Collected Papers, L.D. Landau, Elsevier, pp. 626–629 (1965). T.K. Song, J. Korean Phys. Soc. 46, 1 (2005). C. Hu, S. Salahuddin, C.-I. Lin, and A. Khan, in 2015 73rd Annual Device Research Conference (DRC), pp. 39–40 (2015). Y. Li, K. Yao, and G.S. Samudra, IEEE Trans. Electron Devices 64, 5 (2017). A. Aziz, S. Ghosh, S. Datta, and S.K. Gupta, IEEE Electron Device Lett. 37, 6 (2016). S. George, S. Gupta, V. Narayanan, K. Ma, A. Aziz, X. Li, A. Khan, S. Salahuddin, M.F. Chang, S. Datta and J. Sampson, in Proceedings of the 53rd Annual Design Automation Conference on—DAC’16, pp. 1–6 (2016). S. Salahuddin and S. Datta, Nano Lett. 8, 2 (2008). J. Müller, P. Polakowski, S. Mueller, and T. Mikolajick, ECS J. Solid State Sci. Technol. 4, 5 (2015). P. Polakowski and J. Muller, Appl. Phys. Lett. 106, 23 (2015). K.D. Kim, M.H. Park, H.J. Kim, Y.J. Kim, T. Moon, Y.H. Lee, S.D. Hyun, T. Gwon, and C.S. Hwaung, J. Mater. Chem. C 4, 28 (2016). A.I. Khan, U. Radhakrishna, K. Chatterjee, S. Salahuddin, and D.A. Antoniadis, IEEE Trans. Electron Devices 63, 11 (2016). L. Tu, X. Wang, J. Wang, X. Meng, and J. Chu, Adv. Electron. Mater. 4, 11 (2018). A. Ortiz-Conde, F.J. Garcıa Sánchez, J.J. Liou, A. Cerdeira, M. Estrada, and Y. Yue, Microelectron. Reliab. 42, 4 (2002). T. Sakurai and A.R. Newton, IEEE J. Solid State Circ. 25, 2 (1990). H. Mehta and H. Kaur, IEEE Trans. Electron Devices 66, 7 (2019). Publisher’s Note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.