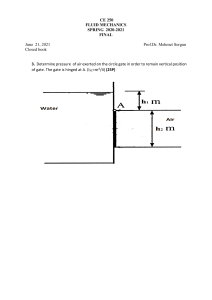

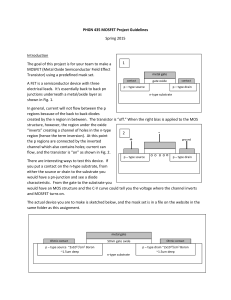

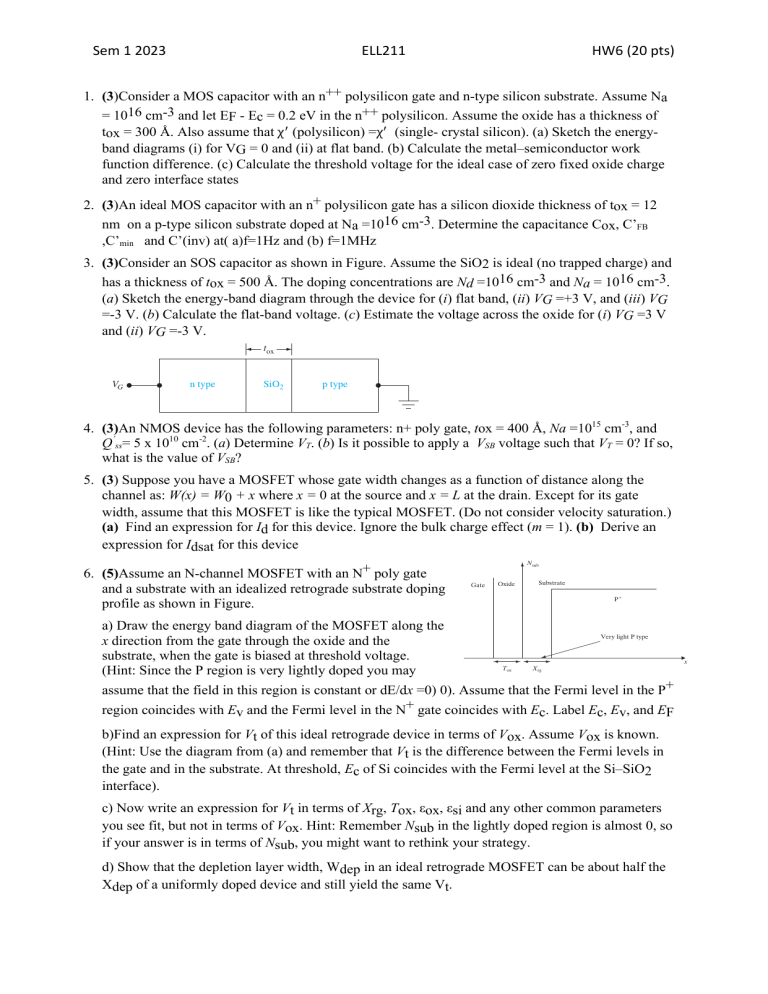

436 charge distribution !(x) in the oxide is given by ! t x!(x) 1 _ 'VFB # $ _ dx Cox 0 tox ox 10.26 Sem Using 1 the2023 results of Problem 10.25, calculate the shift in flELL211 at-band voltage for HW6 (20 pts) tox # 20 nm # 200 Å for the following oxide charge distributions: (a) Q %ss # 8 & 1010 cm$2 is entirely located at the oxide–semiconductor interface, $2 Q ss% # 8 & 1010a cm is capacitor uniformly distributed the oxide, andand n-type silicon substrate. Assume Na ++ polysilicon 1.(b)(3)Consider MOS with an nthroughout gate 10 $2 (c) Q ss% # 8 & 10 cm forms a triangular distribution with the peak at the oxide– = 1016 cm-3 and let - Ecat=the 0.2metal–oxide eV in theinterface. n++ polysilicon. Assume the oxide has a thickness of F zero semiconductor interface andEis ! = 300 Also assume thatbyχusing (polysilicon) =χ!and (singlecrystal silicon). (a) Sketch the energy10.27 Antox ideal MOSÅ. capacitor is fabricated intrinsic silicon an n! polysilicon gate. (a) Sketch the energy-band diagram through the MOS structure under band diagrams (i) for VG = 0 and (ii) at flat band. (b) Calculate the metal–semiconductor work flat-band conditions. (b) Sketch the low-frequency C–V characteristics from function difference. (c) Calculate the threshold voltage for thenegaideal case of zero fixed oxide charge tive to positive gate voltage. and zero interface states 10.28 Consider a MOS capacitor with a p-type substrate. Assume that donor-type onlycapacitor at midgap (i.e., EFin).+Sketch the high-frequency 2.interface (3)An traps idealexist MOS withatan polysilicon gate has aC–V silicon dioxide thickness of tox = 12 Hu_ch07v3.fm 287 Friday, February 13, 2009 4:55 PM curve from accumulation to inversion. Compare this sketch to the ideal C–VPageplot. 16 -3 nm on a p-type silicon substrate doped at N =10 cm . Determine the capacitance Cox, C’FB a 10.29 Consider an SOS capacitor as shown in Figure P10.29. Assume the SiO2 is ideal ,C’ and C’(inv) at( a)f=1Hz and (b) f=1MHz min (no trapped charge) and has a thickness of tox # 500 Å. The doping concentraProblems tions are Nd # 1016 cm$3 and Na # 1016 cm$3. (a) Sketch the energy-band dia3.gram (3)Consider an SOS capacitor as shown in Figure. Assume the SiO is ideal (no trapped charge) and –3 2 through the device for (i) flat band, (ii) VG # !3 V, and (iii) VG # $3(c)V.L = 1 µm, Na = 1E15 cm . –3 µm, N16 a = 1E17 cm (b)has Calculate the flat-band the voltage across the oxide for a thickness of toxvoltage. = 500 (c) Å.Estimate The doping concentrations are(d) NLd= 1=10 cm-3. and Na = 1016 cm-3. Please pay attention to the positions of the curves relative to each other and label all (i)(a) VG Sketch # !3 V the and energy-band (ii) VG # $3 V. diagram (d) Sketchthrough the high-frequency C–V the device forcharacter(i)curves. flat band, (ii) VG =+3 V, and (iii) VG istic curve. ● Trade-off between I and I ● off the on oxide for (i) VG =3 V =-3 V. (b) Calculate the flat-band voltage. (c) Estimate the voltage across 7.4 Does each of the following changes increase or decrease Ioff and Ion? A larger Vt. A and (ii) VG =-3 V. larger L. A shallower junction. A smaller Vdd. A smaller Tox. Which of these changes contribute to leakage reduction without reducing the precious Ion? tox 7.5 There is a lot of concern that we will soon be unable to extend Moore’s Law. In your own words, explain this concern and the difficulties of achieving high Ion and low Ioff. (a) Answer this question in one paragraph of less than 50 words. VG n type SiO2 p type (b) Support your description in (a) with three hand-drawn sketches of your choice. (c) Why is it not possible to maximize Ion and minimize Ioff by simply picking the right values of Tox, Xj, and Wdep? Please explain in your own words. (d) Provide three equations that help to quantify the issues discussed in (c). 7.6 (a) Rewrite Eq. (7.3.4) in a form that does not but contains Vt. Do so by 4. (3)An hasProblem the following tox = 400 Å, Na =1015contain cm-3W,depand FigureNMOS P10.29 device | Figure for 10.29. parameters: n+ poly gate, using Eqs. (5.5.1) and (5.4.3) assuming that Vt is given. ’ 10 -2 Q ss= 5 x 10 cm . (a) Determine VT. (b) Is it possible to apply a VSB voltage that If taken so, to reduce the T = 0? (b) Based on the answer tosuch (a), state what V actions can be minimum acceptable channel length. what is the value of VSB? 7.7 (a) What is the advantage of having a small Wdep? given L and Vt, what is the impact of reducing Wdep on Idsat and gate? (Hint: 5. (3) Suppose you have a MOSFET whose gate width changes (b)as For a function of distance along the consider the “m” in Chapter 6) channel as: W(x) = W0 + x where x = 0 at the source and x =Discussion: L at the drain. forbecause its gate it is more important to be able Overall, smallerExcept Wdep is desirable to suppress Vt roll-off so that L can be scaled. width, assume that this MOSFET is like the typical MOSFET. (Do not consider velocity saturation.) ● MOSFET with Ideal Retrograde Doping Profile ● (a) Find an expression for Id for this device. Ignore the bulk chargeN-channel effectMOSFET (mPM =with 1).an(b) Derive an 12:40 7.8 Assume an 12/11/10 N+ poly gate and a substrate with an idealized retrograde substrate doping profile as shown in Fig. 7–23. expression for Idsat for this device 6. (5)Assume an N-channel MOSFET with an N+ poly gate and a substrate with an idealized retrograde substrate doping profile as shown in Figure. Nsub Gate Oxide Substrate P! a) Draw the energy band diagram of the MOSFET along the Very light P type x direction from the gate through the oxide and the substrate, when the gate is biased at threshold voltage. T X (Hint: Since the P region is very lightly doped you may FIGURE 7–23 assume that the field in this region is constant or dE/dx =0) 0). Assume that the Fermi level in the P+ region coincides with Ev and the Fermi level in the N+ gate coincides with Ec. Label Ec, Ev, and EF ox rg b)Find an expression for Vt of this ideal retrograde device in terms of Vox. Assume Vox is known. (Hint: Use the diagram from (a) and remember that Vt is the difference between the Fermi levels in the gate and in the substrate. At threshold, Ec of Si coincides with the Fermi level at the Si–SiO2 interface). c) Now write an expression for Vt in terms of Xrg, Tox, εox, εsi and any other common parameters you see fit, but not in terms of Vox. Hint: Remember Nsub in the lightly doped region is almost 0, so if your answer is in terms of Nsub, you might want to rethink your strategy. d) Show that the depletion layer width, Wdep in an ideal retrograde MOSFET can be about half the Xdep of a uniformly doped device and still yield the same Vt. x 287