CSR5301

Introduction to Semiconductor Design: Part I – Digital Logic

Fall 2023

Homework Assignment 1

Due on 2023/10/13 23:59

(Provide your intermediate results with the final answer to get the scores.)

1. (20%) The signed 2’s complement representation of a number with a fractional part is the same as that

of an integer except for the different position of the radix point.

For example, suppose (12.3)8 is represented by a 9-bit signed 2’s complement number with its higher

6 bits as the integer part and its lower 3 bits as the fractional part. Convert (12.3)8 to its binary form,

we have (001 010.011)2.

(a) (5%) Convert (43.5)8 to its signed 2’s complement binary form as 𝑥. Consider the same 9-bit

format, i.e., 6-bit integer and 3-bit fractional. Is this format feasible to represent the correct 𝑥?

You must state your reason.

(b) (10%) From now on, let’s consider the 10-bit signed 2’s complement binary form with a 7-bit integer

part and a 3-bit fractional part. Convert the (43.75)10 to its binary form as 𝑦. What is 𝑦? You

must show how you derive the result step by step.

(c) (5%) Perform 𝑧 = (43.5)8 + (43.75)10 with 10-bit binary addition. You must show how you

derive the result step by step. Does the calculation cause an overflow? You must give the reason.

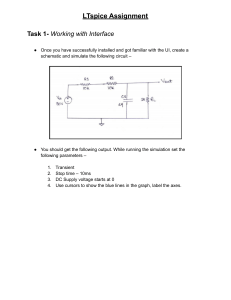

2. (10%) The following design is a logic gate.

(a) (8%) Derive its truth table, which has an output 𝑍 and two inputs, 𝑋 and 𝑌. You must explain

how you derive the result.

(b) (2%) What is this logic gate? Write down its Boolean function. Hint: You may search among the

common logic gates in the lecture notes.

Vdd

!

#

!′

#′

!′

!

#′

#

$

GND

3. (10%) Prove the DeMorgan Theorem (𝑥 ∙ 𝑦)! = 𝑥 ! + 𝑦 ! by using truth tables.

Chih-Tsun Huang

NTHU

1 / 3

CSR5301

Introduction to Semiconductor Design: Part I – Digital Logic

Fall 2023

4. (20%) Draw the logic diagram corresponding to the following Boolean functions directly (you don’t

need to simplify them). You may use two-input or three-input gates of AND, OR, INV, NAND, and NOR.

(a) 𝐹 = 𝐴(𝐵 + 𝐶 + 𝐷)′

(b) 𝐹 = 𝐵𝐶 ! + 𝐴𝐵 + 𝐴𝐶𝐷

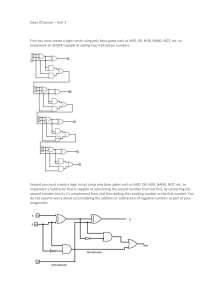

5. (20%) Drive the Boolean functions directly from the following logic diagrams. You don’t need to simplify

the function.

(a) (10%)

A

B

Y

Chapter 2

Boolean Algebra and Logic Gates

(b) (10%)

x

y

F

z

(a) F2 ! x"y"z # x"yz # xy"

6. (20%) Perform the Verilog simulation of the 8-bit Binary Adder.

Hint:

x

Download

hw1_verilog.zip which provides sample Verilog designs and their testbench:

majority_gate.v:

gate-level design of the majority function

y

F2

majority_func.v: functional design of the majority function

majority_t.v: testbench of the majority function using repeat statement to generate all possible

z

input combinations

xy" # x"z

(b) Ffull

2 !adder

full_adder.v: functional design of the

full_adder_t.v:

testbench of the full adder with specific test patterns (four patterns in this example)

FIGURE

2.2

Implementation

Booleandesign

function

withbinary

gates

binary_adder.v:offunctional

of theF28-bit

adder

binary_adder_t.v: testbench of the 8-bit binary adder with four specific test patterns

Refer to the lecture notes to simulate the majority and full adder designs as exercises first.

produce

the

same

truth table,

are equivalent.

the two circuits have the

(a) Visit

EDA

Playground

websitethey

and create

an account:Therefore,

https://www.edaplayground.com

same

outputs

Chih-Tsun

Huang for all possible binary combinations

NTHU of inputs of the three variables. Each 2

circuit implements the same identical function, but the one with fewer gates and fewer

inputs to gates is preferable because it requires fewer wires and components. In general,

there are many equivalent representations of a logic function. Finding the most eco-

/ 3

CSR5301

Introduction to Semiconductor Design: Part I – Digital Logic

Fall 2023

(b) Copy-and-paste the binary adder design and testbench.

Add the fifth test pattern to perform −6 − 13. To do so, you simply insert additional statements in

blue colors as follows:

...

// pattern 4

{a, b, ci} = {8'b00000110, 8'b11110011, 1'b0};

#10

$display("a = %b, b = %b, ci = %b | {co, si} = %b %b", a, b, ci, co, s);

// pattern 5

{a, b, ci} = {the test pattern you want to apply};

#10

$display("a = %b, b = %b, ci = %b | {co, si} = %b %b", a, b, ci, co, s);

$finish;

...

Verify the correctness of the simulation result.

(c) Add the sixth pattern of your own to show an overflow condition. You need to list the inputs and

output in binary and decimal and explain why there is an overflow.

(d) Capture and provide screenshots of the final simulation result for both text log and waveform.

Chih-Tsun Huang

NTHU

3 / 3