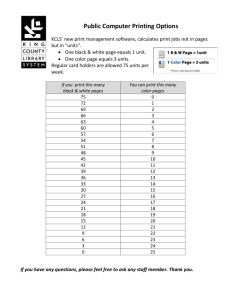

1.2 Functional Diagrams and Function Symbols* J. E. JAMISON (2003) The purpose of this section is to help the reader establish a uniform means of depicting and identifying mainly digitalbased application software functions used for measurement, monitoring, and control. It is done by presenting a designation system including graphic symbols and identification codes as well as functional diagramming techniques that were formerly known as the Scientific Apparatus Manufacturers’ Association (SAMA) system. It must be noted that a significant part of this section has been extracted from the revision work of the ISA SP5.1 subcommittee, and much of it has been based on draft working documents being utilized at the time of this writing, documents with which one of the authors has been actively involved. Other portions of this section are based on the author’s experience in the industry and are not any part of the SP5.1 subcommittee proposed forthcoming revision. A disclaimer to any future ISA standards documents is hereby stated: The reader is cautioned that the draft ISA document that provided much of the information in this section has not been approved as of the time of this writing. It cannot be presumed to reflect the position of ISA or any other committee, society, or group. The intent is to pass along to the reader the best and latest thinking on this subject at this point in time. ISA FUNCTIONAL DIAGRAMMING (EX-SAMA)* Instrument and Control Systems Functional Diagramming Symbol tables are given for use in preparing instrument and control loop functional diagrams, which are not normally shown on process flow diagrams (PFDs) and piping and instrument diagrams (P&IDs). They are used to depict monitoring and control loops in functional instrument diagrams, functional logic diagrams, application software diagrams, sketches, and text. They shall be prepared from the following: a) Instrument line symbols b) Instrument functional diagramming symbols c) Mathematical function block symbols Equivalent P&ID Loop, Functional Instrument and Electrical Diagrams See statement of permission in the footnote below. a) P&ID loop schematic: LT ∗71 LSH ∗01 LIC ∗01 LSL ∗01 Start HS ∗ 01B-1 SP FT Stop HS ∗01B-2 H-O-A ∗01 FIC ∗01 HS ∗01A FV ∗01 P ∗01 FO * Used with permission of the Instrumentation, Systems and Automation Society. 31 © 2003 by Béla Lipták 32 General Considerations b) Functional instrument diagram: LT FT *01 *01 A N D H/ L A K HS*1A I A N D Auto OR NOT NOT K I HS*1B-1 T A T HS*1B-2 A A N D Start Start Pump A N D Stop Overload A N D OR S NOT R Reset F(x) c) Electrical schematic diagram: START HS-∗01B-1 M1 STOP HS-∗01B-2 LSL-∗01 H OL HS-∗01A M 0 M2 LSH-∗01 Note: There is no equivalent electrical schematic for the process control instrumentation. Functional Diagramming Symbol Tables* The symbols used in Table 1.2a are not normally used on P&IDs but are used to diagram control systems at the *The symbols have been extracted by ISA, with permission, from Scientific Apparatus Manufacturers’ Association SAMA Standard PMC 22.1–1981, Functional Diagramming of Instrument and Control Systems, which is no longer supported by SAMA. © 2003 by Béla Lipták hardware and function level for configuration and other purposes. The symbols in Table 1.2b are never used in P&IDs and are used to help document and diagram logic control designs and narratives. The present standard ISA S5.2 (ANSI/ISAS5.2–1976 [R1992]) is now being revised and rolled into the new ANSI/ISA-5.01.01 standard as proposed in the current (as of this writing) Draft 4. Symbols, truth tables, definitions, and graphs used in this section are in accordance with Draft 4 and are very different from S5.2. They are given here to illustrate the latest thinking in this area, including expanded 1.2 Functional Diagrams and Function Symbols 33 TABLE 1.2a Functional Diagramming Symbols—Instrument and Mathematical Functions (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. Symbol Description 01 Measuring device Input device Readout device Output device Symbols from Tables 1.1h through 1.1k may be used 02 Automatic controller Single-mode controller Discrete device driver Insert function symbols, as required to define controller algorithm, from Table 1.2c Use for vertical diagramming 03 Automatic controller Two-mode controller Insert function symbols, as required to define controller algorithm, from Table 1.2c Use for vertical diagramming 04 Automatic controller Three-mode controller Insert function symbols, as required to define controller algorithm, from Table 1.2c Use for vertical diagramming 05 Automatic signal processor Insert function symbol from Table 1.2c Use for vertical diagramming 06 Automatic controller Two-mode controller Insert function symbols, as required to define controller algorithm, from Table 1.2c Use for horizontal diagramming 07 Automatic controller Two-mode controller Insert function symbols, as required to define controller algorithm, from Table 1.2c Use for horizontal diagramming 08 Automatic signal processor Insert function symbol from Table 1.2c Use for horizontal diagramming May be rotated 90° 09 Final control element Control valve Insert function symbol identifier from Table 1.2c (no. 14) 10 Final control element with positioner Control valve with positioner Insert function symbol identifier from Table 1.2c (no.14) 11 Manual signal processor (*) = A, adjustable signal generator (*) = T, signal transfer * 12 Manual auto station A T See statement of permission on page 31. timing functions. Application information and examples on the use of the binary symbols are given in Section 1.12, Binary Logic Diagrams, and they use the current standard ANSI/ISAS5.2–1976 (R1992). © 2003 by Béla Lipták Binary logic switching and memory functions are used in analog or sequential control schemes. In truth tables and graphs, logic one (1) is true and logic zero (0) is false. 34 General Considerations TABLE 1.2b Instrument and Control System Functional Diagramming Symbols—Binary Logic, Memory, and Time Functions (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. Symbol/Truth Table Definition/Graph 01 A B C AND gate. Output is true only if all inputs are true. A N D O x 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 A B C x O 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 1 0 0 0 0 1 0 0 1 0 1 1 0 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 02 1 0 A B C X O t 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 OR gate. Output is true if any input true. A B C OR O x 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 A 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 © 2003 by Béla Lipták B 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 C 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 1 x 0 0 0 0 1 0 0 1 0 1 1 0 1 1 1 1 O 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 A B C X O t 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 1.2 Functional Diagrams and Function Symbols 35 TABLE 1.2b Continued Instrument and Control System Functional Diagramming Symbols—Binary Logic, Memory, and Time Functions (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. Symbol/Truth Table 03 A B C ≥n O Definition/Graph Qualified OR gate with greater than or equal to qualifications. Output equals “1” if number of inputs equal to “1” are greater than or equal to “n” inputs. Truth table and graph are for “n” equals 2. x 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 A 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 B 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 C 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 1 x 0 0 0 0 1 0 0 1 0 1 1 0 1 1 1 1 O 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 04 A B C >n O 1 0 A B C X O t 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Qualified OR gate with greater than qualifications. Output equals “1” if number of inputs equal to “1” are greater but not equal to “n” inputs. Truth table and graph are for “n” equals 2. x 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 A 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 B 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 C 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 1 x 0 0 0 0 1 0 0 1 0 1 1 0 1 1 1 1 O 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 0 A B C X O t 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 (Continued) © 2003 by Béla Lipták 36 General Considerations TABLE 1.2b Continued Instrument and Control System Functional Diagramming Symbols—Binary Logic, Memory, and Time Functions (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. Symbol/Truth Table 05 A B C ≤n O Definition/Graph Qualified OR gate with less than or equal to qualifications. Output equals “1” if number of inputs equal to “1” are less than or equal to “n” inputs. Truth table and graph are for “n” equals 2. x 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 A 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 B 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 C 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 1 x 0 0 0 0 1 0 0 1 0 1 1 0 1 1 1 1 O 0 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 06 A B C <n O 1 0 A B C X O t 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Qualified OR gate with less than qualifications. Output equals “1” if number of inputs equal to “1” are less but not equal to “n” inputs. Truth table and graph are for “n” equals 2. x 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 © 2003 by Béla Lipták A 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 B 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 C 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 1 x 0 0 0 0 1 0 0 1 0 1 1 0 1 1 1 1 O 0 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 1 0 A B C X O t 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 1.2 Functional Diagrams and Function Symbols 37 TABLE 1.2b Continued Instrument and Control System Functional Diagramming Symbols—Binary Logic, Memory, and Time Functions (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. Symbol/Truth Table 07 A B C =n O Definition/Graph Qualified OR gate with equal to qualifications. Output equals “1” if inputs equal to “1” are equal to “n” inputs. Truth table and graph are for “n” equals 2. x 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 08 A 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 A B C B 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 C 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 1 x 0 0 0 0 1 0 0 1 0 1 1 0 1 1 1 1 ≠n O 0 0 0 0 0 1 1 1 1 1 1 0 0 0 0 0 O 1 0 A B C X O t 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Qualified OR gate with not equal to qualifications. Output equals “1” if inputs equal to “1” are not equal to “n” inputs. Truth table and graph are for “n” equals 2. x 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 A 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 B 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 C 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 1 x 0 0 0 0 1 0 0 1 0 1 1 0 1 1 1 1 O 0 1 1 1 1 0 0 0 0 0 0 1 1 1 1 1 1 0 A B C X O t 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 (Continued) © 2003 by Béla Lipták 38 General Considerations TABLE 1.2b Continued Instrument and Control System Functional Diagramming Symbols—Binary Logic, Memory, and Time Functions (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. Symbol/Truth Table 09 NOT A A 1 0 O O 0 1 Definition/Graph NOT gate. Output is false if input is true. Output is true if input is false. A 1 0 O 1 0 t 1 10 A S C B R D 1 2 3 4 5 6 7 8 A 0 1 0 0 0 1 0 1 B 0 0 0 1 0 1 0 1 C 0 1 1 0 0 1 1 0 D 1 0 0 1 1 0 0 1 2 3 4 A So C B R D 1 2 3 4 5 6 7 8 A 0 1 0 0 0 1 0 1 B 0 0 0 1 0 1 0 1 C 0 1 1 0 0 1 1 1 D 1 0 0 1 1 0 0 0 7 8 9 10 11 12 13 14 15 16 1 0 B C D t 2 3 4 5 6 7 8 Set dominant memory (“So dominant”). Outputs C and D are always opposite. If input A equals “1”, then output C equals “1”, and D equals “0”. If input A changes to “0”, output C remains “1” until input B equals “1”, then output C equals “1”, and D equals “0”. If input B equals “1”, then output D equals “1”, and C equals “0”. If input B changes to “0”, output D remains “1” until input A equals “1”, then output D equals “1”, and C equals “0”. If inputs A and B are simultaneously equal to “1”, then output C equals “1”, and D equals “0”. 1 0 A B C D t 1 © 2003 by Béla Lipták 6 A 1 11 5 Basic memory. Outputs C and D are always opposite. If input A equals “1”, then output C equals “1”, and D equals “0”. If input A changes to “0”, output C remains “1” until input B equals “1”, then C equals “1”, and D equals “0”. If input B equals “1”, then output D equals “1”, and C equals “0”. If input B changes to “0”, output D remains “1” until input A equals “1”, then D equals “1”, and C equals “0”. If inputs A and B are simultaneously equal to “1”, then outputs C and D change state. 2 3 4 5 6 7 8 1.2 Functional Diagrams and Function Symbols 39 TABLE 1.2b Continued Instrument and Control System Functional Diagramming Symbols—Binary Logic, Memory, and Time Functions (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. 12 Symbol/Truth Table A S C B Ro D 1 2 3 4 5 6 7 8 A 0 1 0 0 0 1 0 1 B 0 0 0 1 0 1 0 1 C 0 1 1 0 0 0 0 0 Definition/Graph Reset dominant memory (“Ro dominant”). Outputs C and D are always opposite. If input A equals “1”, then output C equals “1”, and D equals “0”. If input A changes to “0”, output C remains “1” until input B equals “1”, then output C equals “1”, and D equals “0”. If input B equals “1”, then output D equals “1”, and C equals “0”. If input B changes to “0”, output D remains “1” until input A equals “1”, then output D equals “1”, and C equals “0”. If inputs A and B are simultaneously equal to “1”, then C equals “0”, and D equals “1”. D 1 0 0 1 1 1 1 1 1 0 A B C D t 1 13 I t PD O 2 3 4 5 6 7 8 Pulse duration, fixed. Output O changes from “0” to “1” and remains “1” for prescribed time duration “t” when input “I” changes from “0” to “1”. NONE 1 0 I O t t t 14 I t DT O Off-time delay. Output O changes from “0” to “1” when input “I” changes from “0” to “1”. Output O changes from “1” to “0” after input I changes from “1” to “0” and has been equal to “0” for time duration “t”. NONE 1 0 I O t t t (Continued) © 2003 by Béla Lipták 40 General Considerations TABLE 1.2b Continued Instrument and Control System Functional Diagramming Symbols—Binary Logic, Memory, and Time Functions (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. Symbol/Truth Table 15 I t GT O R Definition/Graph On-time delay. Output O changes from “0” to “1” after input “I” changes from “0” to “1” and “I” remains “1” for prescribed time duration “t”. Output O remains “1” until a. Input “I” changes to “0”. b. Reset R changes to “1”. NONE 1 0 I O t t t R 16 I t LT O R t Pulse duration, variable. Output O changes from “0” to “1” when input “I” changes from “0” to “1”. Output O changes from “1” to “0” when a. Input “I” has equaled “1” for time duration “t”. b. Input “I” changes from “1” to “0”. c. Reset R changes to “1”. NONE 1 0 I O R See statement of permission on page 31. © 2003 by Béla Lipták t t t t 1.2 Functional Diagrams and Function Symbols 41 TABLE 1.2c Mathematical Function Block Symbols (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. 01 Symbol/Function Equation/Graph Definition Output equals the algebraic sum of inputs. M = X 1 + X 2 … .+ X n Σ X Xn M X1 Summation X2 t 02 Σ/n M = X1 + X2 …. + t Output equals the algebraic sum of the inputs divided by number of inputs. X n/n X M X1 X2 X3 Average t t 03 Output equals the difference between two inputs. M = X1 − X2 ∆ X X1 M X2 Difference t 04 t Output equals the product of the two inputs. M = X1 X2 X X1 X M X2 Multiplication t1 05 ÷ t1 t t Output equals the quotient of the two inputs. M = X1 / X2 X1 X M X2 Division t1 06 2 X M=X t1 t t Output is equal to the square of the input. 2 X M Square t t 07 X n M= X Output is equal to the nth power of the input. n X M Exponential t t (Continued) © 2003 by Béla Lipták 42 General Considerations TABLE 1.2c Continued Mathematical Function Block Symbols (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. 08 Symbol/Function √ Equation/Graph X M= Definition Output is equal to the square root of the input. M X Square Root t t 09 n √ n M= X Output is equal to the nth root of the input. X M nth Root t 10 K or P t Output is proportional to the input. Replace “K” with “1:1” for volume boosters. Replace “K” with “2:1”, ‘3:1”, etc. for integer gains. M = KX X M Proportional t1 11 -K or -P t t t1 M = −KX t1 Output is inversely proportional to the input. t X Reverse Proportional M t t1 12 ∫ or I M = (1/TI ) X ∫ Output varies with the magnitude and time duration of the input. Output is proportional to the time integral of the input. TI, the integral time constant. X dt M Integral t1 13 d/dt or D t2 t t1 t2 t Output is proportional to the time rate of change of the input. TD , derivative time constant. M = T D (dX/dt) X M Derivative t1 14 ƒ(X) t t1 t Output is a nonlinear or unspecified function of the input. Function is defined in note or other text. M = ƒ (X) X M Unspecified Function t © 2003 by Béla Lipták t 1.2 Functional Diagrams and Function Symbols 43 TABLE 1.2c Continued Mathematical Function Block Symbols (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. 15 Symbol/Function ƒ(t) Equation/Graph Definition Output equals a nonlinear or unspecified time function times the input. Output is a nonlinear or unspecified time function. M = Xƒ(t) X M Time Function t1 16 > t t1 t Output equals greater of two or more inputs. M = X 1 for X 1 ≥ X 2 , M = X 2 for X 1 ≤ X 2 X X1 M X2 High Select t1 17 < M = X 1 for X 1 ≤ X t t t1 Output equals lesser of two or more inputs. X 2 , M = X 2 for X 1 ≥ X 2 X1 M X2 Low Select t1 18 > t t t1 Output equals the lower of the input or high limit values. M = X1 for X1 ≤ H, M = X2 for X1 ≥ H X X M H High Limit t t1 19 < t1 t Output equals the higher of the input or low limit values. M = X1 for X1 ≥ L, M = X2 for X1 ≤ L X X M H Low Limit t1 20 V Velocity Limiter t t1 t Output equals input as long as the input rate of change does not exceed the limit value that establishes the output rate of change until the output again equals the input. dM/dt = dX/dt (dX/dt ≤ H, M = X) dM/dt = H (dX/dt ≥ H, M ≠ X) dX/dt>H X dM/dt=H M t1 t2 t t1 t2 t (Continued) © 2003 by Béla Lipták 44 General Considerations TABLE 1.2c Continued Mathematical Function Block Symbols (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. 21 Symbol/Function Equation/Graph Definition Output is equal to input plus an arbitrary value. M=X+b + X M b Positive Bias t X t M b t 22 t Output is equal to input minus an arbitrary value. M=X−b − X M b Negative Bias t X t M b t t 25 I = P, P = I, etc. ∗/∗ I P Conversion t 26 ∗H Output state is dependent on the value of the input. Output changes state when the input is equal to or higher than an arbitrary high limit. (State 1) M = 0 @ X < H (State 2) M = 1 @ X ≥ Η X High Signal Monitor X State 1 H t1 27 ∗L Low Signal Monitor t State 2 t1 Output state is dependent on the value of the input. Output changes state when the input is equal to or lower than an arbitrary low limit. (State 1) M = 0 @ X ≤ H (State 2) M = 1 @ X > Η X M X State State 1 2 L t © 2003 by Béla Lipták t Output signal type is different from that of input signal. * is equal to: E – voltage, A – analog I – current, B – binary P – pneumatic, D – digital R – resistance, H – hydraulic O – electromagnetic, sonic t 1.2 Functional Diagrams and Function Symbols 45 TABLE 1.2c Continued Mathematical Function Block Symbols (proposed for the next revision of ISA S5.1 [now ANSI/ISA-5.01.01] at the time of this writing) No. 28 Symbol/Function Equation/Graph ∗HL Definition Output states are dependent on value of input. Output changes state when input is equal to or lower than an arbitrary low limit or equal to or higher than an arbitrary high limit. (State 1) M = 1 @ X ≤ L (State 2) M = 0 @ L < X < H (State 3) M = 1 @ X ≥ Η X High/Low Signal Monitor M X State 1 H State 2 State 3 L t 29 T t Output equals input that is selected by transfer. Transfer is actuated by external signal. (State 1) M = X1 (State 2) M = X2 X X1 M Transfer State 2 State 1 X2 t See statement of permission on page 31. © 2003 by Béla Lipták t