Lab 1:

Introduction

@SkillsArray

Digital Electronics II

1

Outline

Introduction

Basics of the Verilog Language

@SkillsArray

Digital Electronics II

2

Importance of HDLs

HDL is an acronym of Hardware Description Language.

Two most commonly used HDLs:

Verilog HDL (also called Verilog for short)

2. VHDL (Very high-speed integrated circuits HDL)

1.

Features of HDLs:

Design can be described at a very abstract level.

Functional verification can be done early in the design cycle.

Designing with HDLs is analogous to computer programming.

@SkillsArray

Digital Electronics II

3

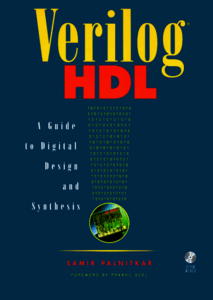

What is Verilog?

HDL describe the structure and behavior of digital electronic circuits.

Verilog is intended to be used for verification through simulation, for

timing analysis, for test analysis (testability analysis and fault

grading) and for logic synthesis.

Synthesis is the process of converting a high-level description of design

(Verilog/VHDL) into an optimized gate-level representation.

Mixed level modeling

Behavioral

Structural

Algorithmic ( like high level language)

Register transfer (Synthesizable)

Gate (AND, OR ……)

Switch (PMOS, NOMS, JFET ……)

Invented in 1985 and standardized in 1995 under the IEEE 1364-1995

@SkillsArray

Digital Electronics II

4

Cont…

Verilog designs partitioned in a hierarchy of modules

Modules communicate using input, output, and inout ports

Described process is executed in a concurrent manner (in parallel)

Verilog is case sensitive

Extra white space is ignored

Keywords are in lowercase

But whitespace does separate tokens

Comments

One liners are //

Multiple lines /* */

Comments may not be nested

@SkillsArray

Digital Electronics II

5

Verilog Value Set

0

represents low logic level or false condition

1

represents high logic level or true condition

x

represents unknown logic level

z

represents high impedance logic level

@SkillsArray

Digital Electronics II

6

Abstraction Levels

Abstraction Levels are used in engineering to specify

how a system will operate without getting consumed

in implementation details

Each level has requirements/specifications

The number of details in the requirements is just

enough to characterize the behavior for that level

Abstraction Levels

System (highest)

(generic specs)

Example

System - The LAN network speed shall be 10 Gbps

Algorithm – the CPU will get the samples from all temperature sensors,

calculate the average, and send it to the remote server.

RTL – the output of the encryption block shall be stored in 128 bit by

64 locations synchronous FIFO

Gate – The dsign shall be synthesized using gates from the

fab32ntzq65.v cell library

Circuit – the structure of an AND gate shall be the following –

transistor schematic for AND gate

Material – cells from fab32ntzq65.v shall be implemented using a 32 nm

process

@SkillsArray

Digital Electronics II

Verilog modeling

Algorithm (subsystem

specs)

Register Transfer

Level (RTL) (block

level data flow)

Gate

Circuit

Material (lowest)

7

Digital Design

Flow

@SkillsArray

Digital Electronics II

8

@SkillsArray

Digital Electronics II

9

Tools used

Electronic Design Automation (EDA) tools are software tools used to

design ICs and PCBs.

EDA = CAD {computer aided design (create schematics)} + CAE

{Computer aided engineering (analyze schematics)}

Several software packages are

used depending on stage

Specification

Design

Implementation

Verification

Test

@SkillsArray

Verilog Simulators

ModelSim and Questa (Mentor)

Incisive Enterprise Simulator

(Cadence)

VCS (Synopsys)

Vivado (Xilinx)

Icarius Verilog (Open source)

Digital Electronics II

10

Installation

Intel ® Quartus ® Prime Lite Edition

Complete design and verification flow for Verilog and VHDI

Comes with Modelsim-intel FPGA Edition (simulation)

Can synthesize your designs and then upload them in an FPGA (Field

Programmable Gate Arrays) development Board (DE1-SoC)

https://fpgasoftware.intel.com/?edition=lite

Create account and download the following and install

Online Simulators

You also need Notepad++

https://edaplayground.com/

https://www.tutorialspoint.com/compile_verilog_online.php

https://www.jdoodle.com/execute-verilog-online/

@SkillsArray

Digital Electronics II

11

Creating a Hello Message

Use ModelSim of online simulators

Create this hello_world file on notepad++ and save it as .v file in you

working folder.

Create another folder within your working folder and name is sim

@SkillsArray

Digital Electronics II

12

Instructions

Create a project folder

Open ModelSim

Go to File ⟶ New ⟶ Project

On the pop-up window, write the project name then click on browse to

select folder (you created earlier) and click ok.

@SkillsArray

Digital Electronics II

13

Cont…

A new window opens,

Select add existing file and browse (one

level up), and select the earlier created

hello_world file and click ok and close

A hello_world can be seen with

a ? Mark. This means that the

file has not been compiled.

Right click and compile all. You will then

have a green √ (successfully compiled.

@SkillsArray

Digital Electronics II

14

Cont…

Go to menu ⟶ Simulate ⟶

Start Simulation ⟶ Expand the

library work and select

hello_world and click ok. (wait

for all icons to be fully loaded).

Then Run all

@SkillsArray

The word hello world will

be displayed on the lower

left section

Digital Electronics II

15

Excercise

Repeat the same process but change from hello-world to something

like this.

I am _____ and this is my first Digital Electronics lab

Procedure

Change on text editor (notepad++)

Click on the project (lower left) ⟶ right click ⟶ compile all ⟶ restart ⟶

ok ⟶ run all

@SkillsArray

Digital Electronics II

16