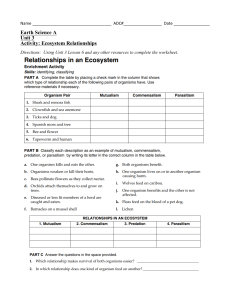

1 CHAPTER 1 1 INTRODUCTION The low power applications were becoming more and more essential due to the increasing portable electronics market during the last decades. The emerging rush to the mobile communications, mobile computers and their immobile counterparts are preceding the constant improvement of low power and high performance ICs. Due to the energy density limitations of commonly used batteries, the weight reduction of portable devices became a bottleneck. Therefore, it was necessary to reduce the total power consumption for saving weight of such portable devices. But, it was divergent to the rapidly growing number of devices on a single chip, due to increasing system complexity. So, it was important to solve these power problems on the transistor and circuit levels. The power consideration, which grew so great, acquired as an important design parameter along with other two inevitable parameters; speed and chip area, each one was being dependent on the others (N. A. Shah and F. A. Khanday, 2009). VLSI where millions of transistors can be integrated on a single chip was perfectly suitable for portable electronics requirements specifically CMOS technology due to its low power consumption and scalability. For many years, bipolar transistor was dominant in the design of silicon ICs. The emergent of Metal Oxide Semiconductor Field Effect Transistor (MOSFET) which demonstrated area and power reduction changed the scenario and became the vehicle for growth of VLSI designs. The CMOS technology, 2 which was designed with complementary and symmetric pairs of n-channel Metal Oxide Semiconductor (NMOS) and p-channel Metal Oxide Semiconductor (PMOS) transistors, dominated both digital and analog IC designs. In CMOS technology, the power was dissipated only when the circuit actually switches. The CMOS circuits had almost zero static power dissipation unlike bipolar circuits. The advancement of CMOS technology had been the stronghold in the implementation of entire electronic SoC which consisted of digital, analog and mixed signal functions. Signal processing was significant in many of the SoC applications. The real world signals are inherently analog signals. Processing of the analog signals was very complex. So, there was a necessity to convert it to the digital form with the intention that the processing of the digital domain was easier. ADC is a mixed signal device which act as interface between the real world and the digital circuits, facilitate the effortless processing of the sensors or transducers output. Hence, there was a huge demand of high speed and low power ADCs (Chen et al. 2012). 1.1 ADC AND ITS TYPES The ADC is a broadly used mixed signal electronic device that converts an input analog electrical signal (commonly a voltage) to a digital (binary) word as shown in Figure 1.1. The ADC had an analog reference voltage or current to which the input analog signal was compared. The digital output words expressed the fraction of reference current or voltage relevant to that of the input signal. 3 Figure 1.1 Basic Block Diagram of an ADC The ADC performed the conversion periodically that is by taking samples of the input instead of performing continuous conversion. Therefore, there was a requisition of defining the rate at which new digital values were sampled from the input analog signal. The rate of new digital values was called as sampling frequency or sampling rate of the converter. For the faithful reproduction of original signal, the sampling rate should be higher than twice the amount of highest frequency of the input signal which was stated as Shannon – Nyquist sampling theorem. The conversion also included the quantization of input to obtain the digital signal. The ADC had wide range of applications such as sensors, data acquisition systems, digital signal processors, radar and communication interfaces. The ADC architecture was chosen on the basis of application requirements. There were many ways had been developed for conversion process, each with its own strengths and weaknesses. If there was a need for speed, a fast ADC can be used else if there was a need of precision, an accurate ADC can be used else if there was constrain in space, a compact ADC can be used appropriately. Hence, there were wide variety of ADC architectures were available with respect to the application requirements. The types of ADC were: 4 Successive Approximation Register ADC Integrating or Dual Slope ADC Flash ADC Averaging ADC Folding and Interpolating ADC Sub Ranging ADC Pipelined ADC Algorithmic ADC Time Interleaved ADC Delta Encoded ADC Sigma Delta ADC Wilkinson ADC 1.1.1 Successive Approximation Register ADC SAR ADC evaluated each bit at a time from most significant bit to least significant bit through all possible quantization levels. The comparator was used in this ADC to compare the input signal with the reference signal obtained from the DAC. SAR logic was used to obtain the digit bits as output of the ADC which was also input of the DAC. Advantages Compact implementation Low power consumption 5 Disadvantages The size of DAC grew with number of bits. They took as many clock cycles for conversion as number of bits. 1.1.2 Integrating or Dual Slope ADC The dual slope ADC used counters to generate the output digital bits. As per the name, the ADC had two phases where first phase ramped up with a slope proportional to the input voltage for a fixed time period and second ramped down with a different slope proportional to the reference voltage for a varied time period. Advantages Very precise The sources of errors were only comparison with zero and clock period. Disadvantages Low speed Needed time to ramp up and down the output voltage which doubled with addition of each bit added to the representation. 1.1.3 Flash ADC Flash ADC had a resistor ladder which divided the reference voltage into equal parts. For every part, a comparator was used to compare the input signal and the voltage obtained from the part of resistor ladder. The outputs of all the comparators were called as thermometer code which was converted to binary code using encoder. 6 Advantages Very fast Instant conversion Disadvantages The size of the ADC doubled for each bit added to the representation. Very high power consumption 1.1.4 Averaging ADC In averaging ADC, the input analog signal was applied to more than one number of ADCs with same clock frequency and phase. The output digital words were generated by averaging them at each clock cycle. Advantages Signal to noise ratio was improved. Uncorrelated noise sources between the ADCs were reduced. Disadvantages Very high power consumption Large area 1.1.5 Folding and Interpolating ADC The architecture consisted of folding blocks and interpolation blocks. The folding architecture was used to reduce the number of comparators and interpolation architecture was used to reduce the number of differential pairs attached to the input signal. The architecture also consisted of coarse quantizer and encoder. 7 Advantages No sub stage DAC No need of linear processing. Disadvantages Jitter errors at high frequencies. Increase in folding factor proportion to ADC resolution 1.1.6 Sub Ranging ADC The architecture of sub ranging ADC was built in two important steps. The input was tracked and held (T/H) in first step. Then it was digitized by a sub stage ADC to produce Most Significant bits (MSBs) in second step. The digital bits were then applied to sub stage DAC and the result was subtracted from T/H output to determine the Least Significant bits (LSBs). A summer was used to yield the final digital word. Advantages No residue amplifier required compared to pipelined ADC. Reduced complexity compared to flash ADC Disadvantages Three clock phases required for each conversion. Low speed 1.1.7 Pipelined ADC Pipelined ADC required number of conversion stages proportional to number of bits. At each conversion stage, the input signal was compared to half the reference value. If it was higher, the reference value was subtracted to input and bit corresponding to that stage was binary 1 else it was 8 binary 0. In both cases, the remaining value was doubled and conceded to next stage. Advantages Higher speed Higher Bandwidth Disadvantages High latency Any error introduced in a stage propagated to the following stages. 1.1.8 Algorithmic ADC Algorithmic ADC, which was also called cyclic ADC, was designed on the basis of binary division principle. The architecture was similar to that of pipelined ADC but single stage was used for all partial conversions. But, it was unable to process more than one sample at a time. Hence, this ADC needed N+1 clock cycles to quantize N bit representation. Advantages Less area Low power consumption Disadvantages Low speed Less throughput 1.1.9 Time Interleaved ADC The time interleaved ADC used M identical parallel ADCs where each ADC sampled the data at every Mth cycle. Thus, the sampling rate was increased by M times in comparison. The architecture could be designed in 9 two ways. One with M identical parallel channels consisted of sample and hold (S/H) circuit and ADC in every channel. Another way was designed with single input S/H circuit and M ADCs. Advantages High speed Increased bandwidth Disadvantages High power consumption Large area 1.1.10 Delta Encoded ADC Delta encoded ADC, which was also known as counter-ramp ADC, had an up-down counter which fed a DAC. The comparator was used to compare the input signal and the DAC and control the counter. The ADC used negative feedback from the comparator to regulate the counter until DAC output was nearer to input signal. Advantages High resolution High bandwidth Disadvantages Low speed High power consumption 10 1.1.11 Sigma Delta ADC Sigma delta ADC was a unique ADC which sampled the signal in much higher frequency than the Nyquist frequency. Hence it was also called as oversampling ADC. The error between reference signal and input signal was integrated to obtain the outputs. Then, the output of the integrator was compared with zero. The process was repeated again and again to obtain the streams of binary zeros and ones. A decimation filter was used to convert the bit stream into desired binary code. Advantages Quantization noise spectral density was reduced. Very simple design Disadvantages Decimation filter was required in the end. Limited bandwidth 1.1.12 Wilkinson ADC The Wilkinson ADC was based on the comparison of input signal with the voltage produced by a charging capacitor. The capacitor was allowed to charge until its voltage equivalent to the amplitude of input signal and discharge linearly. When the capacitor started to discharge, a gate pulse was initiated and remained on until the capacitor discharged completely. The duration of the gate pulse was directly proportional to amplitude of the input signal. 11 Advantages Compact design Less area Disadvantages Low speed Limited bandwidth 1.2 PERFORMANCE METRICS OF ADCS The metrics that characterize the performance of ADCs are divided into two groups namely static and dynamic. The static performance metrics of ADCs are Figure of Merit (FOM), Differential Non-Linearity (DNL) and Integral Non-Linearity (INL). The dynamic performance metrics of ADCs are Effective Number of Bits (ENOB), Total Harmonic Distortion (THD), Signal to Noise Ratio (SNR), Signal to Noise and Distortion Ratio (SNDR) and Spurious Free Dynamic Range (SFDR). 1.2.1 Differential Non-Linearity The difference between an actual step width and ideal value of one LSB is termed as DNL error. The calculated DNL value must be less than 1 LSB. 1 LSB = VFSR / 2N (1.1) Where VFSR is full scale voltage range N is bit resolution of the ADC DNL ( LSB ) V p 1 VP Videal 1 for 0 p 2 N 2 (1.2) where Vp is the physical value corresponding to the digital output code Videal is ideal spacing of two adjacent digital codes 12 1.2.2 Integral Non-Linearity The deviation in LSB or the percent of full scale range of an actual transfer function is INL error. The INL is classified into two types namely the best straight line INL and end point INL. 1.2.2.1 Best Straight Line INL The best straight line INL provides information about gain (slope) error, offset (intercept) error and also position of the transfer function. It also determines the closest approximation to the ADC’s actual transfer function in the form of a straight line. This approach provides the best repeatability and also gives out true representation of linearity. 1.2.2.2 End Point INL The end point INL passes straight line through the end points of ADC’s transfer function and thereby defines precise position for the straight line. This straight line for a N-bit ADC is defined by its full scale range or its zero as outputs. INL ( LSB ) V p Vzero Videal p for 0 p 2 N 1 (1.3) where Vzero is minimum analog input voltage corresponding to all zero output code 1.2.3 Figure of Merit The FOM is a quantity used to represent the measure of efficiency and effectiveness of ADC. The FOM is given as 13 FOM ( J / step) Psignal min ( f s , 2 fin ) 2 ENOB (1.4) where Psignal is the average power of the signal fs is sampling frequency fin is frequency of the input signal 1.2.4 Effective Number of Bits ENOB can be obtained by ENOB (bits) SNDR 1.76 6.02 (1.5) where 1.76 is the term comes from quantization error in an ideal ADC 6.02 is the term which is used to convert decibels into bits 1.2.5 Signal to Noise and Distortion Ratio SNDR is defined as the ratio of total received power to noise plus distortion power. SNDR (dB ) 10 log Ps Pn Pd Pn Pd (1.6) where Ps is the average power of the signal Pn is the average power of the noise components Pd is the average power of the distortion components 1.2.6 Signal to Noise Ratio SNR is defined as the ratio of signal power to noise power which is expressed as 14 SNR (dB) 6.02 N 1.76 (1.7) where N is the resolution of ADC in bits 1.2.7 Total Harmonic Distortion THD is defined as the ratio of sum of powers of all harmonic components to power of fundamental signal which is used to measure the harmonic distortion in the signal. THD (dB) V22 V32 V42 V1 (1.8) where Vn is the root mean square voltage of nth harmonic and n = 1 is the fundamental signal voltage 1.2.8 Spurious Free Dynamic Range SFDR is defined as the strength ratio of the fundamental signal to the highest noise or harmonic distortion component in the FFT spectrum. This is an important specification which is used to determine the minimum signal level that can be differentiated from noise or distortion components. SFDR (dB ) 20 log 1.3 fundamental signal highest spurious (1.9) CHALLENGES IN DESIGNING ADC In mixed signal designs, combining analog circuits on a digital IC substrate was very difficult. Hence, there must be performance trade off and 15 sometimes there might be error in the designs. There were key challenges to be aware of while designing ADCs. The unavoidable challenges were: Sampling rates Bit resolution SNR ENOB Power Supply voltage 1.3.1 Sampling Rates To satisfy Nyquist sampling theorem, the sampling rate should be higher than twice the higher frequency of the input signal. However, faster sampling rate demanded higher bandwidth which in turn consumed more power and required better synchronization among the bits. 1.3.2 Bit Resolution Bit resolution was a reflection of how closely the analog signal represented as a digital word. The resolution was used to convey how many discrete values can be produced over the range of analog values. So, it was necessary to determine the bit resolution of the ADC. 1.3.3 SNR In ADC, any noise that presented in the signal reduced the accuracy of the digital output. So, care should be taken while considering the placement of neighbouring components and circuitry on the chip. 16 1.3.4 ENOB ENOB was a broad way to measure the impact of distortion, noise and temperature impact on the performance of ADC. So, it was essential to have ENOB as high as number of ADC bits. 1.3.5 Power In all SOC designs, power became an increasingly critical concern. There was an increase in power consumption whenever any of the performance metrics was improved. Always power became a trade off in the design of ADC. 1.3.6 Supply Voltage As the need for portable devices were drastically increased, there was a necessity to design the circuits with reduced supply voltage. The design of analog circuits with reduced supply voltage was critical when compared to that of digital circuits. So, more concentration should be taken when it came to supply voltage for the ADC architectural design. 1.4 MOTIVATION AND SCOPE OF THE THESIS The push for portable systems and longer battery life time in the electronic applications demands less area and low power consuming ADCs. The advancement in CMOS technologies had supported the design of analog circuits. In order to design efficient ADCs to achieve requirements using CMOS technology, the limitations and scope of the circuit designs should be understood. 17 1.4.1 Power Consumption Power consumption can be calculated by using various factors such as supply voltage, capacitance, leakage current, short circuit current, frequency and data activity. The commonly used expression for power consumption was given by Pc Pd Psc Pl (1.10) where Pc – Power Consumption Pd – Dynamic Power due to switching activities Psc – Short Circuit Power Pl – Leakage Power The short circuit power resulted from finite rise and fall time of the input signals that led to pull up and pull down network to ON for a short time period. The expression for short circuit power was given by Psc I sc Vdd (1.11) where Isc - Short Circuit Current Vdd – Supply voltage The reduction in supply voltage led to reduction in threshold voltage to maintain the performance. This resulted in exponential growth of the sub-threshold leakage current. Pl I l Vdd (1.12) where Il – Leakage Current 1.4.2 CMOS as Active Resistor The goal of the thesis is to optimize the building blocks of ADCs by overcoming their limitations to achieve high speed low power and area 18 efficient ADC architectures. Among the numerous ADC architectures, there are three important architectures namely flash ADC, SAR ADC and pipelined ADC are widely used (Razavi 2015). Hence, all three ADC architectures are considered for the research to attain their optimized designs and also record their static and dynamic performance metrics. The comparator is the essential element in the design of ADCs but also limit the performance of these ADCs (Katyal et al. 2006). So, there is a need of designing low power, low offset and high speed comparator. To arrive at the above specifications, the dynamic comparators are often used which compare the inputs once in every clock period (Jeon & Kim 2010). Hence, a dynamic comparator was proposed to meet the above mentioned criterions. The research includes proposed multiplexer based encoder for the design of flash ADC and proposed two SAR logics where one with FSM and other with shift registers. The research also includes the proposed DAC with zero average switching energy. The circuit designs are implemented in 130nm CMOS process using Tanner tool 13.0 version at 1.2 V supply voltage. The characteristics of the ADCs are manipulated with the help of MATLAB R2010a. 1.5 OBJECTIVES AND CONTRIBUTIONS OF THE THESIS The main objectives and contributions of the thesis are, To analyze various elements of ADC such as dynamic comparators, encoders, DACs, operational amplifiers by doing widespread survey on existing designs and study their merits and demerits. To propose a design of low power, area efficient and high speed 19 dynamic comparator. To design a four bit flash ADC architecture based on proposed dynamic comparator and proposed multiplexer based thermometer code to binary code encoder. To design a four bit SAR ADC architecture based on proposed dynamic comparator, proposed SAR logic designs using FSM and also using shift register and proposed DAC with zero average switching energy. To design a four bit pipelined ADC architecture based on proposed flash ADC as sub stage ADC, proposed DAC with zero average switching energy and operational amplifier. To implement the design of proposed ADCs in an automotive application. To carry out a comparative analysis between conventional and proposed designs by considering the parameters such as transistor count, delay, average power consumption, power delay product, static power dissipation and dynamic power dissipation. To observe and record the ADC static and dynamic characteristics such as: SFDR, SINAD, ENOB, INL, DNL and FOM. 1.6 ORGANIZATION OF THE THESIS The Chapters are organized as follows. Chapter 2 presents a detailed survey on various dynamic comparators and various components of ADCs. Chapter 3 proposes a design of low power, area efficient and high speed dynamic comparator. Chapter 4 proposes a design of four bit flash ADC architecture based on dynamic comparator and thermometer code to binary code 20 encoder. Chapter 5 proposes a design of four bit SAR ADC architecture based on dynamic comparator, two SAR logic designs where one using FSM and other using shift register, DAC with zero average switching energy. Chapter 6 proposes a design of four bit pipelined ADC architecture based on flash ADC as sub stage ADC, DAC with zero average switching energy and operational amplifier. Chapter 7 explains the implementation of the proposed ADC in the automotive applications using LabVIEW tool. Chapter 8 analyzes the performance of the proposed dynamic comparator. A comparative analysis is performed between the conventional and proposed designs to establish the effectiveness of the proposed designs. Chapter 9 concludes and recapitulates the overall effectiveness of the proposed designs and possible scope for the future work.