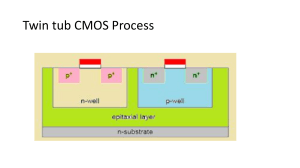

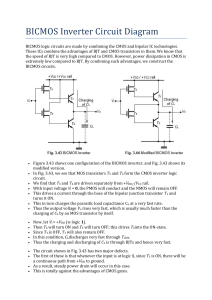

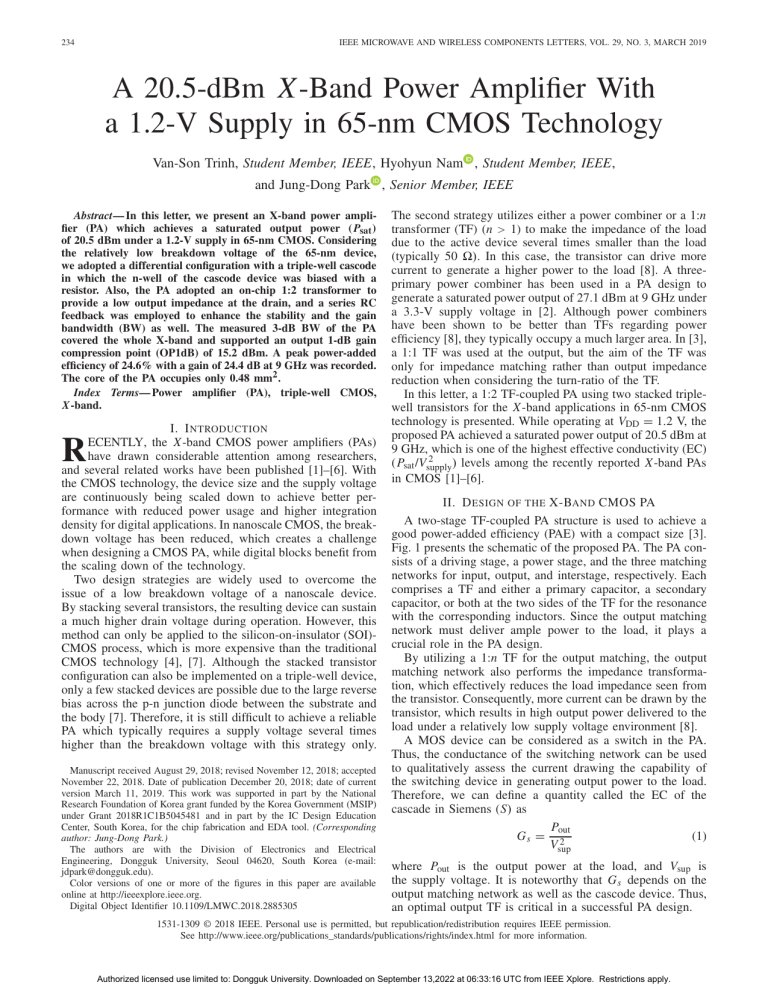

234 IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, VOL. 29, NO. 3, MARCH 2019 A 20.5-dBm X -Band Power Amplifier With a 1.2-V Supply in 65-nm CMOS Technology Van-Son Trinh, Student Member, IEEE, Hyohyun Nam , Student Member, IEEE, and Jung-Dong Park , Senior Member, IEEE Abstract— In this letter, we present an X-band power amplifier (PA) which achieves a saturated output power ( Psat ) of 20.5 dBm under a 1.2-V supply in 65-nm CMOS. Considering the relatively low breakdown voltage of the 65-nm device, we adopted a differential configuration with a triple-well cascode in which the n-well of the cascode device was biased with a resistor. Also, the PA adopted an on-chip 1:2 transformer to provide a low output impedance at the drain, and a series RC feedback was employed to enhance the stability and the gain bandwidth (BW) as well. The measured 3-dB BW of the PA covered the whole X-band and supported an output 1-dB gain compression point (OP1dB) of 15.2 dBm. A peak power-added efficiency of 24.6% with a gain of 24.4 dB at 9 GHz was recorded. The core of the PA occupies only 0.48 mm2 . Index Terms— Power amplifier (PA), triple-well CMOS, X-band. I. I NTRODUCTION ECENTLY, the X-band CMOS power amplifiers (PAs) have drawn considerable attention among researchers, and several related works have been published [1]–[6]. With the CMOS technology, the device size and the supply voltage are continuously being scaled down to achieve better performance with reduced power usage and higher integration density for digital applications. In nanoscale CMOS, the breakdown voltage has been reduced, which creates a challenge when designing a CMOS PA, while digital blocks benefit from the scaling down of the technology. Two design strategies are widely used to overcome the issue of a low breakdown voltage of a nanoscale device. By stacking several transistors, the resulting device can sustain a much higher drain voltage during operation. However, this method can only be applied to the silicon-on-insulator (SOI)CMOS process, which is more expensive than the traditional CMOS technology [4], [7]. Although the stacked transistor configuration can also be implemented on a triple-well device, only a few stacked devices are possible due to the large reverse bias across the p-n junction diode between the substrate and the body [7]. Therefore, it is still difficult to achieve a reliable PA which typically requires a supply voltage several times higher than the breakdown voltage with this strategy only. R Manuscript received August 29, 2018; revised November 12, 2018; accepted November 22, 2018. Date of publication December 20, 2018; date of current version March 11, 2019. This work was supported in part by the National Research Foundation of Korea grant funded by the Korea Government (MSIP) under Grant 2018R1C1B5045481 and in part by the IC Design Education Center, South Korea, for the chip fabrication and EDA tool. (Corresponding author: Jung-Dong Park.) The authors are with the Division of Electronics and Electrical Engineering, Dongguk University, Seoul 04620, South Korea (e-mail: jdpark@dongguk.edu). Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/LMWC.2018.2885305 The second strategy utilizes either a power combiner or a 1:n transformer (TF) (n > 1) to make the impedance of the load due to the active device several times smaller than the load (typically 50 ). In this case, the transistor can drive more current to generate a higher power to the load [8]. A threeprimary power combiner has been used in a PA design to generate a saturated power output of 27.1 dBm at 9 GHz under a 3.3-V supply voltage in [2]. Although power combiners have been shown to be better than TFs regarding power efficiency [8], they typically occupy a much larger area. In [3], a 1:1 TF was used at the output, but the aim of the TF was only for impedance matching rather than output impedance reduction when considering the turn-ratio of the TF. In this letter, a 1:2 TF-coupled PA using two stacked triplewell transistors for the X-band applications in 65-nm CMOS technology is presented. While operating at VDD = 1.2 V, the proposed PA achieved a saturated power output of 20.5 dBm at 9 GHz, which is one of the highest effective conductivity (EC) 2 (Psat /Vsupply ) levels among the recently reported X-band PAs in CMOS [1]–[6]. II. D ESIGN OF THE X-BAND CMOS PA A two-stage TF-coupled PA structure is used to achieve a good power-added efficiency (PAE) with a compact size [3]. Fig. 1 presents the schematic of the proposed PA. The PA consists of a driving stage, a power stage, and the three matching networks for input, output, and interstage, respectively. Each comprises a TF and either a primary capacitor, a secondary capacitor, or both at the two sides of the TF for the resonance with the corresponding inductors. Since the output matching network must deliver ample power to the load, it plays a crucial role in the PA design. By utilizing a 1:n TF for the output matching, the output matching network also performs the impedance transformation, which effectively reduces the load impedance seen from the transistor. Consequently, more current can be drawn by the transistor, which results in high output power delivered to the load under a relatively low supply voltage environment [8]. A MOS device can be considered as a switch in the PA. Thus, the conductance of the switching network can be used to qualitatively assess the current drawing the capability of the switching device in generating output power to the load. Therefore, we can define a quantity called the EC of the cascade in Siemens (S) as Pout Gs = 2 (1) Vsup where Pout is the output power at the load, and Vsup is the supply voltage. It is noteworthy that G s depends on the output matching network as well as the cascode device. Thus, an optimal output TF is critical in a successful PA design. 1531-1309 © 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Dongguk University. Downloaded on September 13,2022 at 06:33:16 UTC from IEEE Xplore. Restrictions apply. TRINH et al.: 20.5-dBm X -BAND PA WITH A 1.2-V SUPPLY IN 65-nm CMOS TECHNOLOGY Fig. 1. 235 Schematic of the two-stage TF-coupled PA (TF: transformer). Fig. 4. Fig. 2. (a) Structure of the bulk CMOS. (b) Schematics of the nMOS cascode with the bulk CMOS. (c) Structure of the triple-well CMOS. (d) Schematics of the conventional cascode with the triple-well CMOS. (e) Triple-well CMOS cascode with the biasing resistor (Rb ). Fig. 3. (a) Simulated voltage waveforms of the nodes shown in Fig. 2(e): drain (Vd ), n-iso1 (Vn ), gate1 (Vg ), and interpoint (Vi ). (b) PAE of the PA when using the configurations shown in Fig. 2(d) (PAE2d ) and Fig. 2(e) (PAE2e ). In a CMOS PA, a cascode is commonly used for boosting the gain and improving the stability in wireless regime [7], [9], [10]. For the bulk-CMOS technology with the device diagram illustrated in Fig. 2(a), the voltage swing of the drain is limited by the breakdown voltage of the drain-bulk junction Djdb [shown in Fig. 2(b)] when the bulk is connected to ground. Therefore, the cascode device (M1 ) is usually implemented with a thick-oxide transistor having a high breakdown voltage [3]. However, the channel resistance (Ron ) of the cascade device is increased due to the longer channel length of the thick-oxide MOS, which limits the current driving capability from the increased EC, G s . The body effect also significantly reduces the gain of the cascode. To avoid the limitation of the bulk-CMOS technology, a cascode of triple-well transistors can be employed, as shown in Fig. 2(d), where the body effect is avoided by tying the p-well of each transistor to its source as [7]. Owing to the Microphotograph of the CMOS PA (core size: 0.6 mm × 0.8 mm). stacked configuration, the voltage swing of the interpoint Vip is halved of the drain voltage (Vdrain ), which significantly relieves the stress on the junction diodes in the cascode structure. As presented in Fig. 2(d), each p-well is tied to its corresponding n-iso which may degrade the isolation between p-wells and p-sub of M1−2 . To enhance the isolation between p-wells and p-sub, resistor Rd can be employed as bias for the n-iso of the cascode device (n-iso1) from its drain, and the other n-iso node of the main transistor (n-iso2) can be connected to the supply voltage as illustrated in Fig. 2(e). The resistance, as well as the p-n junction capacitances of the n-iso1 node, determines the voltage at the n-iso1 node Vn−iso1. The resistance of Rd is chosen such that Vn−iso1 is higher than the p-well node but must be low enough to avoid the breakdown voltage of diode D3 . An RC bias circuit similar to the bias configuration used for the stacked transistors in the SOI-CMOS technology [7] is employed to bias the gate of M1 to achieve voltage distributed equally over the two stacked nMOSs in the cascode configuration. Fig. 3(a) presents the simulated voltages each node described in Fig. 2(e) when Pout = 21.5 dBm at 11 GHz, which shows that the peak drain voltage Vd approximately doubles the peak of the interpoint voltage Vi , while the voltage of n-iso1 node Vn is maintained at nearly 0.3 V higher than Vi . The gate voltage swings around its bias value of 1.4 V, thereby keeping the drain-to-gate and gate-to-source voltages in the safe region. Fig. 3(b) shows the comparison of the PAE of PA when using two different configurations in Fig. 2(d) and (e) is applied. The PA with the triple-well cascode device biased with Rd [Fig. 2(e)] achieves higher PAE than the PA without Rb [Fig. 2(d)]. In the designed PA, we introduce an RC feedback network to make the PA more stable with the improved bandwidth. A transient analysis in the time domain, as well as a k-stability check in the frequency domain, was carried out to ensure that the PA is stable during dynamic operation. The values of the elements and the biases of the PA are given in Fig. 1. To verify the design, a chip with the X-band CMOS PA was fabricated and measured. A photograph of the chip is shown in Fig. 4. III. M EASURED R ESULTS The X-band PA consumed a dc current of 289 mA when the input power was 0 dBm at 10 GHz; the consumed Authorized licensed use limited to: Dongguk University. Downloaded on September 13,2022 at 06:33:16 UTC from IEEE Xplore. Restrictions apply. 236 IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, VOL. 29, NO. 3, MARCH 2019 TABLE I S UMMARY OF THE CMOS PA S A ROUND THE X -BAND Fig. 5. S-parameter versus frequency of the X-band 65-nm CMOS PA. the simulation. About 10% of the peak degradation in PAE was recorded at 11 GHz. The frequency shift was mainly from the inaccuracy in parasitic extraction, and overall performance degradation was due to the lowered Q of the on-chip TF in the implemented PA. The performances of the CMOS PAs (including the SOI-CMOS) around the X-band reported recently are compared in Table I. The PA in this letter achieved the highest EC and a significant peak PAE compared to the other X-band PAs reported to date. IV. C ONCLUSION A fully integrated X-band PA was implemented on a standard 65-nm CMOS process. By employing a cascode of triple-well transistors and a 1:2 TF at the output, the PA could generate a saturated power output of 20.5 dBm at 9 GHz while operating with a 1.2-V source. R EFERENCES Fig. 6. Measured power performance of the PA in the range of 8–11 GHz in 1-GHz increments. Fig. 7. Measured and simulated saturated power output (Psat ), OP1dB, and peak PAE along with measured OIP3 versus frequency. dc current varied with the input power and the operating frequency. The measured S-parameters are shown in Fig. 5. Fig. 6 demonstrates the gain, output power, and PAE of the PA versus input power in the range of 8–11 GHz in 1-GHz increments. Fig. 7 shows a comparison of the simulated and measured results of the saturated power output (Psat ), output 1-dB gain compression point (OP1dB), and peak PAE at various frequencies from 8 to 11 GHz along with the measured OIP3 of the PA. Since the center frequency was shifted slightly toward the lower region, the measured performances of the PA were degraded more at higher frequency regime compared to [1] H. Wang, C. Sideris, and A. Hajimiri, “A CMOS broadband power amplifier with a transformer-based high-order output matching network,” IEEE J. Solid-State Circuits, vol. 45, no. 12, pp. 2709–2722, Dec. 2010. [2] J.-H. Tsai and J.-W. Wang, “An X-band half-watt CMOS power amplifier using interweaved parallel combining transformer,” IEEE Microw. Wireless Compon. Lett., vol. 27, no. 5, pp. 491–493, May 2017. [3] B.-H. Ku, S.-H. Baek, and S. Hong, “A wideband transformer-coupled CMOS power amplifier for X-band multifunction chips,” IEEE Trans. Microw. Theory Techn., vol. 59, no. 6, pp. 1599–1609, Jun. 2011. [4] J.-H. Chen, S. R. Helmi, A. Y.-S. Jou, and S. Mohammadi, “A wideband power amplifier in 45 nm CMOS SOI technology for X-band applications,” IEEE Microw. Wireless Compon. Lett., vol. 23, no. 11, pp. 587–589, Nov. 2013. [5] P.-S. Chi, Z.-M. Tsai, J.-L. Kuo, K.-Y. Lin, and H. Wang, “An X-band, 23.8-dBm fully integrated power amplifier with 25.8% PAE in 0.18-μm CMOS technology,” in Proc. 5th Eur. Microw. Integr. Circuits Conf. (EuMIC), Paris, France, Sep. 2010, pp. 436–439. [6] J. P. Comeau, E. W. Thoenes, A. Imhoff, and M. A. Morton, “X-band +24 dBm CMOS power amplifier with transformer power combining,” in Proc. IEEE 11th Top. Meeting Silicon Monolithic Integr. Circuits RF Syst. (SiRF), Phoenix, AZ, USA, Jun. 2011, pp. 49–52. [7] S. Pornpromlikit, J. Jeong, C. D. Presti, A. Scuderi, and P. M. Asbeck, “A watt-level stacked-FET linear power amplifier in silicon-on-insulator CMOS,” IEEE Trans. Microw. Theory Techn., vol. 58, no. 1, pp. 57–64, Jan. 2010. [8] I. Aoki, S. D. Kee, D. B. Rutledge, and A. Hajimiri, “Distributed active transformer—A new power-combining and impedance transformation technique,” IEEE Trans. Microw. Theory Techn., vol. 50, no. 1, pp. 316–331, Jan. 2002. [9] Y. Lee and S. Hong, “A dual-power-mode output matching network for digitally modulated CMOS power amplifier,” IEEE Trans. Microw. Theory Techn., vol. 61, no. 4, pp. 1570–1579, Apr. 2013. [10] N. Wongkomet, L. Tee, and P. R. Gray, “A +31.5 dBm CMOS RF Doherty power amplifier for wireless communications,” IEEE J. SolidState Circuits, vol. 41, no. 12, pp. 2852–2859, Dec. 2006. Authorized licensed use limited to: Dongguk University. Downloaded on September 13,2022 at 06:33:16 UTC from IEEE Xplore. Restrictions apply.