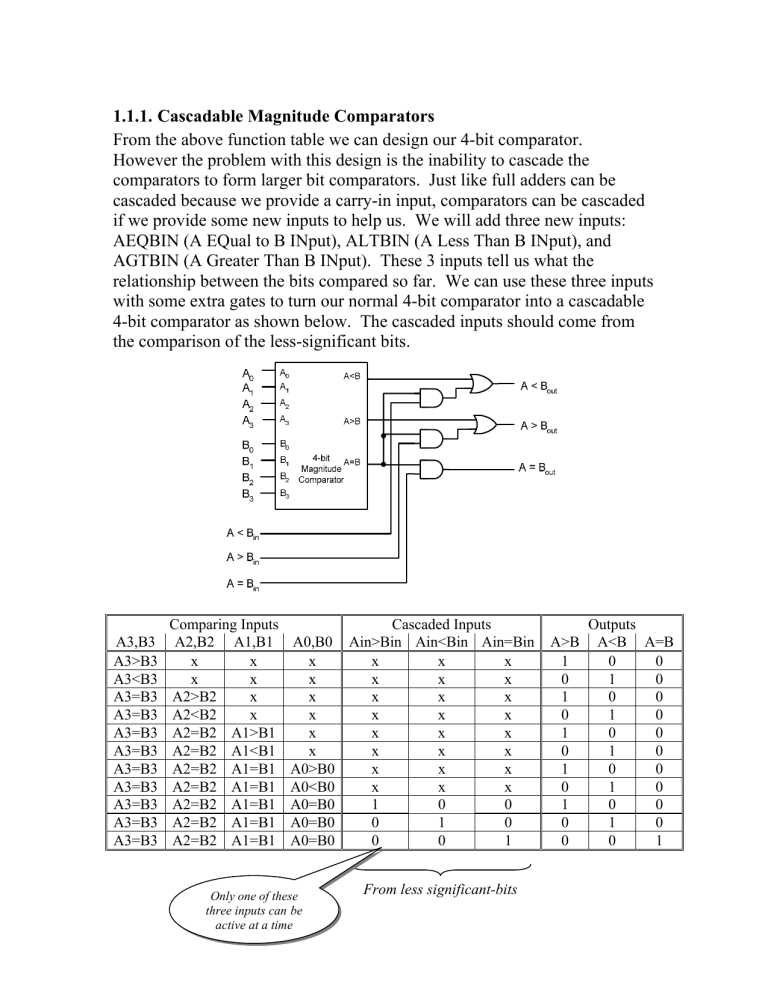

1.1.1. Cascadable Magnitude Comparators From the above function table we can design our 4-bit comparator. However the problem with this design is the inability to cascade the comparators to form larger bit comparators. Just like full adders can be cascaded because we provide a carry-in input, comparators can be cascaded if we provide some new inputs to help us. We will add three new inputs: AEQBIN (A EQual to B INput), ALTBIN (A Less Than B INput), and AGTBIN (A Greater Than B INput). These 3 inputs tell us what the relationship between the bits compared so far. We can use these three inputs with some extra gates to turn our normal 4-bit comparator into a cascadable 4-bit comparator as shown below. The cascaded inputs should come from the comparison of the less-significant bits. A3,B3 A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 Comparing Inputs A2,B2 A1,B1 x x x x A2>B2 x A2<B2 x A2=B2 A1>B1 A2=B2 A1<B1 A2=B2 A1=B1 A2=B2 A1=B1 A2=B2 A1=B1 A2=B2 A1=B1 A2=B2 A1=B1 Cascaded Inputs A0,B0 Ain>Bin Ain<Bin Ain=Bin x x x x x x x x x x x x x x x x x x x x x x x x A0>B0 x x x A0<B0 x x x A0=B0 1 0 0 A0=B0 0 1 0 A0=B0 0 0 1 Only one of these three inputs can be active at a time From less significant-bits A>B 1 0 1 0 1 0 1 0 1 0 0 Outputs A<B A=B 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 1 There is a standard MSI component called the 74LS85 that implements a 4bit cascadable comparator. One thing to notice is how the 74LS85 uses the cascaded inputs. They can only affect the output if the current set of 4 bits are equal. This design forces us to compare the lower bits first and pass the outputs of the lower order comparison to the next comparator as shown below: More Significant Bits Connect the less significant bits to this comparator Connect the more significant bits to this comparator Question: Can you use the above circuit to compare two 2-digit decimal numbers expressed in BCD? Exercise: Connect the following (3) 74LS85 comparators to compare a 12-bit number X = (X11…X0) with the constant 1578? Label your outputs as GT, EQ, or LT where GT = (X > 1578), EQ = (X = 1578), LT = (X < 1578). (1578)10 = ( )2 Exercise: Using a simple logic gate and your design above how could you produce a signal GE = (X ≥ 1578)? SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS SDLS123 – MARCH 1974 – REVISED MARCH 1988 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 7 Exercise: An alternative design for a 4-bit comparator is shown below. It uses the cascaded inputs from the higher-order bits. Please fill in the function table and then show how to compare (2) 8-bit numbers X=(X7…X0) and Y=(Y7…Y0) with 2 of these new comparators. Cascaded Inputs Ain>Bin Ain<Bin Ain=Bin 1 0 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 A3,B3 x x A3>B3 A3<B3 A3=B3 A3=B3 Comparing Inputs Outputs A2,B2 A1,B1 A0,B0 A>B A<B A=B x x x x x x x x x x x x A2>B2 x x A2<B2 x x