See discussions, stats, and author profiles for this publication at: https://www.researchgate.net/publication/356015490

Insulation Coordination Design for Grid-Connected Solid-State Transformers

Article in IEEE Journal of Emerging and Selected Topics in Power Electronics · November 2021

DOI: 10.1109/JESTPE.2021.3125708

CITATIONS

READS

6

266

9 authors, including:

Chunmeng Xu

Jia Wei

Georgia Institute of Technology

Georgia Institute of Technology

16 PUBLICATIONS 88 CITATIONS

18 PUBLICATIONS 99 CITATIONS

SEE PROFILE

SEE PROFILE

Liran Zheng

Maryam Saeedifard

Georgia Institute of Technology

Georgia Institute of Technology

35 PUBLICATIONS 453 CITATIONS

145 PUBLICATIONS 10,707 CITATIONS

SEE PROFILE

Some of the authors of this publication are also working on these related projects:

Medium-Voltage Current-Source Solid-State Transformer View project

Global Asset Monitoring, Management and Analytics (GAMMA) Platform View project

All content following this page was uploaded by Chunmeng Xu on 07 December 2021.

The user has requested enhancement of the downloaded file.

SEE PROFILE

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

1

1

Insulation Coordination Design for GridConnected Solid-State Transformers

Chunmeng Xu, Member, IEEE, Jia Wei, Member, IEEE, Liran Zheng, Member, IEEE, Xiangyu Han,

Member, IEEE, Maryam Saeedifard, Senior Member, IEEE, Rajendra Prasad Kandula, Member, IEEE,

Karthik Kandasamy, Member, IEEE, Deepak Divan, Life Fellow, IEEE, Lukas Graber, Senior

Member, IEEE

Abstract—The deployment of solid-state transformers (SSTs) in

medium-voltage distribution systems is facing various challenges,

especially the challenge of insulation coordination design against

grid-originated lightning impulses. In this paper, two challenges in

existing insulation coordination designs for grid-connected SSTs

are identified. One challenge is the mismatch between metal-oxide

varistor (MOV) protective levels and SST insulation strength, the

other challenge is the incompatibility of standard impulse test on

SST protective structures. To address the MOV selection

challenge, a novel lightning protection scheme is designed to

protect a single-stage SST where the semiconductor modules are

directly exposed to external lightning impulses. The in-lab

lightning impulse tests are performed to verify the overvoltage

attenuation performance of the prototyped lightning protection

scheme. To address the impulse test challenge, the surge withstand

capability of the protected SST is comprehensively evaluated with

a complete set of insulation coordination design procedures

beyond the BIL test. After these two challenges are addressed, a

discussion is presented on substituting conventional transformers

with the protected SSTs into insulation-coordinated distribution

systems to facilitate the field deployment of SSTs.

Index Terms—Basic insulation level (BIL), energy router,

medium-frequency

transformer (MFT),

metal

oxide

varistor (MOV), power electronic transformer (PET), solid-state

transformer (SST).

I. INTRODUCTION

S

OLID-STATE transformers (SSTs) provide a promising

solution to achieve voltage transformations in a compact

and flexible manner [1, 2]. Recent advancements in power

semiconductor devices have expedited the deployments of these

power electronic transformers (PETs) in medium-voltage (MV)

distribution-level grids [3, 4]. Multiple SST and PET

prototypes are targeting to replace their line-frequency

transformer (LFT) counterparts for increased flexibility and

controllability in MV systems [5-8]. Nevertheless, several

practical challenges currently exist for large-scale field

deployments of SSTs [2, 9].

A major deployment challenge for grid-connected SSTs is

1

Manuscript received July 31, 2021; revised September 26, 2021; accepted

Oct 16, 2021. Date of publication XX XX, XXXX; date of current version XX

XX, XXXX. The information, data, or work presented herein was funded by

the Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department

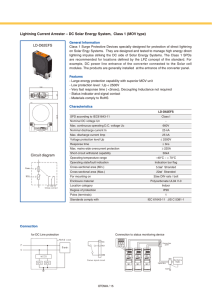

the fault protection [6, 10]. As illustrated in Fig. 1, various

types of faults can happen to a grid-connected SST and

numerous strategies have been proposed to protect SSTs under

these fault conditions [11-13]. The SSTs can maintain

operations under single phase to ground faults [14] and

overload conditions [15] on the load side or the lowvoltage (LV) side. The SSTs can also detect and mitigate their

internal faults like open-circuit faults [16, 17] and short-circuit

faults [18]. However, the SST protection against grid-side or

medium-voltage (MV) side faults is less studied in literature.

The overcurrent surges brought by ground faults can be

interrupted with circuit breakers or get limited by the SST

itself [19]. Comparatively, the overvoltage impulses are more

challenging to be handled by SSTs which are constructed with

voltage-sensitive semiconductor devices [20].

Although multiple studies in literature have chosen

overvoltage suppressors like metal-oxide varistors (MOVs) to

attenuate lightning and switching impulses [10, 11, 21], their

analyses on MOVs are lack of experimental verification and

thus neglecting many real-world phenomena of MOVs.

Moreover, the existing studies on SST insulation designs focus

primarily on the medium-frequency transformers (MFTs) [22,

23] without considering the grid-front semiconductor modules.

As illustrated in Fig. 1, the grid-front semiconductor devices are

exposed to the external surges before the isolation MFT in an

SST. If the grid-front semiconductor devices fail under a

lightning event, the overall SST becomes malfunctional no

matter whether the isolation MFT has a qualified basic lightning

impulse insulation level (BIL) or not. As of now, there is no

study focusing on the lightning protection scheme to help the

overall SST pass the lightning impulse tests. Therefore, the

challenges of insulation coordination designs for SSTs have not

been fully addressed in literature yet.

In this paper, two knowledge gaps are identified in the SST

insulation coordination designs: one is the mismatch between

the MOV protective levels and the SST insulation strength that

may cause breakdown damages in SSTs; the other is the

incompatibility of standard impulse test procedures on SST

protective structures that may fail to provide BIL ratings for

of Energy, under Award Number DE-AR0000899 in the CIRCUITS program

monitored by Dr. Isik Kizilyalli. (Corresponding author: Chunmeng Xu.)

The authors are with the School of Electrical and Computer Engineering,

Georgia Institute of Technology, Atlanta, GA 30332 USA (email:

chunmengxu@gatech.edu)

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Grid (MV) Side

Inside Solid-State Transformer

Load (LV)

Side

(a)

𝑉

LFT

6

1

2

3

4

2

Grid-originated:

1. Lightning impulse

2. Ground fault

3. Switching impulse

Inside converter:

4. Internal fault

Load-side:

5. Overload

6. Short circuit

Fig. 1. The typical faults that may happen to a grid-connected single-phase

SST. The illustrated SST topology is a 7.2 kV three-port single-stage modular

soft-switching SST (M-S4T) as reported in [24].

SSTs. To tackle the first challenge, a novel lightning protection

scheme (LPS) is constructed to provide sufficiently low

protective levels under lightning impulses. To tackle the second

challenge, this study discusses how to comprehensively

evaluate the surge withstand capability of an LPS-protectedSST without a standard-defined BIL rating. A flowchart of

insulation coordination design for SSTs is generalized in this

paper and a guideline on substituting LFTs with SSTs in

insulation-coordinated distribution systems is proposed. To the

author’s knowledge, it is the first time in literature that the

insulation coordination designs for SSTs are verified with the

experimental results of lightning impulse tests.

The rest of the paper is organized as follows. Section II

identifies the two challenges in SST insulation coordination

designs. Section III mitigates the first MOV selection challenge

by proposing a new LPS circuit for a 7.2 kV SST with

parameter design principles and frequency-dependent models.

Section IV validates the overvoltage attenuation performance

of the LPS prototype through in-lab lightning impulse tests.

Section V tackles the second impulse test challenge by

proposing a new set of insulation coordination design

procedures for SSTs. Section VI concludes the paper.

II. CHALLENGES IN INSULATION COORDINATION FOR SSTS

A. Standard Impulse Tests and BIL Ratings for LFTs

Insulation coordination, by its definition, refers to the

selection of the equipment insulation strength that is consistent

with the estimated external voltage stresses to obtain an

acceptable risk of failure [25]. A widely accepted parameter to

represent the standardized insulation strength of LFTs is the

BIL rating [26, 27]. According to the IEEE Std. C57.98 [26],

the BIL ratings of LFTs should be determined through impulse

tests with a full-wave lightning impulse. This full-wave

lightning impulse resembles a lightning disturbance that travels

along the transmission line before reaching a transformer [26].

The voltage of a full-wave lightning impulse should rise from

zero to its crest value in 1.2 μs and then decay to half of its crest

value at 50 μs, so that it is generally referred to as the 1.2/50 μs

lightning impulse in literature [28].

Inductive filter

(magnetic core)

Impulse generator

5

𝐿

𝑚

(b)

𝑉

MOV

𝑠𝑠

𝑚

SST

𝑠𝑠

Fig. 2. (a) A standard impulse test circuit for an LFT and (b) a common

configuration with an impulse generator, a MOV, a grid-front filter and an SST

in the lightning impulse protection studies of [11, 21].

The impulse generator circuit in Fig. 2 could generate the

standard 1.2/50 μs lightning impulse vLI at its output [29]. When

performing impulse tests on an LFT, the terminals of the LFT

are directly connected to the output of the impulse generator, so

that the same vLI can be measured from the LFT terminal as

illustrated in Fig. 2(a). For a 7.2 kV LFT under test, if the LFT

terminals do not exhibit any disruptive discharge that distorts

the vLI until 95 kV peak, the impulse test is considered as passed

and a 95 kV BIL rating is assigned to the LFT. On the other

hand, if the terminal-to-terminal insulation of this 7.2 kV LFT

fails before the 95 kV peak, the LFT terminal voltage will

collapse and the standard 1.2/50 μs waveshape is no longer

maintained. In short, the LFT impulse test codes [26] require

that a 1.2/50 μs lightning impulse must be measured from the

LFT terminal in order to determine the BIL rating of the LFT

under test.

B. MOV Selection and Impulse Test Challenges for SSTs

The first challenge on SST insulation coordination designs

happens when the breakdown voltage Vbr of an SST is even

lower than the maximum protective level VPL,max of a MOV. In

this study, the 7.2 kV SST to be protected has its Vbr at 15 kV.

The 15 kV is a conservatively estimated value on the insulation

strength of five cascaded submodules in this SST, because each

submodule is constructed with 3.3 kV SiC MOSFETs [30].

After adding a 10% voltage margin from the theoretically

maximum insulation strength of five cascaded submodules at

16.5 kV, the assumed breakdown voltage of this 7.2 kV SST is

15 kV or approximately 2 pu (the per-unit base is the SST

system voltage Vs).

On the other side, the protective levels VPL (also known as

clamping voltage) of distribution-class MOVs are proportional

to their maximum continuous operating voltage VM [31]. The

ratio of protective level VPL/VM is at least 2.32 ~ 2.48 under

front-of-wave (FOW) overvoltage surges, or 2.1 ~ 2.2 under

8/20 μs current impulse, or 1.7 ~ 1.85 under switching

impulse [32]. If choosing the VM of a MOV as equal to the Vs of

an SST according to the IEEE Std. C62.22 [32], the maximum

protective level VPL,max of the selected MOV during

overvoltage-clamping processes can be approximated as:

𝑉𝑃𝐿,𝑚𝑎𝑥 ≥ 𝐾𝐹𝑂𝑊 𝑉𝑀 = 𝐾𝐹𝑂𝑊 𝑉𝑠 ≈ 2.4𝑉𝑠

(1)

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Voltage

AC

(a)

DC

AC bus xfmr valve Converter DC bus

arrester winding unit DC bus arrester

arrester

arrester

Breakdown of power modules

(without MOV) – “BROKEN”

,

Smoothing

reactor arrester

LFT

, standard 1.2/50μs lightning

impulse in LFT BIL tests – “PASS”

3

DC cable

arrester

MFT

, discharge waveform

of MOV – “CLAMPED”

AC

(b)

DC

AC bus

arrester

Time [μs]

DC

LCL filter

arrester

AC

AC

DC-link

capacitor

DC

Dual active bridge

MFT

Fig. 3. Comparison on the standard lightning impulse vLI from LFT impulse

tests (peaks at BIL rating VBIL), a broken-down SST’s voltage waveform under

lightning impulse test with MOV protections (peaks at the breakdown voltage

Vbr of the SST), and a MOV-clamped voltage vmov under lightning impulse test

for the MOV-protected-SST (peaks at maximum protective level VPL,max of the

MOV).

where KFOW is the ratio of protective level under the FOW

overvoltage surges, the “worst-case scenario” of overvoltage

protection. In reality, most commercial MOVs have much

higher values of KFOW, like 3.65 for MOVs used in [11] and 4.4

for MOVs selected in this study. For adhering to the industrial

standards, an average value of KFOW = 2.4 within the standarddefined range of 2.32 – 2.48 [32] is used in the following

discussions.

According to (1), if an SST has a breakdown voltage Vbr

being less than 2.4 times of its system voltage Vs, this SST is

subject to the overvoltage damages brought by a parallelconnected MOV. For the 7.2 kV SST with a Vbr of 15 kV in this

study, it will be damaged by a 7.2 kV-rated MOV in the circuit

of Fig. 2(b) due to the following voltage relationship:

𝑉𝑃𝐿,𝑚𝑎𝑥 ≈ 2.4𝑉𝑠 > 2𝑉𝑠 ≈ 𝑉𝑏𝑟

(2)

In short, this mismatch between SST insulation strength and

MOV protective levels constitutes the MOV selection challenge

for SST insulation coordination designs. In order to tackle this

MOV selection challenge, a customized lightning protection

scheme (LPS) is proposed for the 7.2 kV SST in Section III and

then tested with a lightning impulse generator in Section IV in

this paper.

The second challenge on SSTs insulation coordination

designs comes from the conflicts among the LFT-compatible

impulse test standards, the BIL rating, and the surge withstand

capabilities of SSTs. As introduced above, a 7.2 kV LFT needs

to pass the standard impulse tests to obtain a 95 kV BIL rating.

Noteworthy to mention, the standard requires the LFT to be

tested without any surge arrester in the circuit as Fig. 2(a). In

contrast, it is almost impossible for a 7.2 kV SST to survive a

95 kV impulse without any protective device in the circuit,

considering the breakdown voltage of SST semiconductor

modules is normally 1.5 ~ 2.5 times of the continuous operating

voltage [9]. A broken-down SST will exhibit a “front-chopped”

voltage waveform (“BROKEN” curve in Fig. 3) with vigorous

short-circuit phenomena like overheating and sparking. After

MOVs and filters are included in the SST impulse test circuit

like Fig. 2(b), these surge suppressors will also clamp down the

(c)

Current

Source

Inverter

Lightning

Protection

Scheme

LC filter

Current

Source

Inverter

or

M-S4T

DC-link inductor

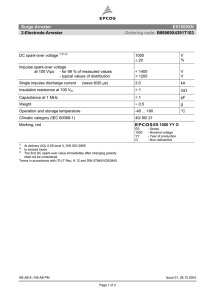

Fig. 4. (a) Typical HVDC converter station topology (single-phase equivalent

circuit) provided in IEC60071-5 with suggested arrester locations [33];

(b) Typical three-stage voltage-source SST topology with AC-side arrester

location reported in literature [10, 34]; (c) the single-stage, current-source MS4T with the LPS protection proposed in this paper.

original 1.2/50 μs waveshape (“CLAMPED” curve in Fig. 3)

through resistive dissipation based on the V-I characteristics of

surge suppressors.

Although the “surviving SST” scenario (“CLAMPED”

curve) is still distinguishable from the “broken-down SST”

scenario (“BROKEN” curve) in Fig. 3, neither of them qualifies

as the desired 1.2/50 μs waveform to pass a successful lightning

impulse test according to [26]. If the clamped vmov is measured

from an SST impulse test, the LFT test codes will consider the

SST as “failed” because the original 1.2/50 μs waveshape has

been distorted. As a result, a BIL rating cannot be assigned to a

“failed” SST test, although this SST has survived the 95 kV

lightning impulse with its protective devices. Without a testconfirmed BIL rating, the 7.2 kV SST is not accepted by

industrial standards to replace a 7.2 kV LFT into an insulationcoordinated distribution system. This is the direct consequence

caused by the impulse test challenge for SSTs. This impulse test

challenge will be discussed further in Section IV and Section V

in this paper.

C. Comparison with existing studies

Prior to this study, there have been mainly three categories of

insulation coordination studies on power converters. The first

category is the system-level coordination of withstand voltage

in HVDC converter stations that has been standardized by

IEC 60071-5 and lEC 60099-9 [33, 35, 36]. The second

category is the component-level coordination of protective

levels between the SST and the surge protection devices [34,

37, 38]. The third category is the structure-level coordination of

dielectric strength, clearance and creepage among insulation

layers within the power converters [39, 40].

In this study, the discussions on the MOV selection challenge

provide the first publicly-available lightning impulse test results

among the component-level coordination studies in SSTs. The

discussions on the impulse test challenge evaluate the

feasibility of BIL tests on SSTs for the first time in literature.

Comparatively, the BIL tests for HVDC converters are not

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

considered in their insulation coordination designs due to the

existence of winding-based converter transformers at the AC

grid interface. By referring to the general standards with LFTs

(i.e., IEEE Std C62.82.1 [25] and IEC 60071-1 [41]) instead of

the specialized ones with converters (i.e., IEC 60071-5 [33]),

this study actually sets a higher goal for insulation coordination

designs in SSTs than most other power converters. This is the

unique motivation and the main innovation of this study, which

reflects the practical challenges for SSTs to be deployed in

conventional AC distribution systems.

Comparatively, the single-stage current-source M-S4T

topology being protected in this study requires the highest level

of overvoltage surge protection as compared to the IECstandard HVDC station topology or the common three-stage

SSTs. As illustrated in Fig. 4(a), the AC-DC converter in an

HVDC station has no direct exposure to the external surges

because it is bounded by the inductance of converter

transformer, the smoothing reactor, and the DC-link

capacitor [33]. In this way, the requirements of surge withstand

capabilities in HVDC converters are much lower than the surge

capabilities in converter transformers. As illustrated in Fig. 4(b),

the dual active bridge in three-stage voltage-source SSTs is

interfaced by a DC-link capacitor, a rectifier, and a LCL filter

to the grid-front MOV [10, 34, 42].

Different from the HVDC station topology or the three-stage

voltage-source SSTs, the semiconductor devices in the M-S4T

prototype are more exposed to external disturbances. As

illustrated in Fig. 4(c), the grid-originated overvoltage surges

will reach the SiC MOSFETs right after the input LC filter,

which makes the overvoltage attenuation in this single-stage MS4T much more challenging than the protections for HVDC

converters or three-stage SSTs. Moreover, the input capacitive

filter in this current-source M-S4T cannot provide the same

degree of overvoltage attenuation as the DC-link capacitor in

voltage-source converters. In a sense, this M-S4T topology

becomes the “worst-case scenario” for SST protections and thus

it is selected as the case study in this paper.

III. LIGHTNING PROTECTION SCHEME

A. SST Topology

The SST to be protected in this study is a 7.2 kV, 50 kVA

single-phase single-stage M-S4T with the prototype photo

shown in Fig. 5 and the submodule topology shown in

Fig. 6 [43]. The MV-side SiC MOSFETs used in the 7.2 kV MS4T prototype are customized modules with 3.3 kV rating and

reverse-blocking features [30]. This M-S4T topology allows

modular cascading with five submodules and the bidirectional

power flow according to [8]. The M-S4T utilizes the singlestage current-source topology without AC-DC rectifier or DCAC inverter at the grid-front interface. Compared to three-stage

SST topologies, this single-stage M-S4T topology offers higher

efficiency, higher power density and lower electromagnetic

interference [43].

Besides the semiconductor devices, the MV-side LC filter is

also a vital component that should be protected by the LPS

under lightning impulses. In the M-S4T prototype, the filtering

4

LV

MV

HF

bridge xfmr bridge

Front view

Back view

Fig. 5. Photo of the 7.2 kV M-S4T prototype [24].

One S4T submodule

Lightning

Protection

Scheme (LPS)

vsst

MV filter

MV bridge

HF xfmr

LV bridge

LV filter

Fig. 6. Schematic of the S4T-LPS insulation coordination with the submodule

topology of the 7.2 kV M-S4T.

capacitance Cf is chosen for clamping the peak-to-peak voltage

ripple around 10% [24]. For suppressing the surge currents into

the M-S4T, a filtering inductor Lf with parasitic resistance of Rf

is used as shown in Fig. 7. This surge-suppressing air-core

inductor is a separate component from the ripple-reducing

magnetic-core inductor as illustrated in Fig. 6. Because the

magnetic-core inductor is rated at only 7 A (50 kVA by

7.2 kV), its magnetic core will easily get saturated under

hundreds of amperes of surge currents during lightning impulse

tests. Therefore, a separate surge-suppressing inductor is

designed to have an air core for the anti-saturation purpose, and

its optimal inductance will be determined in the next section.

In this paper, the LPS circuit is designed independently from

the M-S4T internal structure as long as the M-S4T input voltage

was kept below Vbr during the lightning impulse tests. The

remaining discussions of stress propagations and voltage

balancing problems inside the M-S4T structure belong to the

regime of converter internal faults, which have been studied

in [10, 44] and are not the focus of this paper.

B. LPS Design Principles and Parameter Selections

The design principles of the LPS circuits are presented in this

section. Fig. 7 illustrates the single-layer structure of an LPS

with its on-state equivalent circuit. The major task of LPS

design is to select an appropriate VM value of the MOV so that

the maximum voltage over the M-S4T input VSST,max is less than

the breakdown limit of M-S4T (VSST,max < Vbr) during lightning

impulse tests.

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

LM0

Impulse

generator

A0

A1

(b)

Fig. 7. (a) A single-layer structure of LPS with a MOV, a switch or spark gap

to isolate the MOV under nominal voltage, and the LC filter of the S4T; (b) is

the equivalent circuit of single-layer LPS during impulse tests for MOV

parameter selections.

L1

SW

M1

L2

M2

Cf

Fig. 8. Proposed LPS circuit with two layers of MOVs and inductors.

To find the maximum voltage over the M-S4T input during

impulse tests, assuming the MOV can be simplified as a step

voltage source with the step level of VPL,max during the current

discharging process like the vmov in Fig. 4. In Fig. 7(b), the

voltage over Cf can be derived as:

𝛼

= 𝑉𝑃𝐿,𝑚𝑎𝑥 [1 − (𝑐𝑜𝑠 𝜔 + 𝑠 𝑛 𝜔 ) 𝑒 −𝛼 ] (3)

𝑠𝑠

𝜔

where 𝛼 = 𝑓 /2𝐿𝑓 . Assuming the parasitic resistance Rf of aircore inductor Lf is negligible, the vsst expression can be

simplified with 𝑓 → 0, 𝛼 → 0:

≈ 𝑉𝑃𝐿,𝑚𝑎𝑥 [1 − 𝑐𝑜𝑠 𝜔 ]

(4)

The maximum voltage over the M-S4T filtering capacitor

VSST,max should be kept below Vbr to avoid any damage to the MS4T as expressed in (5). Additionally, the VSST,max is

proportional to the maximum protective level VPL,max of MOV:

𝑉𝑆𝑆𝑇,𝑚𝑎𝑥 = 2𝑉𝑃𝐿,𝑚𝑎𝑥 = 2𝐾𝐹𝑂𝑊 𝑉𝑀 ≤ 𝑉𝑏𝑟

(5)

Therefore, the selection criterion of MOV rating VM so as to

stay below the M-S4T insulation strength Vbr is:

𝑉𝑀 ≤

RM1

CM

=

(a)

𝑠𝑠

S1

RM0

,

MOV

Impulse

generator

LM1

S0

Switch

(or spark gap)

5

1 𝐾𝑏𝑟

1 2

𝑉 =

7.2 = 3 𝑘𝑉

2 𝐾𝐹𝑂𝑊 𝑠 2 2.4

(6)

where Kbr is the ratio between M-S4T breakdown voltage Vbr

and M-S4T rated voltage Vs, that is, 𝐾𝑏𝑟 = 𝑉𝑏𝑟 /𝑉𝑠 . Considering

the 𝐾𝑏𝑟 ≈ 2, 𝐾𝐹𝑂𝑊 ≈ 2.4 and 𝑉𝑠 = 7.2 kV, the upper limit of

MOV rated voltage is 3 kV according to (6). Referring to the

IEEE Std. C62.22 [32], the closed VM rating below 3 kV is

2.55 kV. Therefore, a 2.55 kV-rated MOV is selected for the

proposed LPS circuit to substitute the 7.2 kV-rated MOV that

is discussed in Section II.B.

However, the biggest problem of installing a 2.55 kV-rated

MOV in parallel to a 7.2 kV-rated M-S4T is the unwanted

Fig. 9. Frequency-dependent model of the gapped MOV used in LPS

simulation.

current conduction under the system voltage. A 2.55 kV-rated

MOV can discharge as large as 5 kA under the 10.2 kV system

peak voltage [32]. In order to disconnect the 2.55 kV-rated

MOV from the 7.2 kV system voltage under M-S4T normal

operations, an actively-switching power module or a passivelyswitching spark gap must be connected in series with the MOV

like Fig. 7(a).

The switch or the spark gap in Fig. 7(a) will inevitably bring

the switching-on delays in the MOV operations and the

overvoltage rise in vsst. A solution to minimize the overvoltage

rise during switching-on delays is to add another layer of MOV

in the LPS circuit like Fig. 8. The newly-added MOV M1 should

withstand the 7.2 kV system voltage by itself (𝑉𝑀 ≥ 7.2 kV).

When a lightning impulse comes, the M1 can act immediately

and clamp the overvoltage to an intermediate level, such as

35 kV when using a 7.65 kV-rated MOV [32]. Next, the M2 (a

2.55 kV-rated MOV) starts conducting after the switching-on

delay and further attenuates the overvoltage below 15 kV. The

inter-MOV inductor L1 will take the voltage difference between

M1 and M2, and then the input filtering inductor L2 will further

suppress the surge current and reduce the overvoltage from M2

to Cf.

The inductances of air-core inductors L1 and L2 are selected

to balance the current sharing between the two MOVs. The

lower-voltage-rated M2 has a lower resistance to naturally

discharge more current during the parallel conduction of M1 and

M2. Also, the M2 has a lower energy rating because the energy

rating of a MOV is proportional to its VM value [31].

Collectively, the M2 has a higher possibility of failure than M1

if the current sharing is uncontrolled. In order to determine the

minimal inductance of L1 and L2 that achieves the proper current

sharing among two MOVs, a frequency-dependent model of

LPS circuit is built to comprehensively represent the MOV

behaviors, especially the steep front effect that leads to the high

protective levels of MOVs in real-world scenarios.

C. Frequency Modeling and LPS Simulation

Improved from the traditional approach of modeling MOVs

as nonlinear resistors, the frequency-dependent model of

MOVs can better capture the steep front effect that causes a

higher protective level at a steeper-front surge [32, 45]. In this

paper, the comprehensive model of gapped MOVs is proposed

to include the switch (or spark gap) in series with the M2 as

shown in Fig. 9. This model demonstrates the steep front effect

by directing the current flowing through two nonlinear resistors

A0 and A1 with regards to the front time of input surges. The

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

6

more current flowing into A0 at a steeper-front surge will cause

a higher protective level of the overall MOV, because A0

exhibits a higher voltage drop at a given current than A1

according to (7) and (8) below:

𝑉𝐴0

=

𝑉𝑟𝑒𝑓

/ 4.96

𝐼𝐴

1.284 × ( 0 )

𝐼𝑟𝑒𝑓

, 𝐼𝐴0 < 3400 𝐴

𝐼𝐴

0.7836 × ( 0 )

𝐼𝑟𝑒𝑓

{

(7)

/ 0. 6

, 𝐼𝐴0 > 3400 𝐴

50

𝑉𝐴1

𝐼𝐴

= 0.9596 × ( 1 )

𝑉𝑟𝑒𝑓

𝐼𝑟𝑒𝑓

(8)

where 𝑉𝑟𝑒𝑓 = 𝑉𝑃𝐿, 0𝑘𝐴 /1.6. The VPL,10kA is the MOV protective

levels measured under 10 kA-peak current impulse in standard

8/20 μs waveshape. The 𝐼𝑟𝑒𝑓 is selected as 1 A. The threshold

value of 3400 A is determined through curve-fitting to the V-I

characteristics of A0 and A1 as given in IEEE Std. C62.22 [32].

Besides the nonlinear components A0 and A1, the remaining

components in Fig. 9 represent the parasitics in a gapped MOV.

As suggested by [31], these parasitics are computed as follows:

𝐿M0 = 0.2

𝐿M

𝑑

= 15 [μH];

𝑛

𝑑

[μH];

𝑛

M

M0

= 100

𝑑

= 65 [Ω];

𝑛

150

/ 9.

𝑀

𝑑

[Ω]

𝑛

𝑛

= 100 [pF]

𝑑

Fig. 10. Simulated current sharing among two MOVs of LPS circuit with

different inductance values of air-core inductors. These curves are used as the

parameter selection guidance for air-core inductors in the LPS circuit.

Lower-rated, Gapped MOV

Voltage [pu]

(i) Spark gap V-I

curve

1.7

[10 kA, 1.4 pu]

1.4

IV. LIGHTNING IMPULSE TESTS

A. LPS Prototype for the M-S4T

One difficulty of prototyping the proposed LPS circuit is to

implement the switch in the M2 branch. Using an active switch

[40 kA, 1.8 pu]

[20 kA, 1.6 pu]

(iii) V-I curve of a

gapped MOV

(9)

where d is the height of MOV in meters and n is the number of

parallel columns of metal-oxide stack in the MOV.

As reported in [46], the selected M2 for M-S4T protection has

a VM of 2.55 kV, a VPL,10kA value of 10.2 kV and a turning-on

threshold voltage of 12 kV. The selected M1 has a VM of 12.7 kV

and a VPL,10kA value of 38.5 kV. The reason for choosing a

higher-rated M1 is to get a higher energy rating in M1.

Meanwhile, as the LPS output voltage is determined by the

protective levels of M2, increasing the VM1 from

1.0 pu (7.65 kV) to 1.7 pu (12.7 kV) will only change the LPS

output voltage slightly by 2.3% according to simulation results.

The current sharing between two MOVs is simulated with the

inductance of L1 and L2 being swept from 1 μH to 1 mH under

the impulse test settings in Fig. 10. According to Fig. 10, when

the inter-MOV inductance is close to 1 μH, it is mainly the M2

that discharge the surge current from the impulse generator and

the peak current through M2 hits as high as 1800 A. By

increasing the inductance value, more current is deviated from

the M2 to flow through the M1. The crossover point of current

sharing happens at the inductance of 50 μH. At an inductance

of 150 μH, the peak current discharged by M1 is about two times

of the peak current discharged through M2, which matches up

with the ideal VM ratios of two MOVs. Therefore, an inductance

value of 150 μH is selected for the optimal current sharing

between two MOVs in the LPS prototype.

(ii) ZnO stack V-I

curve

Sparkover

region

Discharge Current

(log scale)

0.35

MCOV

1 mA

10 kA

Fig. 11. Illustrative V-I curve of the lower-rated gapped MOV M2

(VM = 2.55 kV) used in the LPS prototype [32, 47]. The per-unit base is the MS4T rating (also the system voltage) of 7.2 kV.

gives very high controllability but quite low reliability, because

the switch auxiliary components like gate drivers need the same

surge withstand capability to survive the impulse tests. The

other solution is to use passive switches like spark gaps with

high voltage ratings [32]. Cascading a spark gap with a gapless

metal-oxide (mostly zinc-oxide, ZnO) stack constitutes a seriesgapped MOV, which is the selected product for the LPS

prototype in this study.

The working principle of a series-gapped MOV is shown in

Fig. 11. The illustrated MOV is the 2.55 kV-rated M2. Different

from a gapless MOV with a continuous V-I curve as shown in

the curve (ii) of Fig. 11, a gapped MOV has a discontinuity in

its V-I curve that is caused by the sparkover event inside its

spark gap. This sparkover event switches the V-I curve of M2

from the spark gap path (curve (i)) to the ZnO stack

path (curve (ii)) with physically determined switching-on

delays. In this way, the M2 can safely withstand the 7.2 kV

system voltage following the spark gap curve (curve (i)) when

its applied voltage is below 1.7 pu or 12 kV (“OFF” state). The

M2 can also provide very low clamped voltage in current

discharging processes following the ZnO stack curve

(curve (ii)) when its applied voltage rises above 1.7 pu or

12 kV (“ON” state) [46]. The resulted V-I curve of M2 is shown

as curve (iii) in Fig. 11.

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

7

0.35 m

L1

M1

M2

L2

1.0 m

Fig. 14. Measured 1.2/50 μs lightning impulse with 90 kV peak under the noload condition of the impulse generator.

1.0 m

Cf

Mf

VM1

VLI

Fig. 12. Constructed LPS prototype with gapped MOVs, air-core inductors, and

the M-S4T capacitive filter [46].

Impulse

generator

IM1

Voltage

divider

ILI

VM1

Grounding

tapes

LPS

Prototype

Current

sensor

SST input

filter

Fig. 13. Lightning impulse test setup with the LPS prototype and the capacitive

filter of M-S4T [46].

A constructed LPS prototype for M-S4T protection is shown

in Fig. 12. In the LPS prototype, M1 has a VM value of 12.7 kV

and M2 has a VM value of 2.55 kV [47]. Both MOVs come from

Eaton® UltraSILTM series which have proprietary insulation

ceramic ring assemblies functioning as the spark gaps.

Improved from the concept circuit of Fig. 7, the M1 selected for

the LPS prototype is also a gapped MOV like M2 to evaluate the

LPS performance under the worst-case scenario. That is, the M1

also has a switching-on delay that may increase the LPS output

voltage during impulse tests. The air-core inductors, L1 and L2,

have the inductance of 152 μH and the parasitic capacitance of

8.83 pF [46]. They are wound with 30 kV-rated power cables

to avoid insulation failures during lightning impulse tests. The

capacitive filter of M-S4T is constituted by five pairs of 4.5 μF

capacitors with electronic-grade, gapless MOVs as backup

protection. The constructed LPS prototype has the most

conservative creepage and clearance design and thus its form

factor has not been optimized yet.

B. Lightning Impulse Test Setup

In the test setup shown in Fig. 13, an impulse generator was

used to generate a 90 kV-peak standard lightning impulse like

Fig. 14 when the LPS prototype was not connected to the

impulse generator. The Fig. 15(a) shows this no-load condition

of the impulse generator. In order to demonstrate the voltage

attenuation progressively over the LPS prototype, its three

IM1

ILPS

(b)

(a)

(c)

VM1

VM2

Vf

IM2

ILPS,f

(d)

If

Fig. 15. Lightning impulse test circuit to demonstrate the progressive

overvoltage attenuation over the LPS prototype: (a) Test 1 – no-load condition,

(b) Test 2 – M1 was connected, (c) Test 3 – M1 and M2 were connected,

(d) Test 4 – M1, M2, and the input capacitive filter of M-S4T was connected and

the final output of LPS was measured [46].

branches were introduced into the impulse test circuit one after

another as in circuits shown from Fig. 15(b) to Fig. 15(d). More

details about the lightning impulse test setup can be found

in [46].

C. Test Results

The lightning impulse test results have demonstrated the

layer-by-layer overvoltage attenuation throughout the LPS

prototype as illustrated in Fig. 16.

As shown in Fig. 16(a), the standard 1.2/50 μs lightning

impulse with 90 kV generated in Test 1 (Fig. 15(a)) was frontchopped by the M1 at 48 kV and then maintained around 20 kV

for several microseconds in Test 3 (Fig. 15(c)). Even though the

sparkover delay was 0.5 μs and the voltage clamping duration

was less than 5 μs, both the 48 kV sparkover voltage and the

20 kV discharge voltage of the M1 could have destroyed the

downstream M-S4T if the M1 were used alone. This

experimental observation had confirmed the dangers of using a

single MOV to protect the M-S4T as discussed in Section II.

At almost the same time that the M1 turned on, the M2 sparked

over at 15 kV (0.3 μs of sparkover delay) and then quickly

transited to a discharge voltage around 6.5 kV. The VM1 stayed

at 6.5 kV for an long period of time (i.e., 50 μs) with

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

8

(a)

(a)

Sparkover

−

Nonlinear conduction

through ZnO stack

−

−

−

.

(b)

(b)

−

Matched 𝑉𝑓, 𝑒𝑎𝑘

(2% error)

−

−

−

Fig. 16. Experimental (a) voltage waveforms and (b) current waveforms from

lightning impulse tests with different subcircuits of LPS prototype connected

to the impulse generator.

negligible decreases in its magnitude, which confirmed the

theoretical approach to use a step voltage source for presenting

the VM in Fig. 7.

With an almost-flat 6.5 kV discharge voltage over M2 for the

first 50 μs, the LC oscillation at the M-S4T filter side generated

a peak voltage of 13 kV, which was two times of the 6.5 kV

discharge voltage as predicted in (5). Also, the LC oscillation

helped to attenuate the sparkover noises that slightly overrode

the 15 kV limit in VM2. The final output voltage of the LPS

prototype, Vf, kept its voltage magnitude within 15 kV to avoid

damaging the downstream M-S4T as illustrated in Fig. 16(a).

In Fig. 16(b), the peak current through VM1 was about 2 times

of the peak current flowing through VM2, which matched up

with the simulated current sharing under 𝐿 = 150 μH in

Fig. 10. The measured current waveforms in Fig. 16(b) also

illustrated how the MOVs clamped the overvoltage surges from

the impulse generator by discharging a large current to the

ground. The measured no-load output current of an impulse

generator ILI was only a few amps in Test 1 (Fig. 15(a)). In this

way, the 300 J pre-charged energy in the impulse

generator (within C1 of Fig. 2) was outputted in the 1.2/50 μs

standard waveshape with 90 kV output voltage and negligible

output current. To the opposite, after connecting the MOVs in

Test 2 to Test 4 (Fig. 15 (b) to (d)), the same 300 J pre-charged

energy in the impulse generator was discharged through a large

output current and a reduced output voltage, like VM1 and IM1

compared to VLI and ILI.

If taking the flag of failure as the “chopped output voltage

and boosted ground current” during impulse tests according to

the IEEE Std. C57.98 [26], the LPS would automatically be

Fig. 17. Verification of the frequency-dependent model of LPS prototype with

references to experimental (a) 𝑀 voltage and (b) M-S4T capacitive filter

voltage (equivalently the 𝑆𝑆𝑇 ).

considered as “failed” the impulse tests despite no insulation

failure had ever occurred in the LPS. If the M-S4T prototype

were connected with the LPS under the impulse test, the LPSprotected-S4T would also be considered as “failed” the test

according to existing LFT standards. This conflict between

standard-defined test protocols and in-lab SST test phenomena

illustrated the “impulse test challenge for SSTs” as mentioned

in Section II.B. To tackle this challenge, new procedures of

insulation coordination designs for SSTs without using a

conventional BIL rating will be proposed in the next chapter.

D. Discussions

The frequency-dependent model of the LPS circuit

constructed in Section III.C can be verified with the impulse

test results. Fig. 17 presents the comparisons between the

impulse test results and the simulated waveforms when the LPS

is connected with the capacitive filter of M-S4T as in

Fig. 15(d). It can be found that the simulated waveforms match

closely with the lightning impulse test results. The simulated

peak voltage at M-S4T capacitive filter Vf is 13.2 kV, which

stays within 2% error range from the measured Vf of 13.0 kV.

Therefore, the accuracy of the frequency-dependent model for

the LPS prototype has been verified accordingly.

V. INSULATION COORDINATION DESIGN FOR SSTS

In the previous sections, the LPS prototype has been

designed, constructed and tested in lightning impulse test.

However, even if the LPS-protected-S4T can survive the

lightning impulse tests that had 90 kV-peak 1.2/50 μs impulse

at no-load condition, neither the LPS prototype nor the LPSprotected-S4T could be assigned a BIL rating of 90 kV.

Because the 90 kV-peak 1.2/50 μs waveshape got inevitably

distorted by the LPS in the test circuit. Without a 1.2/50 μs

voltage waveform being measured from the device under test,

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

BIL rating of LFT

5

(1) External

voltage

stresses

4

LINE- FREQ XFMR

PART 1

Voltage

[pu]

(2) Insulation

strength of LFT

PART 2

1

Fast-front

overvoltage

Lightning

μs range

Slow-front

overvoltage

Switching

μs to ms range

Temporary

overvoltage

s to min range

B2. Select submodule w/

breakdown voltage Vb

B1. Select LFT

2

(4) Protective levels of (5) Protective levels of

LPS

surge arrester

SOLID-STATE XFMR

A. Select external stress like:

Lightning impulse (1.2/50 μs voltage wave)

3

(3) Range of

Insulation

Strength of

SSTs

Time

Duration

Continuous

operating

voltage

PART 4

C1. Perform 1.2/50 μs

lightning impulse tests

onto the LFT

C2. Find number of

cascading submodule N

D1. Measure BIL rating

of LFT

D2. Calculate breakdown

voltage of SST: × 𝑉𝑏

E1. Select MOV

E2. Design LPS

F1. Read protective

levels of the MOV from

its datasheet

F2.1 Build frequency

dependent model of LPS

F2.1 Measure lightning

impulse protective level

of LPS by 1.2/50 μs test

NO

END

A. Insulation Coordination Design Flowchart for SSTs

In its fundamental form, the process of insulation

coordination design for power equipment is a comparison

between the external voltage stress and the internal insulation

strength as illustrated in Fig. 18 [25, 27, 51]. The criteria of

insulation coordination design are that if the external stress

overwhelms the insulation strength, proper surge protective

devices like MOVs should be installed to attenuate the external

stress [27, 52]. For example, the external lightning impulse and

switching impulse stresses in Fig. 18 (curve (1)) are possibly

higher than the insulation strength of an LFT (curve (2)). In this

case, a MOV is needed to clamp down the external stress to its

protective levels (curve (4)), which constantly stay lower than

the insulation strength of the LFT (curve (2)). Similarly, the

insulation coordination design criteria for SSTs require the LPS

to provide sufficiently low protective levels after clamping

down the same external stress (curve (5)), especially under fastfront overvoltage region like the lightning impulses.

The step-by-step flowchart in Fig. 19 shows both insulation

coordination design processes: one is for LFTs as defined in the

industrial standards and the other is for SSTs as proposed in this

paper. The insulation coordination design process for LFTs is a

standard approach generalized from IEEE standards and IEC

PART 3

Fig. 18. Illustration of insulation coordination design criteria for LFTs and

SSTs to survive different types of overvoltage surges.

the BIL rating cannot be calibrated, and the surge withstand

capability of LPS-protected-S4T cannot get represented by the

BIL rating.

Therefore, it is neither logical nor possible to use the same

LFT standards for impulse test on SSTs or any other power

electronic converter serving both “transformer” and

“converter” functions. In this section, a new insulation design

flowchart is proposed to evaluate the lightning impulse

withstand capabilities of the LPS-protected-SSTs without a BIL

rating. This flowchart supports the future insulation

coordination design procedures for SSTs. Also, the

considerations of substituting LFTs with LPS-protected-SSTs

in the insulation-coordinated distribution systems will be

preliminarily discussed in this section.

9

G1. Evaluate protective

ratios of LFT-MOV

coordination by

empirical equations as

provided in standards

G2. Calculate protective

ratios of SST-LPS

coordination

H1.

Acceptable

protective

ratio?

H2.

Acceptable

protective

ratio?

YES

NO

YES

I1. Check self-restoring

insulation issues like

clearance, parasitics and

partial discharge

I2. Check self-restoring

insulation issues like

clearance, parasitics and

partial discharge

J1. Insulation coordination

design for LFT

accomplished

J2. Insulation coordination

design for SST

accomplished

Procedure for Transformer Insulation Coordination Design:

1. Determination of external voltage stresses

2. Selection of transformer insulation strength

3. Application of surge-protective devices

4. Evaluation of protective ratios and self-restoring insulation

Fig. 19. Procedures for insulation coordination designs of LFTs and SSTs.

Procedures for LFTs are generalized from IEEE standards [25, 32, 48-50].

Procedures for SSTs are proposed to facilitate the future standardization of SST

insulation coordination designs.

standards including [25, 32, 48-50]. The proposed SST process

is an analogy to the standard LFT process with two

modifications. One modification is in Part 2: the SST insulation

strength can be determined through theoretical analyses before

performing destructive breakdown tests on SSTs. The other

modification is in Part 3: an LPS is chosen as the main

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

protective device for SSTs to replace the single, normal-rated

MOV.

Starting from Part 1 in Fig. 19, the external stress faced by

SSTs is the 1.2/50 μs lightning overvoltage impulse for the

insulation coordination design in this study. In Part 2, the

insulation strength of an LFT is usually determined

experimentally through standard lightning impulse tests to get

the BIL ratings as described above. To the opposite, it is

meaningless to perform LFT-equivalent impulse tests on an

unprotected SST at this step, because the semiconductor

modules will get damaged by the BIL-equivalent overvoltage.

Without performing destructive tests, the insulation strength of

an unprotected SST can be estimated through calculations. For

a general SST that cascades N submodules with a breakdown

voltage of Vb in each submodule, a reasonable assumption about

the maximum insulation strength of SST is × 𝑉𝑏 . Just like the

16.5 kV insulation strength for the M-S4T cascading five

submodules with 3.3 kV MOSFETs.

Surge protective devices are selected in Part 3 of both LFT

and SST design processes. The steps for LFTs are much more

straightforward than the steps for SSTs, because LFTs can

choose off-the-shelf MOV products and read MOV protective

levels from their datasheets. Comparatively, SSTs need

customized protective devices like an LPS. The lightning

impulse protective levels of an LPS should be estimated by the

frequency-dependent modeling and then confirmed by the inlab 1.2/50 μs lightning impulse tests.

After establishing the S4T – LPS coordination from Step B

to Step F2.3, the protective ratio (PR) of this S4T – LPS

coordination is calculated in Step G2 and then compared to the

PR criterion in Step H2. The PR criterion includes empirically

defined boundary values to ensure sufficient protective margins

in insulation coordination designs [25]. From the lightning

impulse tests presented in Section IV.C, the lightning protective

ratio PRL of S4T – LPS coordination can be calculated as:

𝑃

𝐿,𝑆4𝑇−𝐿𝑃𝑆

=

S4T theoretical insulation strength

LPS lightning impulse protective level

=

16.5 kV

= 1.26 > 1.2

13.0 kV

(10)

The S4T-LPS coordination qualifies as acceptable

coordination with regards to the lightning impulse protection,

because the value of PRL,S4T-LPS,exp is larger than the standardized

boundary value of 1.2 [26, 32]. If the protective ratio of S4T –

LPS coordination fails this PR criterion, the design process

should flow back to Step E2 and change the structure and

components inside the LPS. The design process cannot flow

back to Step B2 for increasing the insulation strength of M-S4T,

because it means more submodules to be added and then the

total volume and weight of M-S4T will be increased.

If the PR criterion is successfully met in Step H2, the M-S4T

insulation coordination design process will proceed to Step I2

and start checking the self-restoring insulation issues that are

related with clearance, parasitics and partial discharge [22,

53, 54].

In summary, without a BIL value representing the lightning

impulse withstand capability of an SST, the SST insulation

Transmission

Line

Breaker

MOV-protected-LFT

OK

10

Load

NO

LPS-protected-SST

LPS

SST

Fig. 20. Preferred deployment approach of using an LPS-protected-SST to

replace a MOV-protected-LFT in distribution systems from the perspective of

insulation coordination designs.

coordination design should go through the full process with

simulation and experiment as generalized in Fig. 19 to get the

PR value for representing the level of surge protection.

B. Deployment of LPS-Protected-SST in Distribution Systems

From the perspective of insulation coordination, an M-S4T

should not be used as a direct replacement for an LFT in

distribution systems because the single, normal-rated MOV

cannot effectively protect the M-S4T as described above.

Instead, it should be the LPS-protected-S4T replacing the

MOV-protected-LFT as shown in Fig. 20. This replacement

suggestion is based on the following analyses. To begin with,

suppose the BIL ratings in the system of Fig. 20 have been

coordinated properly following this relationship [49, 51]:

𝑉𝑙𝑖𝑛𝑒,𝐵 𝐿 ≥ 𝑉𝑏𝑟𝑒𝑎𝑘𝑒𝑟,𝐵 𝐿 > 𝑉𝐿𝐹𝑇,𝐵 𝐿 ≫ 𝑉𝑀𝑂𝑉,𝑃𝐿

(11)

where 𝑉𝑀𝑂𝑉,𝑃𝐿 refers to the protective levels of the MOV.

According to this chain of insulation coordination of (11), the

MOV should react to the overvoltage surges at a much lower

voltage than the transformer BIL rating to protect the LFT.

Next, the LFT, the circuit breaker, and the transmission line

may fail consecutively if the overvoltage levels still exceed

their respective BIL ratings and MOV protective limits (the

MOVs for the circuit breaker and the transmission line are not

shown in Fig. 20). In this way, the “risk of failures” of power

equipment within this distribution substation is properly

coordinated and effectively controlled.

If an SST wants to replace the LFT inside this voltage

coordination chain, the protective devices should be changed

from the MOV to the LPS at the same time to avoid the

challenge of mismatched protective levels. The new insulation

coordination chain for the field-deployed SST becomes:

𝑉𝑙𝑖𝑛𝑒,𝐵 𝐿 ≥ 𝑉𝑏𝑟𝑒𝑎𝑘𝑒𝑟,𝐵 𝐿 ≫ 𝑉𝑆𝑆𝑇,𝑏𝑟 > 𝑉𝐿𝑃𝑆,𝑃𝐿

(12)

Different from (11), the (12) shows that the inherent

breakdown voltage of an SST 𝑉𝑆𝑆𝑇,𝑏𝑟 is much lower than the

BIL rating of circuit breaker (suppose the circuit breaker is not

the solid-state type) [27]. The SST insulation strength is slightly

higher than the protective levels of its LPS device. This

difference in voltage coordination relationships leads to

different failure analyses of the two systems. In the LFT-based

system of Fig. 20, the failure rate of LFT is independent of its

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

protective MOV, and the LFT could still withstand a

considerate level of overvoltage after its protective MOV fails.

As a contrast, the SST in Fig. 20 has so limited overvoltage

margin by itself that the overall surge withstand capability and

failure rate of the LPS-protected-S4T is majorly determined by

its LPS. Once its LPS device fails, the M-S4T cannot withstand

most of the overvoltage impulses by itself. In this way, the

reliability of LPS becomes extremely important. This is one of

the reasons that a higher-rated MOV M1 has been chosen for the

LPS prototype to achieve higher reliability and a longer life

expectancy.

VI. CONCLUSION

This paper has addressed two challenges on insulation

coordination designs for grid-connected SSTs. The first

challenge is the higher lightning impulse protective levels of a

MOV than the insulation strength of an SST. The solution to

this first challenge is the proposed LPS circuit with sufficiently

low protective levels. Design principles and frequencydependent models of the LPS circuit are established to adjust

the protective levels and the current sharing among MOVs.

With the impulse generator set to output a standard 90 kV-peak

1.2/50 μs impulse during in-lab tests, the final output voltage of

the LPS prototype is only 13 kV, which is 15% lower than the

M-S4T breakdown voltage of 15 kV. With an experimentallyconfirmed protective ratio of 1.26, the S4T – LPS coordination

is qualified as the acceptable insulation coordination with

sufficient protective margin. The second challenge is the

incompatibility between impulse test codes and SST protective

devices, which causes that a BIL rating cannot be assigned to

the LPS-protected-SST. The solution to this conflict is the

proposed insulation coordination design flowchart for SSTs,

which completely evaluates the surge withstand capability of

SSTs under lightning impulses. Without a BIL rating as the

reference, the insulation coordination designs for SSTs need the

protective ratio of the S4T-LPS coordination to demonstrate the

degree of surge protection. Last but not least, the guidance on

substituting MOV-protected-LFT by an LPS-protected-SST is

also provided to control the risk of failure of SSTs and facilitate

the SST field deployment in the insulation-coordinated

distribution systems.

ACKNOWLEDGMENT

The information, data, or work presented herein was funded

by the Advanced Research Projects Agency-Energy (ARPA-E),

U.S. Department of Energy, under Award Number DEAR0000899 in the CIRCUITS program monitored by Dr. Isik

Kizilyalli. The views and opinions of authors expressed herein

do not necessarily state or reflect those of the United States

government or any agency thereof.

The authors would like to thank Brandon Royal in the Center

for Distributed Energy at Georgia Tech on assembling the LPS

prototype. The authors would also like to thank Prof. Peter

Zeller from the University of Applied Sciences Upper Austria

for his expert advice on MOV structures and applications

11

REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

[18]

[19]

J. E. Huber and J. W. Kolar, "Applicability of Solid-State Transformers

in Today’s and Future Distribution Grids," IEEE Trans. Smart Grid, vol.

10, no. 1, pp. 317-326, 2019.

M. Liserre, G. Buticchi, M. Andresen, G. D. Carne, L. F. Costa, and Z.

Zou, "The Smart Transformer: Impact on the Electric Grid and

Technology Challenges," IEEE Ind. Electron. Mag., vol. 10, no. 2, pp.

46-58, 2016.

W. Xu, Z. Guo, A. Vetrivelan, R. Yu, and A. Q. Huang, "Hardware

Design of a 13.8kV/3MVA PV Plus Storage Solid State Transformer

(PVS-SST)," IEEE Trans. Emerg. Sel. Topics Power Electron., 2021.

L. Zheng, R. P. Kandula, and D. Divan, "Current-Source Solid-State DC

Transformer Integrating LVDC Microgrid, Energy Storage and

Renewable Energy into MVDC Grid," IEEE Trans. Power Electron.,

2021.

Q. Zhu, L. Wang, A. Q. Huang, K. Booth, and L. Zhang, "7.2-kV SingleStage Solid-State Transformer Based on the Current-Fed Series

Resonant Converter and 15-kV SiC mosfets," IEEE Trans. Power

Electron., vol. 34, no. 2, pp. 1099-1112, 2019.

D. Dong, M. Agamy, J. Z. Bebic, Q. Chen, and G. Mandrusiak, "A

Modular SiC High-Frequency Solid-State Transformer for MediumVoltage Applications: Design, Implementation, and Testing," IEEE

Trans. Emerg. Sel. Topics Power Electron., vol. 7, no. 2, pp. 768-778,

2019.

A. Anurag, S. Acharya, S. Bhattacharya, T. R. Weatherford, and A.

Parker, "A Gen-3 10 kV SiC MOSFETs based Medium Voltage ThreePhase Dual Active Bridge Converter Enabling a Mobile Utility Support

Equipment Solid State Transformer (MUSE-SST)," IEEE Trans. Emerg.

Sel. Topics Power Electron., 2021.

L. Zheng et al., "SiC-Based 5 kV Universal Modular Soft-Switching

Solid-State Transformer (M-S4T) for Medium-Voltage DC Microgrids

and Distribution Grids," IEEE Trans. Power Electron., vol. 36, no. 10,

pp. 11326-11343, 2021.

S. A. Saleh et al., "Solid-State Transformers for Distribution Systems–

Part II: Deployment Challenges," IEEE Trans. Ind Appl., vol. 55, no. 6,

pp. 5708-5716, 2019.

T. Guillod, F. Krismer, and J. W. Kolar, "Protection of MV Converters

in the Grid: The Case of MV/LV Solid-State Transformers," IEEE

Trans. Emerg. Sel. Topics Power Electron., vol. 5, no. 1, pp. 393-408,

2017.

A. Anurag, S. Acharya, N. Kolli, S. Bhattacharya, and T. R.

Weatherford, "Protection Scheme for a Medium Voltage Mobile Utility

Support Equipment based Solid State Transformer (MUSE-SST)," in

Ann. Conf. IEEE Ind. Electron. Soc., 2020, pp. 1431-1436.

N. B. Y. Gorla, S. Kolluri, M. Chai, and S. K. Panda, "A Novel OpenCircuit Fault Detection and Localization Scheme for Cascaded H-Bridge

Stage of a Three-Stage Solid-State Transformer," IEEE Trans. Power

Electron., vol. 36, no. 8, pp. 8713-8729, 2021.

L. Zheng, R. P. Kandula, K. Kandasamy, and D. Divan, "Stacked LowInertia Converter or Solid-State Transformer: Modeling and Model

Predictive Priority-Shifting Control for Voltage Balance," IEEE Trans.

Power Electron., vol. 36, no. 8, pp. 8934-8952, 2021.

G. D. Carne, M. Langwasser, R. Zhu, and M. Liserre, "Smart

Transformer-Based Single Phase-To-Neutral Fault Management," IEEE

Trans. Power Del., vol. 34, no. 3, pp. 1049-1059, 2019.

J. Kucka and D. Dujic, "Current Limiting in Overload Conditions of an

LLC-Converter-Based DC Transformer," IEEE Trans. Power Electron.,

vol. 36, no. 9, pp. 10660-10672, 2021.

N. Zhao, J. Liu, Y. Shi, J. Yang, J. Zhang, and X. You, "Mode Analysis

and Fault-Tolerant Method of Open-Circuit Fault for a Dual ActiveBridge DC–DC Converter," IEEE Trans. Ind. Electron., vol. 67, no. 8,

pp. 6916-6926, 2020.

S. Ouyang, J. Liu, X. Chen, and Y. Yang, "Control Strategy for SinglePhase Open-Circuit Operation of a Modular Solid-State Transformer,"

IEEE Trans. Power Electron., vol. 34, no. 9, pp. 8555-8573, 2019.

R. Zhao, J. Gu, C. Wang, and Y. Wang, "On-Line Identification of HighFrequency Transformer Short-Circuit Parameters Based on

Instantaneous Phasor Method," IEEE Trans. Emerg. Sel. Topics Power

Electron., 2021.

H. Weng, J. Li, K. Shi, M. Chen, P. T. Krein, and D. Xu, "A DC Solid

State Transformer with DC Fault Ride-through Capability," IEEE Trans.

Emerg. Sel. Topics Power Electron., 2021.

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

[20]

[21]

[22]

[23]

[24]

[25]

[26]

[27]

[28]

[29]

[30]

[31]

[32]

[33]

[34]

[35]

[36]

[37]

[38]

[39]

[40]

[41]

[42]

[43]

[44]

[45]

M. A. Hannan et al., "State of the Art of Solid-State Transformers:

Advanced Topologies, Implementation Issues, Recent Progress and

Improvements," IEEE Access, vol. 8, pp. 19113-19132, 2020.

S. Madhusoodhanan, D. Patel, S. Bhattacharya, J. A. Carr, and Z. Wang,

"Protection of a transformerless intelligent power substation," in IEEE

Int. Symp. Power Electron. Distrib Gen. Syst., 2013, pp. 1-8.

M. Mogorovic and D. Dujic, "100 kW, 10 kHz Medium-Frequency

Transformer Design Optimization and Experimental Verification,"

IEEE Trans. Power Electron., vol. 34, no. 2, pp. 1696-1708, 2019.

P. Czyz, T. Guillod, F. Krismer, J. Huber, and J. W. Kolar, "Design and

Experimental Analysis of 166 kW Medium-Voltage Medium-Frequency

Air-Core Transformer for 1:1-DCX Applications," IEEE Trans. Emerg.

Sel. Topics Power Electron., 2021.

L. Zheng, X. Han, R. P. Kandula, K. Kandasamy, M. Saeedifard, and D.

Divan, "7.2 kV three-port single-phase single-stage modular softswitching solid-state transformer with active power decoupling and

reduced dc-link," in IEEE Appl. Power Electron. Conf. Expo., 2020, pp.

1575-1581.

IEEE Standard for Insulation Coordination--Definitions, Principles,

and Rules, IEEE Std C62.82.1, 2010.

IEEE Guide for Transformer Impulse Tests, IEEE Std C57.98, 2011.

A. R. Hileman, Insulation coordination for power systems. CRC Press,

1999.

IEEE Standard for High-Voltage Testing Techniques, IEEE Std 4, 2013.

E. Kuffel, W. Zaengl, and J. Kuffel, High Voltage Engineering

Fundamentals, 2nd ed. 1986.

X. Han, L. Zheng, R. P. Kandula, K. Kandasamy, D. Divan, and M.

Saeedifard, "Characterization of 3.3 kV Reverse-Blocking SiC Modules

for Use in Current-Source Zero-Voltage-Switching Converters," IEEE

Trans. Power Electron., vol. 36, no. 1, pp. 876-887, 2020.

IEEE Standard for Metal-Oxide Surge Arresters for AC Power Circuits

(>1 kV), IEEE Std C62.11, 2012.

IEEE Guide for the Application of Metal-Oxide Surge Arresters for

Alternating-Current Systems Amendment 1: Supplement to Consider

Energy Handling Capabilities, IEEE Std C62.22a, 2013.

Insulation co-ordination – Part 5: Procedures for high-voltage direct

current (HVDC) converter stations, IEC 60071-5, 2014.

X. Rong, "Insulation Coordination of Solid State Devices Connected

Directly to the Electric Power Distribution System," M.S. thesis,

Arizona State University, 2017.

Surge arresters - Part 9: Metal-oxide surge arresters without gaps for

HVDC converter stations, IEC 60099-9, 2014.

V. Hinrichsen, "Overview of IEC Standards' recommendations for

lightning protection of electrical high-voltage power systems using

surge arresters," in Int. Conf. Lightning Protection, 2014, pp. 1701-1707.

T. Guillod, F. Krismer, R. Färber, C. M. Franck, and J. W. Kolar,

"Protection of MV/LV solid-state transformers in the distribution grid,"

in Ann. Conf. IEEE Ind. Electron. Soc., 2015, pp. 3531-3538.

J. Carr, W. Zhenyuan, S. Bhattacharya, and D. Patel, "Transient

overvoltage rating and BIL of the transformerless intelligent power

substation," in IEEE Power & Energy Soc. General Mtg, 2013, pp. 1-5.

M. Mogorovic and D. Dujic, "Computationally Efficient Estimation of

the Electric-Field Maximums for the MFT Insulation Coordination," in

IEEE Energy Convers. Cong. Expo., 2019, pp. 7118-7123.

S. Ozdemir, N. Altin, A. Nasiri, and R. Cuzner, "Review of Standards

on Insulation Coordination for Medium Voltage Power Converters,"

IEEE Open J. Power Electron., vol. 2, pp. 236-249, 2021.

Insulation co-ordination - Part 1: Definitions, principles and rules, IEC

60071-1, 2019.

J. Carr, W. Zhenyuan, S. Bhattacharya, K. Hatua, and S.

Madhusoodhanan, "Overloading and overvoltage evaluation of a

Transformerless Intelligent Power Substation," in IEEE Power &

Energy Society General Meeting, 2013, pp. 1-5.

L. Zheng, R. P. Kandula, and D. Divan, "Soft-Switching Solid-State

Transformer With Reduced Conduction Loss," IEEE Trans. Power

Electron., vol. 36, no. 5, pp. 5236-5249, 2021.

J. Burkard and J. Biela, "Design of a Protection Concept for a 100-kVA

Hybrid Transformer," IEEE Trans. Power Electron., vol. 35, no. 4, pp.

3543-3557, 2020.

Q. Yi et al., "Snubber and Metal Oxide Varistor Optimization Design of

Modular IGCT Switch for Overvoltage Suppression in Hybrid DC

Circuit Breaker," IEEE Trans. Emerg. Sel. Topics Power Electron.,

2020.

[46]

[47]

[48]

[49]

[50]

[51]

[52]

[53]

[54]

12

C. Xu et al., "Lightning Impulse Protection for Grid-connected Solidstate Transformers," in IEEE Energy Convers. Cong. Expo., Detroit, MI,

2020, pp. 6057-6064.

Eaton, "UltraSIL™ Polymer-Housed Evolution™ (10 kA) IEEE® Surge

Arresters for MV Systems to 36 kV," CA235018EN ed, 2017.

IEEE Guide for the Application of Insulation Coordination, IEEE Std

1313.2, 1999.

IEEE Guide for Recommended Electrical Clearances and Insulation

Levels in Air-Insulated Electrical Power Substations, IEEE Std 1427,

2007.

IEEE Recommended Practice for Testing Transformers and Inductors

for Electronics Applications, IEEE Std 389, 2020.

L. Gan, "Insulation Coordination in the Alberta Interconnected Electric

System Part 1," in Alberta Power Ind. Conf., 2015.

IEEE Guide for the Application of Surge-Protective Components in

Surge-Protective Devices and Equipment Ports--Overview, IEEE Std

C62.42.0, 2017.

L. Zheng, R. P. Kandula, and D. Divan, "Robust Predictive Control for

Modular Solid-State Transformer With Reduced DC Link and Parameter

Mismatch," IEEE Trans. Power Electron., vol. 36, no. 12, pp. 1429514311, 2021.

T. Guillod, R. Faerber, D. Rothmund, F. Krismer, C. M. Franck, and J.

W. Kolar, "Dielectric Losses in Dry-Type Insulation of MediumVoltage Power Electronic Converters," IEEE Trans. Emerg. Sel. Topics

Power Electron., vol. 8, no. 3, pp. 2716-2732, 2020.

Chunmeng Xu (S’16–M’21) received the B.S.

degree in electrical engineering from Xi'an Jiaotong

University, Xi'an, China in 2016, the M.S. and the

Ph.D. degree in electrical and computer engineering

from Georgia Institute of Technology, Atlanta, GA,

USA in 2019 and 2021 respectively. She is currently

a Research Scientist with ABB Raleigh Research

Center, Raleigh, NC, USA. Her research interests

include solid state circuit breakers, multiphysical

design and prototyping, and advanced switchgear for

DC system protections.

Jia Wei (S'16–M’21) received the B.S. degree in

electrical and computer engineering from Ohio State

University, Columbus, OH, USA in 2015 and the

M.S. degree in electrical and computer engineering

from Georgia Institute of Technology, Atlanta, GA,

USA in 2016. He is currently working toward the

Ph.D. in electrical and computer engineering at

Georgia Institute of Technology. His research

interests include novel dielectric materials and gas

discharge theories.

Liran Zheng (S’17–M’21) received the B.S. degree

in control engineering from Tsinghua University,

Beijing, China, in 2016, and the M.S. degree in

electrical and computer engineering from Georgia

Institute of Technology, Atlanta, GA, USA, in 2018,

where he is currently working towards the Ph.D.

degree with the Center for Distributed Energy.

He was a Visiting Student with the Center for

Power Electronics Systems, Virginia Polytechnic

Institute and State University, Blacksburg, VA, USA,

and The University of Texas at Austin, Austin, TX, USA, in summer 2015 and

fall 2014, respectively. His research interests include power electronics and

distributed energy resources.

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

13

Xiangyu Han (S’15–M’20) received the B.Eng

degree in electrical engineering from Xi’an Jiaotong

University, Xi'an, China, in 2014 and the Ph.D. degree

in the electrical and computer Engineering from

Georgia Institute of Technology, Atlanta, GA, USA,

in 2020. He is currently a Senior Electronic Design

Engineer with Tesla, Pala Alto, CA, USA. His

research interests include wide-bandgap power

devices and applications of power electronics in

power systems.

is funded by clean-tech venture capital firm Khosla Ventures and investor Bill

Gates. He currently serves as the Chief Scientist and Founder of Varentec. He

is also the Scientific Founder of two additional companies—Innovolt, based in

Atlanta, which makes next-generation power protection and asset management

devices and where he serves on the Board, and Soft Switching Technologies

Corporation, where he served as the CEO and developed a range of devices to

help manufacturing facilities ride-through power disturbances. He has also been

a Professor in electric engineering at the University of Wisconsin-Madison,

Madison, WI, USA. He has more than 250 papers and holds 50 issued and

pending patents.

Dr. Divan is a member of the U.S. National Academy of Engineering. He is

the first recipient of the IEEE William E. Newell Power Electronics Award, and

a past President of the IEEE Power Electronics Society

Maryam Saeedifard (SM’11) received the Ph.D.

degree in electrical engineering from the University

of Toronto, Toronto, Canada, in 2008.

She is currently as Associate Professor in the

School of Electrical and Computer Engineering at

Georgia Institute of Technology, Atlanta, GA, USA.

Prior joining Georgia Tech, she was an Assistant

Professor in the School of Electrical and Computer

Engineering at Purdue University, West Lafayette, IN,

USA. Her research interests include power electronics

and applications of power electronics in power systems.

Lukas Graber (S’02–M’03–SM’11) received the

Diploma and doctorate degrees in electrical

engineering from ETH Zurich, Zürich, Switzerland, in

2002 and 2009, respectively.

He is currently an Associate Professor in the

School of Electrical and Computer Engineering at

Georgia Institute of Technology, Atlanta, GA, USA.

Before he joined Georgia Tech, in 2015, he was with

the Center for Advanced Power Systems, Florida

State University—initially as a Postdoctoral Research

Associate and later as a Research Faculty Member. His research interests

include superconducting power cables and fault current limiters, cryogenic

power electronics, supercritical dielectric materials, ultrafast mechanical

switchgear, short-circuit forces in substations, and grounding aspects of power

distribution on future all-electric ships. He is a member of the CIGRE, CSA,

and Electrosuisse. He serves on the Board of Directors for CSA, an Editor for

select issues of the IEEE Transactions on Applied Superconductivity, and

contributes to standard committees, taskforces, as well as study committees

within IEEE and CIGRE.

Rajendra Prasad Kandula (S’10–M’14) received

the B.E degree in electrical engineering from NIT,

Nagpur, India in 2002, the M.E degree from IISC,

Bangalore, India in 2004, and the Ph.D. degree in

electrical engineering from Georgia Institute of

Technology, Atlanta, GA, USA in 2014.

He worked for three years in, Bharat Heavy

Electricals Limited (BHEL) R&D, Hyderabad, as

Design Engineer in the area of industrial drives and

PV applications. He worked at Varentec, Santa Clara,

as a Principal Engineer, mainly working in the area of development of power

flow controllers and hybrid transformers for meshed transmission systems. He

is currently working as a Chief Engineer with Center for Distributed Energy,

Georgia Tech, Atlanta, USA. His main research interests include applications

of power electronics for utility applications such as hybrid transformers, solid

state transformers, hybrid filters, grid-forming converters, etc.

Karthik Kandasamy (S’11–M’16) received the B.E.

degree in Electrical and Electronics Engineering from

PSG College of Technology, Anna University (India)

in 2008, and the M.Sc. degree in Power Engineering

and the Ph.D. degree in the field of Power Electronics

from Nanyang Technological University (Singapore)

in 2011 and 2016 respectively.

He was associated with the Rolls-Royce@Nanyang

Technological University (Singapore), the Center for

Distributed Energy at Georgia Institute of Technology