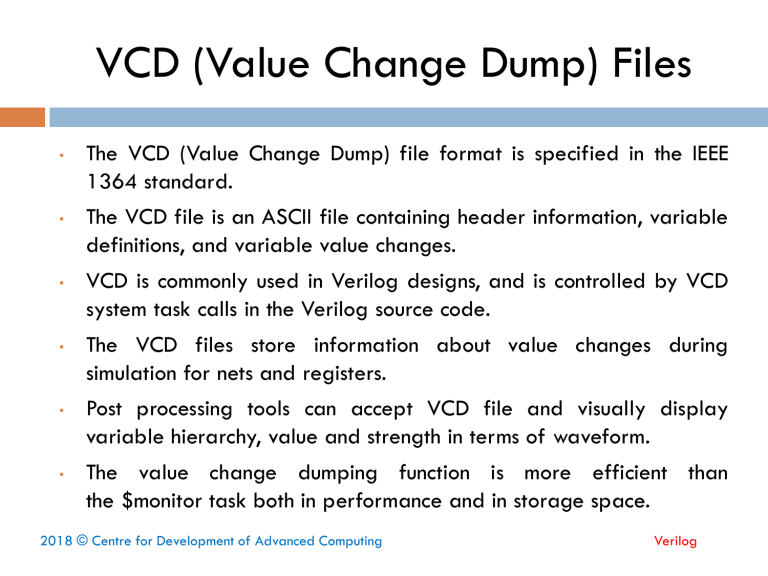

VCD (Value Change Dump) Files • • • • • • The VCD (Value Change Dump) file format is specified in the IEEE 1364 standard. The VCD file is an ASCII file containing header information, variable definitions, and variable value changes. VCD is commonly used in Verilog designs, and is controlled by VCD system task calls in the Verilog source code. The VCD files store information about value changes during simulation for nets and registers. Post processing tools can accept VCD file and visually display variable hierarchy, value and strength in terms of waveform. The value change dumping function is more efficient than the $monitor task both in performance and in storage space. 2018 © Centre for Development of Advanced Computing Verilog VCD (Value Change Dump) Files • The files saved in the VCD format contain several sections that describe : • • • • • File creation date and time Version number $timescale directive Signals specification $dumpvars task which defines which variables to dump into a file 2018 © Centre for Development of Advanced Computing Verilog Some useful System Tasks for VCD operations with syntax • $dumpfile(name) • $dumpvars • $dumpvars(level, list_of_variables_or_modules) • $dumpoff • $dumpon • $dumpall • $dumplimit • $dumpflush 2018 © Centre for Development of Advanced Computing Verilog VCD System Tasks • • $dumpfile is used to create a VCD file • $dumpfile; //Default file name is dump.vcd • $dumpfile(“file name”); $dumpvars is used to specify variables to be dumped • $dumpvars(level, variables or modules); level how many level of hierarchy of modules has to be dumped to the VCD file. 1 will dump all variables in current specified module, not modules instantiated inside current specified module. 0 will dump all variables in current specified module and modules instantiated inside current specified module. 2018 © Centre for Development of Advanced Computing Verilog VCD System Tasks $dumpvars(1, TB); //Dumps values of A and B $dumpvars(1, TB.u3); //Dumps values of C and D $dumpvars(2, TB); //Dumps values of A, B, C and D $dumpvars(0, TB); //Dumps values of A, B, C, D, E1 and E2 $dumpvars(1, TB.u3, A); //Dumps values of A, C and D $dumpvars(1, TB.u3.u1,TB.u3); //Dumps value of C, D and E1 2018 © Centre for Development of Advanced Computing Verilog VCD System Tasks • • • $dumpall is used to write current value of all selected variable • $dumpall; $dumpon/$dumpoff is used to resume or stop dumping process • $dumpoff; //stop dumping • $dumpon; //resume dumping $dumpflush is used to empty VCD buffer and ensure all data in buffer is written to VCD file. It is used to update the dump file while simulation is running. • $dumpflush; 2018 © Centre for Development of Advanced Computing Verilog Keyword Inside VCD File • • • • • • $comment $date $timescale $var $scope $end 2018 © Centre for Development of Advanced Computing Verilog • • • • • • $dumpon $dumpoff $dumpvars $dumpall $version $upscope VCD Keywords • $comment represents comment inside a VCD file • • • $comment This is the comment $end $comment Multi-line Comment1 Multi-line Comment2 $end $timescale specifies time scale which was used during simulation • $timescale time_number time_unit $end 2018 © Centre for Development of Advanced Computing Verilog VCD Keywords • $date specifies the date on which VCD file was created • • $date data_in_text_format $end $upscope indicates change of scope to next higher level in design hierarchy. • $upscope $end 2018 © Centre for Development of Advanced Computing Verilog VCD Keywords • $var section specifies properties and identification code of variable been dumped. • • $scope specifies scope of variable been dumped • • $var var_type size identifier_code var_name $end $scope module modulename/instance_name $end $version indicates version of VCD writer and system task $dumpfile used to create the file • $version version_text system_task $end 2018 © Centre for Development of Advanced Computing Verilog Design Example module comb_logic (a, b, c, d, e); input a, b, c, d; output e; wire x, y; assign x= a & b; assign y= c | d; assign e= x ^ y; endmodule 2018 © Centre for Development of Advanced Computing Verilog VCD Test Bench (1/3) module testbench; reg a, b, c, d; wire e; comb_logic u0 (a, b, c, d, e); 2018 © Centre for Development of Advanced Computing Verilog VCD Test Bench (2/3) // VCD initial block initial begin $dumpfile; $dumpvars(1, testbench, u0.x, u0.y); #20 $dumpoff; #30 $dumpon; #5 $dumpall; end 2018 © Centre for Development of Advanced Computing Verilog VCD Test Bench (3/3) initial begin forever begin a=$random; b=$random; c=$random; d=$random; #3; end end endmodule 2018 © Centre for Development of Advanced Computing Verilog Questasim VCD Feature • • Creating VCD file without using Verilog System Tasks vsim –novopt testbench //Start TB simulation vcd file vcd_filename //Create VCD file vcd add var1 var2 //Add variables to be dumped add wave * //Add wave window run time_value //Run Simulation Converting a VCD file to a waveform file vcd2wlf vcd_filename wlf_filename.wlf 2018 © Centre for Development of Advanced Computing Verilog