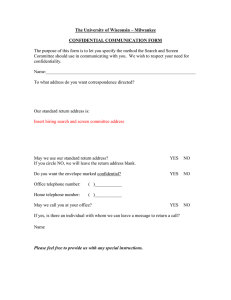

Implementing An LCD Interface In A Customizable ARM7 Microcontroller Using The CAP7 Metal Programmable Block What is CAP7? JTAG Main OSC PLL PMC WDT AIC PIT 32K OSC RTT RC OSC POR ICE PLL EBI ARM7TDMI MPLIB 250K/450K ASIC gates SHWDC GPBREG Static Mem. CF NAND Flash SDRAM SRAM SRAM 96KB 64KB POR 6-layer AHB Matrix ROM (256KB) AMBA Bridge Peripheral DMA Controller APB USB FS Device SPI PIO x64 Timer x3 USART USART ADC Confidential 2 CAP7 Features Processor: ARM7TDMI CPU up to 80MHz Memory: 160K Bytes SRAM, 256K Bytes Boot ROM External Bus Interface Peripherals: - - SDRAM, Mobile SDRAM Static Memories, NOR Flash and Compact Flash, NAND Flash USB2.0 Full Speed Host Device – 6 end-points 21 * Channel Peripheral DMA controller 1 * SPI 3 * 16-bit Timer/Counters 2 * USARTs 2 * 32 bit PIO 1* 8-channel 10-bit ADC Full-featured System Controller 32 Channel Interrupt Controller • Reset Controller w/two POR cells • Shut Down Controller • 20 battery backup registers • Advanced Power Management • Debug Unit 250K/450K Gates Metal Programmable Block (6LM) Confidential 3 Application: Adding An LCD Interface Confidential 4 Design Requirements Low Cost ARM7TDMI CPU Fast on chip memory for execution of GUI OS / Application code Display Support: Passive LCD’s Monochrome LCD’s up to 640x480 pixels with Frame Rate Modulated Grays (16 shdaes) Color LCD’s up to 640x480 pixels 12 bit FRM color, or 256 color pallete TFT LCD’s up to 800x600 24 bit color or 256 color pallette Resistive Touch Panel – 4 Wire and 5 Wire Internal frame buffer memory for monochrome and small color displays Independent Dual Port Line Buffer for entire LCD Scan Line LCD refreshed without stealing processor cycles for responsive interfaces. Confidential 5 LCD Refresh Consumes The Bus Memory ARM7 CPU Application Code And Data Display Frame Buffer LCD Controller 640x480 = 1,228,800 Bytes Display Refresh = 1.2 MBytes @ 60 Hz = 73,728,000 bytes/second Confidential 6 Concurrent Execution and LCD Refresh On Chip Memory Application Code ARM7 CPU And Data External Memory Frame Buffer LCD Controller 640x480 = 1,228,800 Bytes Confidential 7 LCD Usage of CAP7 Resources JTAG LCD Timing Generator ICE ARM7TDMI PIXEL Formatter Color Pallete (DualPort) LineBuffer (DualPort) AHB MASTER 2 AHB MASTER 1 EBI Control Registers External RAM Static Mem. SRAM (64KB) SDRAM Frame Buffer 6-layer AHB Matrix AMBA Bridge APB ROM (256KB) Peripheral DMA Controller SRAM (96KB) USB FS Device SPI PIO x64 Timer x3 USART USART ADC Confidential 8 CAP7 Customization – Fixed Logic Placement and Components: routing is fixed Hard Macro Timing is fixed, STA on internal paths not needed ARM7 HMATRIX System RAM/ROM Full backannotated timing views for STA to/from these areas PDC AHB/APB Bridge EBI APB Peripherals ASCs DPRs Confidential 9 CAP7 Customization – Atmel Gates Components: Delivered a pre- Battery Backup synthesized gates JTAG logic Design Centers will need to place, route, and extract timing MP Macro Interface DPR BIST Gives freedom to customize* (within restrictions) In most cases, customer can used as delivered * This is not part of the default quick turn flow Confidential 10 CAP7 Customization – Customer RTL Area designated for the customer’s logic Components: Custom MP Confidential 11 CAP7 Customization – Atmel RTL IP from Atmel to Components: be used directly by the customer Atmel IP Delivered as protected RTL, gates* Design centers will need to assist customers for integration * Available views will depend on IP Confidential 12 CAP7 Customization – I/O I/O placement is Components: fixed Digital I/O I/O sites can be customized* in metal to change drive strengths, pullup/pulldown/bu s holder. MP I/O sites can be converted in additional power/gnd pads if needed* * This is not part of the default quick turn flow Confidential 13 CAP7 MP Block Interface - Clocks from APMC and APB bridge - Interrupts to AIC - APB Peripherals to Hard Macro Bridge and PDC MP Block 4x4 AHB Slaves and 4 AHB Masters are connected to the MBBlock 4x4 AHB Slaves 4 AHB Masters 15 APB Slaves available to the MPBlock MP Interface Wrapper and BIST are located in the MP area so actual gates available to the customer will be less than 450K 15 APB Slaves ... MP Interface – Scan W rapper ... ChipID USB PHY Ext ChipID BIST Clock (42) DPR 2kx16 BIST MPBlock Custom AREA DPR 2kx16 ITs (19) 13 PDC channels The USB transceiver cell can be utilized by the customer to implement their own USB host or device DPR memories are completely for customer use. BIST is provided Resets (4) 450K Gates 90 MPIO I/OS Chip Boundary Scan MP I/Os type may be customized MPIOs (90) MPBlock scan chain wrapper for Chip and MPBlock scan test Confidential 14 CAP7 Design Flow System Prototyping Integration Place & Route (Metal Layers) 10~12 WEEKS Prototype Fabrication Production Volume Confidential 15 CAP7 Emulation Strategy Emulate your future device in a few weeks Custom IP Blocks Model your custom IP Test your software on target hardware CAP9 Or CAP7 FPGA Emulation Platform Confidential 16 CAP Emulation Board One motherboard supporting either CAP7 or CAP9 daughtercards (Altera-based and Xilinx-based versions to be available for either CAP device) Design to support LCD, audio, PIO, communications interface, etc. Design to facilitate OS support Supports different EBI memory types Low cost solution Confidential 17 CAP7 Emulation Daughter Card CAP7 Device customized for emulation ARM Mode - low speed Platform Mode – 80Mhz Xilinx Virtex 4 LX80 FPGA For MP Logic development 512Mbyte SRAM For ROM development EBI Memory Sockets For SDRAM/NAND/C-Flash development 3.3V Battery Backup 4MB DataFlash For NV program and data storage Confidential 18 CAP7 Emulation Design Flow Summary Func Sims * PostLayout Sims * 01001110 01110010 10101111 00101011 11000... H/W Flow Verilog/VHDL MP Logic RTL Bitstream .mpm .edf Synthesis Netlist P&R EBI Interface Dau ghtercard Con nector JT AG ICE He ad er EBI Interface Dau ghtercard Con nector Header JT AG He ade r Xilinx Virtex 4 LX60 Header Push Butto ns Swi tch LED's Produ ct # C/C++ Source .Hex Header S/W Flow Xi l in x Pl atform Fla sh Header SRAM CAP7L em u la ti o n pe rsona li ty Rev. A ICE Compile/Link/Debug Download/ICE * Simulators Supported NC Verilog/ Modelsim Confidential 19 USB UART 0 UART 1 Ethe rn et MP Logic Block Development Designers code their MP Logic module in HDL and synthesize1 to an .edf FPGA gate-level netlist FPGA compiler tools1 are used to combine the user’s MP logic block netlist with the CAP7 platform netlist Atmel provided macro files handle merging of both netlists, P&R, and generation of the FPGA bitstream A vendor-supplied JTAG-ISP tool is used to program the FPGA configuration PROM with the bitstream 1Xilinx ISE tools include XST for synthesis Altera Quartus support Nov-07 Confidential 20 FPGA RTL Functional Simulation Supported with Cadence NC Verilog or Mentor Modelsim Atmel Provides: ARM7TDMI Solaris/Linux compatible model Encrypted Verilog model of CAP7 platform logic Scripts to support simulation environment (e.g. makefiles, Perl, etc.) Verilog testbench Confidential 21 FPGA Post-Layout Simulations Supported with Cadence NC Verilog or Mentor Modelsim Atmel Provides: ARM7TDMI Solaris/Linux compatible model FPGA netlist for CAP7 Platform Logic Scripts to support simulation environment (e.g. makefiles, Perl, etc.) Verilog testbench (same as for RTL simulations) Confidential 22 S/W Tool Chain Environment Vendors : ARM ADS GNU GCC + Eclipse IAR Embedded Workbench Green Hills Multi IDE Keil RealView MDK Rowley CrossWorks + Confidential 23