Fabrication Process Technology

Gong Xiao

Email: elegong@nus.edu.sg

Office: E4-05-31

Main Content:

Thin Film Deposition and Growth

Dopant Introduction – Diffusion & Ion Implantation

Pattern Transfer – Lithography

Pattern Transfer – Plasma Etching

Back-End Technology

CMOS Process Flow Integration

A Look Inside Apple’s iPhone:

A Modern Electronic System with Multiple

IC Chips

Si-based chips

Source:

www.ifixit.com

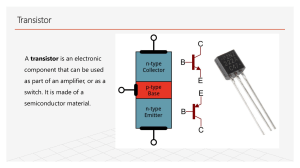

Transistor

Faster Device Operation

Lower Power Consumption

Higher Device Density

III-V-based Devices

History of Transistor Scaling

Number of transistors in CPU

~$2800

4

First transistor

in 1950’

10

2016: Intel 14 nm Xeon E5 -2600

16-24 CPU cores (456 mm2)

7.2 Billion Transistors!

Cost/transistor = 2-5μ cents

~$1000

2

10

1971: Intel 4004 (12 mm2)

2300 Transistors

Cost/transistor = 50 cents

50 billion

Transistors?

0

10

60'

65'

70'

75'

80'

2016

2022

Moore’s Law: the number of transistors on a microchip doubles about

every two years, though the cost of computers is halved.

Recent Transistor Scaling

Year 2005

Tech node 65 nm

2009

2011

32 nm

22 nm 14 nm 10 nm Sub-5 nm, beyond Si CMOS

2013

2017

2019 and Beyond

Nanosheet

Nanowire

III-V

Ge

TFET

Strained Si

High-k

Metal Gate

FinFET

MoS2

Strained Silicon

High-k/Metal Gate

FinFET

GeSn

BP

Overview of Integrated Circuits

• Currently more than hundreds of device structures

exist, Si CMOS is the dominant technology!

• For example: Microprocessor (many levels of

Interconnects and high density of very small

transistors)

Intel’s 22 nm Tri-gate

Fabrication Process

There are two major stages in the

production process of semiconductor.

One is called front-end of the line

process where the transistors are

formed on the silicon substrate

(wafer), and the other is called backend of the line process where devices

are connected by layers of metal lines.

EE4436 Course Outline

1. Thin Film Deposition and Growth

2. Dopant Introduction

3. Lithography

4. Plasma Etching

5. Interconnects

6. CMOS Integration

What to Learn

Thin Film Deposition

and Growth

Dopant Introduction

–Diffusion & Ion Implantation

Pattern Transfer

–Lithography

Pattern Transfer

–Plasma Etching

Transistor

Back-End

Technology

CMOS Process

Flow

Integration

Assessment:

40% CA + 60% (Final Exam)

Simulation Project (20%)

Literature Review Report (20%)

Assignment 1

Assignment 2

0

0