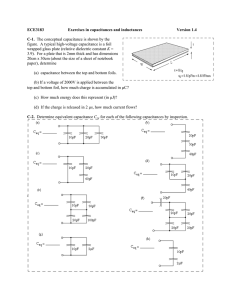

196 IEEE ELECTRON DEVICE LETTERS, VOL. EDL-2, NO. 8, AUGUST 1981 oupling Capacitancesfor imensional Wires R. L. M. DANG AND N. SHIGYO other sides as magnetic walls where the normal component of the potential gradient is zero. This reflective boundary implies theexistence ofsimilar half-conductorsatsymmetrical distances with respect to the right side and the upper wall. Therefore, the size of the calculation region must be large enough to minimize theinfluence of suchhalf-conductor ‘‘images” on HE delay time of an MOS gate is essentially determined the calculated result. In the present study we found that when by the transfer conductance and the gate capacitance of each side of the calculation region is larger than a few times H the MOS transistor and various parasitic capacitances, includthe error due to the half-conductor “images” can generally be ing that of the interconnect. As LSI devices are scaled down, neglected. Note that the mesh size forthefinite-difference the width and the length of the interconnect are reduced acequations is kept constant and small enough so that H should cording to the scaling factor. But the thickness of the interbe always at least 10 meshes larger. On the other hand, for connect and that of the field insulator are usually not scaled the case of a plurality of periodically arrangedparallelcondown in the Same proportion. At first sight it looks as if only ductors, the calculation region is taken, also by virtue of symthe non-scaled-down line thickness would constitute a serious metry, as a half of Fig. 2 which is an example of the potential problem because it increases thetwo-dimensional fringeefdistribution obtained by the present method. fect; but the thick field insulator helps reduce the total line Figure 1 shows acomparison between.our calculatedrecapacitance.This is true if the line-and-spaceremainssuffisults and those based on the conventional formula for a paralcientlylargecomparedwiththe line thickness. But because lel plate condenser aswellas thosebased ona closed form the vertical dimensions are not scaled down in the same protwo-dimensional formula [4]. As seen, the conventional portion as the horizontal ones, there is a considerable increase formula for a parallel plate condenser applies only to very of thecouplingcapacitance whereneighboring lines exist. wide conductors and proves to include an error as large as a Inthepresentletter, to gain insight intotheproblem of few hundred percent when the value of W is less than H . On two-dimensionalcapacitanceeffectswithoutgoing intothe closed form two-dimensional problem-solving technique [ 1, 21 , we make use of the method the other hand, the approximated based on the solution of the Laplace equation [3] to obtain formula just mentioned [4], while being reasonably good for the whole range of W,seems to have a rather weak dependence the capacitances as described below. are in close The capacitances associated with a system of y1 conductors on the conductor thickness. Note that our results agreement with previous calculations based on the Green funcare given as follows: tion formulation [ 5 ] for the two-dimensional case (W/L= 0). Qi=Ci,(Vi-Vl)tCi,(Vi-V,)t . . . t C i i V i t . . . tCin(Vi-Vn) Figure 3 shows the calculated capacitances for the case of where Qi, Vi, Cii denotesthecharge,thepotentialandthe the periodic arrangement shown in the inset of the same figcapacitance of the ith conductor, respectively;Cij is the capac- ure.Thisperiodicarrangement is intended to simulate the itance between the ith and the jth conductors. The problem of situation when a plurality of parallel wiresaredesignedand capacitance is thus reduced to that of calculating Qi’s when fabricatedaccordingtoapredeterminedline-and-spacerule. Vi’s are known. This is done as follows: the two-dimensional From this figure, it is found that the “grounding” capacitance Laplace equation is numericallysolvedforthepotential dis- Cll between eachline and ground decreases but the “coupling” tribution; and the normal componentof the potential gradient 2 is then integrated around the conductors for Qj’s using the CAPACITANCE OF PARALLEL PLATES . Gauss theorem. To economize computer time and memory, the boundaries of the two-dimensional region where the Laplace equation is 6 solved(calculationregion),aredefined as follows.Forthe ... case of a single line above an infinite ground plane, the calculaV tion region is taken as half of the inset of Fig. 1 , by virtue of symmetry, with thebase side taken as an equipotential and the Abstract-This letter reports some interesting results on the twodimensional effectsof the capacitances of LSI metallic interconnect wires, based on a numerical analysis of the Laplace’s equation. Our findings show that there exists an optimum condition for the relation between line-and-spaceand coupling capacitances. \ Manuscript received March 3, 1981; revised May 29, 1981. The authors are with IC Laboratory, TOSHIBA Research and Development Center, TOSHIBA Corporation, 7 2 Horikawa-cho,Saiwai-ku, Kawasaki-shi, 210 Japan. 0193-8576/81/0800-196$00.75 01981 IEEE 0 Fig. 1 DANG AND SHHGYO: COUPLING CAPACITANCES FOR TWO-DIMENSIONAL WIRES 8 I radian) Fig. 4 . -40.5w Fig. 2. IO CAPACITANCE OF PARALLEL PLATES capacitance C12 increases sharply with decreasing line-andspace. As a result?thetotal capacitance C1 always showsa minimum. It can be seen from Fig. 3 that decreasing the line thickness and/or increasing the line spacing reduces the total line capacitanceandatthe same timeshiftstheminimum point to a smaller line width. In actual design, however, decreasing the line thickness will result in a higher line resistance while increasing line spacing will lower the packing density. Therefore,it is thoughtthatthemost desirable design rule would be a 1:1 relation between the line width and thespacing. Figure 4 shows.the periodicarrangement case when the conductors are trapezoidalincross-section. By varying the angle 0 shown in the inset of Fig. 4, it is possible to simulate various design andfabricationconditions whereby the interconnects are formed. It is interesting to observe thatthe groundingcapacitance e,, is virtually unchanged while the coupling capacitance CI2 andthusthetotalcapacitance C1 both show a minimum when theconductor cross-section is rectangular. Notethatthe 1: 1 line-and-space relation is assumed hereinaccordancewiththe observation made above andthe angle 0 is varied as showntokeepthe linecrosssectionalarea constant.This,at first approximation,would assure a constant resistance per unit length of the wire so that any change in terms of the wire capacitance can be considered to have a direct consequence on the time delay of the wire itself. The results shown in Figs. 3 and 4 imply that as the lineand-space is decreased, the number of field lines increases to account for the increased charges on the conductors, but these additional fieldlinesare terminatedatthe neighboring conductors and not at the groundplane. Therefore, they only contributeto increasing the couplingcapacitance andnotthe grounding one. This constitutesa serious problemfor LSI devices as they are scaled down because the increased total capacitance C1 means a deteriorationinspeed,andtheincreasedcouplingcapacitance e,, means anincreased interTerence between neighboring interconnect lines [ 4 ] . In this sense, theoptimumconditionshowninboth Figs. 3 and 4 can serve as a guideline for designing such optimized interconnect capacitances. An extensive experimental study is in progress to check the validity of the above calculated results and an excellent agreement has been obtained between a part of them and measurements [7]. ACKNOWLEDGMENT The authors wish to thank Dr. H. Iizukaand T. Shibata for discussions and Dr. K. Shimizu for permission to publish these findings. REFERENCES [I] [2] [3] [4] 151 [6] [7] A. E. Ruehli, IBM J.Res.Develop., vol. 23, no. 6 , p . 626, Nov. 1979. A. E.Ruehliand P. A. Brennan, IEEEJSolid-State Circuits, vol. SC-10, no. 6,p. 530, Dec. 1975. J. W. Duncan, Trans. on Microwave Theory aad Technique, vol. MTT-15, no. 1 0 , p . 575, Oct. 1967. W. H. Chang, IEEE Trans. on Microwave Theory and Technique, vol. "IT-24, no. 9, p. 608, Sept. 1976 andvol. MTT-25, no. 8, p. 712, Aug. 1971. A. E.Ruehliand P. A. Brennan, IEEEJ.§olid-stQteCircuits, vol. 92-8, no. 8, p. 289, Aug. 1973. J. G. Poksheva, D. N. Pattanayak,and J. H. Nelson, Device the IEEE Electron DeResearch Conference (sponsoredby vices Society), p. VA-7, June 23-25, 1980. T. Shibata et al., Proceedings oftheElectrochemicalSociety Meeling, Minneapolis, Minnesota, May 1981.