- No category

IC Compiler to IC Compiler II Design Migration Guide

advertisement

Migrating a Design From

IC Compiler to IC Compiler II

Agenda

•

Overview

•

Design Data Migration

•

Sanity and Consistency Checkers

© 2016 Synopsys, Inc.

2

Overview

• The IC Compiler tool is enhanced to help you migrate design data to

the IC Compiler II format

• Several commands can output files in an IC Compiler II consumable

format for easy migration and setup

• After you migrated the design, there are two design setup checking

utilities:

– The consistency checker to ensure tool settings are consistent

– The sanity checker to sanity check the design data

© 2016 Synopsys, Inc.

3

Design Data Migration

•

Design Constraints Migration

•

Design Netlist

•

Floorplan Constraints

•

Design Constraints

•

Clock Tree Constraints

•

Scenario Constraints

•

Routing Constraints

•

Script Flow Example

© 2016 Synopsys, Inc.

4

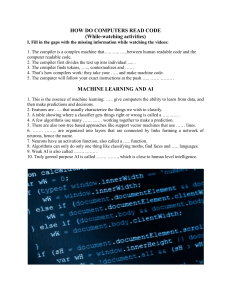

Design Constraints Migration

IC Compiler to IC Compiler II

IC Compiler II Design Setup

IC Compiler

Verilog

write_verilog

write_floorplan

write_script

write_def

write_timing_context

write_rp_groups

report_net_routing_

layer_constraints

save_upf

Floorplan

write_script

output

Layer

constraints

Timing

constraints

UPF

read_verilog

Source floorplan Tcl file

Source write_script command output Tcl file

Source relative placement group Tcl file

Source layer constraint file

Load timing constraints

read_def

load_upf

Apply user define routing constraint if any

set_ignored_layers

set_routing_rule

set_attribute on physical_status

add_via_mapping

DEF

Generate IC Compiler II compliant Tcl scripts for easy transition from

IC Compiler to IC Compiler II

Design Netlist

write_verilog

• Writing out the netlist from IC Compiler for IC Compiler II is the same

as writing out for other tools

– Prepare the netlist names to be Verilog compliant before writing out

• Use the change_names command to prepare the netlist to be Verilog

compliant

icc_shell> change_names –rules verilog –hierarchy

icc_shell> write_verilog –pg from_icc1.v

© 2016 Synopsys, Inc.

6

Floorplan Constraints

write_floorplan

• The write_floorplan command has a –format icc2 option to

make the floorplan file consumable by IC Compiler II

• The content and coverage of the write_floorplan command is no

different than it normally is for IC Compiler

– The only difference is that the Tcl commands are written out using the IC

Compiler II Tcl command names

icc_shell> write_floorplan –format icc2 \

–output from_icc1_fp.tcl

© 2016 Synopsys, Inc.

7

Design Constraints

write_script

• The write_script command has a –format icc2 option to output

the constraints file in a IC Compiler II consumable format

– The content and coverage of the write_script command is the same,

but the commands match the names and format for IC Compiler II

• The following constraints are not covered by the write_script

command:

– set_max_transition

– set_max_capacitance

– set_max_fanout

– set_max_area

– set_max_net_length

icc_shell> write_script –format icc2 \

–output from_icc1_cstr.tcl

© 2016 Synopsys, Inc.

8

Clock Tree Synthesis Constraints

write_script

• One new feature of using the write_script –format icc2

command is that clock tree synthesis (CTS) options are written out

into a new file

– A second file is written out with CTS and timing constraints in a single file

named ${output_name}_cts_setup.tcl

• The following table has the CTS constraints that are covered

Covered CTS Constraints

CTS scenario settings

Target latency

Clock tree references

Clock routing rules

Maximum transition, capacitance and

fanout

Fixed detail routes

Latency adjustment options

Clock tree exceptions

Inter clock delay options

Exceptions on pins, nets, cells

Target skew

Clock cell spacing

© 2016 Synopsys, Inc.

9

Scenario Constraints

write_timing_context

• In IC Compiler a scenario includes mode, corner, and scenario

specific constraints

– The write_timing_context command writes out a Tcl scripts that can be

sourced in IC Compiler II to rebuild the scenarios

• The write_timing_context command generates:

– A directory and scripts that contain the write_script command output

for each scenario

– A wrapper script named top.tcl re-create all the modes, corners, and

scenarios

– Duplicates the IC Compiler scenario options in IC Compiler II

icc_shell> write_timing_context –format icc2 \

–output from_icc1_tim_context

icc2_shell> source from_icc1_tim_context/top.tcl

© 2016 Synopsys, Inc. 10

Design Constraint Setting for Timing

IC Compiler

Scenario options

(setup/hold/power)

Scenario

constraints

(mode/corner etc.)

Manual conversion

• Categorize SDC into

mode/corner/scenario

• Identify common corner/mode

to leverage IC Compiler II

MCMM capacity advantages

IC Compiler II

Scenario options

(setup/hold/power)

Mode

Corner

scenario

IC Compiler II

write_timing_context

Scenario options

(setup/hold/power)

• Push-button solution for initial

migration and new users

• Expanded scenario settings like

IC Compiler

© 2016 Synopsys, Inc. 11

Scenario

constraints

(mode/corner etc.)

Routing Constraints

Not Covered

• The write_floorplan, write_def, and write_script commands

can cover many of the routing constraints but not all routing settings

are covered

• Settings that are not covered

– set_ignored_layers

– Router options (set_route_zrt_common_options to route.common.*

application options, etc.)

– Net routing layer constraints

• The sanity and consistency checkers can help highlight the constraint

differences not covered here

© 2016 Synopsys, Inc. 12

UPF

save_upf

• No special options are necessary for transferring the UPF file to IC

Compiler II

• The same commands can be used for writing out the UPF constraints

for either the UPF Prime or Golden UPF flow

• UPF Prime

icc_shell> save_upf from_icc1.upf

• Golden UPF

icc_shell> save_upf –supplemental from_icc1.supplemental.upf

icc_shell> save_upf –supplemental from_icc1.supplemental.pg.upf \

–include_supply_exceptions

© 2016 Synopsys, Inc. 13

Script Flow Example

Output From IC Compiler and Input Into IC Compiler II

IC Compiler

change_names –rules verilog –hierarchy

write_verilog –pg from_icc1.v

write_floorplan –format icc2 –output from_icc1_fp.tcl

write_script –format icc2 –output from_icc1_cstr.tcl

write_def –all_vias –via_style_as_generated –version 5.7|5.8 \

–output from_icc1.def

write_timing_context –format icc2 –output from_icc1_tim_context

save_upf from_icc1.upf

IC Compiler II

read_verilog –top $design_name from_icc1.v

load_upf from_icc1.upf

read_def from_icc1.def

source from_icc1_fp.tcl

source from_icc1_cstr.tcl

source from_icc1_tim_context/top.tcl

source from_icc1_cstr_cts_setup.tcl

## Apply other routing constraints

© 2016 Synopsys, Inc. 14

Script Flow Example

Output From IC Compiler And Input Into IC Compiler II (Golden UPF)

IC Compiler

change_names –rules verilog –hierarchy

write_verilog –pg from_icc1.v

write_floorplan –format icc2 –output from_icc1_fp.tcl

write_script –format icc2 –output from_icc1_cstr.tcl

write_def –all_vias –via_style_as_generated –version 5.7|5.8 \

–output from_icc1.def

write_timing_context –format icc2 –output from_icc1_tim_context

save_upf –supplemental –include_supply_exceptions \

from_icc1.supplemetal.upf

IC Compiler II

read_verilog –top $design_name from_icc1.v

load_upf golden.upf

load_upf from_icc1.supplemental.upf

read_def from_icc1.def

source from_icc1_fp.tcl

source from_icc1_cstr.tcl

source from_icc1_tim_context/top.tcl

source from_icc1_cstr_cts_setup.tcl

## Apply other routing constraints

© 2016 Synopsys, Inc. 15

After Design Migration

• Settings Consistency Checker

• Design Sanity Checker

• IC Compiler II Reference Methodology

© 2016 Synopsys, Inc. 16

Flow After Design Migration

• Perform setting consistency check

–Compare variables, application option

values and command option values of

the IC Compiler and IC Compiler II

session

• Perform design sanity check

–Compare design timing, constraints,

and physical design data of IC

Compiler and IC Compiler II

• Check IC Compiler II scripts

–Use updated RM scripts as startpoint

© 2016 Synopsys, Inc. 17

IC Compiler II

Placed design

Perform setting

consistency

check

Perform design

sanity check

Check IC Compiler

II scripts

Settings Consistency Checker

© 2016 Synopsys, Inc. 18

Settings Consistency Checker

• The consistency checker allows for automated comparisons of settings

between the IC Compiler and IC Compiler II tools

– Checks and compares the tool settings in key areas of data model, placement,

legalization, timer, extraction, preroute optimization, CTS, routing and

postroute optimization

• The consistency checker is a set of scripts, with the following two main

scripts

– snps_settings.tcl

– Defines a Tcl procedure named report_settings to output the tool session’s settings

– snps_consistency_checker.pl

– A Perl script to compare the output of the report_settings procedure, from both

tools, and report the differences

• SolvNet article #2112936 includes these scripts and information on how

to use them

© 2016 Synopsys, Inc. 19

Settings Consistency Checker

Scripts Flow

# Step 1 in IC Compiler: Open the top design, source snps_settings.tcl, and redirect report_settings to a file

open_mw_lib orca_lib.mw

open_mw_cel orca

source consistency_checker/snps_settings.tcl

redirect –file icc_settings.rpt {report_settings}

# Step 2 in IC Compiler II: Open the top design, source snps_settings.tcl and redirect report_settings to a file

open_lib orca_lib.nlib

open_block orca

source consistency_checker/snps_settings.tcl

redirect –file icc2_settings.rpt {report_setttings}

# Step 3 in UNIX: Pass report_settings outputs from both tools to the snps_consistency_checker.pl

consistency_checker/snps_consistency_checker.pl \

icc_settings.rpt icc2_settings.rpt > consistency.rpt

IC Compiler

icc_settings.rpt

report_settings

UNIX Terminal

IC Compiler II

report_settings

© 2016 Synopsys, Inc. 20

consistency_checker/snps_consistency_checker.pl

icc2_settings.rpt

Design Sanity Checker

© 2016 Synopsys, Inc. 21

Design Sanity Checker

write_sanity_check_point

Checkpoint contents

Setup and hold WNS/TNS/NVP (ZIC)

• Checks design timing, constraints, and

physical design data consistency between IC

Compiler and IC Compiler II

Maximum transition/capacitance

Macro/black box area and cell area

Number of buffers and inverters

Number of ideal nets

• Ensures IC Compiler II design has the same

or similar physical information and constraints

Number of dont_touch cells (+ user-set)

Number of size_only cells (+ user-set)

Number of fixed cells

• Three easy steps to report differences

IC Compiler:

write_sanity_check_point

IC Compiler II: write_sanity_check_point

unix% tkdiff icc_sanity_check.rpt \

icc2_sanity_check.rpt

Ignored layers

Group_path list and weight

Timing paths

Placement blockages (placed cell)

Number of bounds (placed cell)

Number of physical only cells (placed

cell)

Standard cell utilization (placed cell)

Number of voltage areas

© 2016 Synopsys, Inc. 22

Design Sanity Checkers

write_sanity_check_point

• The write_sanity_check_point command outputs a file that is a

simple text file of the design’s checkpoint criteria

– Use a UNIX utility, such as tkdiff, to compare the output file from both

tools

– The criteria should be close or the same between the two tools

© 2016 Synopsys, Inc. 23

Design Sanity Checkers

write_sanity_check_point

• The write_sanity_check_point command has two stages

‐stage setup and –stage placement

• The –stage setup reports all of the checkpoint criteria for the

design, including the zero interconnect timing for the design

• The –stage placement reports all of the same criteria but also runs

the create_placement command under-the-hood to get the wire

length number for comparison

• The –output option controls the name of the output file

– By default, the output file name for the

– Setup stage is sanity_setup_qor_log

– Placement stage it is sanity_placement_qor_log

© 2016 Synopsys, Inc. 24

Design Sanity Checker

write_sanity_check_point example

# Step 1 in IC Compiler: Open the top design and execute the write_sanity_check_point command

open_mw_lib orca_lib.mw

open_mw_cel orca

write_sanity_check_point –stage setup –output icc_sanity_check.rpt

# Step 2 in IC Compiler II: Open the top design and execute the write_sanity_check_point command

open_lib orca_lib.nlib

open_block orca

write_sanity_check_point –stage setup –output icc2_sanity_check.rpt

# Step 3 in UNIX: Use the tkdiff command and compare the output files from both tools to compare

any differences. Expect few to no differences

tkdiff icc_sanity_check.rpt icc2_sanity_check.rpt

© 2016 Synopsys, Inc. 25

Design Sanity Checker

Output File Comparison Example

IC Compiler II

IC Compiler

##SANITY_REPORT_AREA

Buf/Inv Cell Count: 255945

Buf/Inv Area: 239757.408000

Macro/Black Box Area: 506240.707200

Cell Area (netlist): 3058653.739223

##SANITY_REPORT_AREA

Buf/Inv Cell Count: 255945

Buf/Inv Area: 239757.408000

Macro/Black Box Area: 506240.707200

Cell Area (netlist): 3058653.739223

##SANITY_DONT_TOUCH_CELLS

18208

74 (user‐set dont‐touch)

##SANITY_DONT_TOUCH_CELLS

18210

74 (user‐set dont‐touch)

##SANITY_SIZE_ONLY_CELLS

205570

16226 (user‐set size‐only)

##SANITY_SIZE_ONLY_CELLS

205570

16226 (user‐set size‐only)

##SANITY_FIXED_PLACEMENT_CELLS

72

##SANITY_FIXED_PLACEMENT_CELLS

72

##SANITY_IGNORED_LAYERS

Min Routing Layer

Max Routing Layer

RC Estimation Ignored Layers

M2

M8

M1 M7 M8 M9

##SANITY_IGNORED_LAYERS

Min Routing Layer

Max Routing Layer

RC Estimation Ignored Layers

##SANITY_PATH_GROUP

Group Name

Weight

‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐

REGIN

1.00

REGOUT

2.00

##SANITY_PATH_GROUP

Group Name

Weight

‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐

REGIN

1.00

REGOUT

1.00

##SANITY_IDEAL_NETS

0

##SANITY_IDEAL_NETS

0

##SANITY_PLACEMENT_BLOCKAGE

Hard Blockage: 72

Soft Blockage: 7

Partial Blockage: 0

...

##SANITY_PLACEMENT_BLOCKAGE

Hard Blockage: 72

Soft Blockage: 7

Partial Blockage: 0

...

© 2016 Synopsys, Inc. 26

M2

M6

M1 M5 M6 M7 M8 M9

IC Compiler II Reference

Methodology

© 2016 Synopsys, Inc. 27

IC Compiler II Reference Methodology

• The IC Compiler II Reference Methodology scripts are a good starting

point for your place and route flow

– The scripts show the flow and features available in the tool

• Download the scripts from SolvNet

– https://solvnet.synopsys.com/rmgen/

© 2016 Synopsys, Inc. 28

Thank You

0

0

advertisement

Add this document to collection(s)

You can add this document to your study collection(s)

Sign in Available only to authorized usersAdd this document to saved

You can add this document to your saved list

Sign in Available only to authorized users