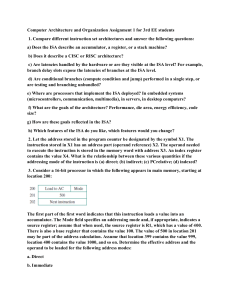

Computer Architecture and Organization Assignment 1 for 3rd EE students 1. Compare different instruction set architectures and answer the following questions: a) Does the ISA describe an accumulator, a register, or a stack machine? b) Does it describe a CISC or RISC architecture? c) Are latencies handled by the hardware or are they visible at the ISA level? For example, branch delay slots expose the latencies of branches at the ISA level. d) Are conditional branches (compute condition and jump) performed in a single step, or are testing and branching unbundled? e) Where are processors that implement the ISA deployed? In embedded systems (microcontrollers, communication, multimedia), in servers, in desktop computers? f) What are the goals of the architecture? Performance, die area, energy efficiency, code size? g) How are these goals reflected in the ISA? h) Which features of the ISA do you like, which features would you change? 2. Let the address stored in the program counter be designated by the symbol X1. The instruction stored in X1 has an address part (operand reference) X2. The operand needed to execute the instruction is stored in the memory word with address X3. An index register contains the value X4. What is the relationship between these various quantities if the addressing mode of the instruction is (a) direct; (b) indirect; (c) PCrelative; (d) indexed? 3. Consider a 16-bit processor in which the following appears in main memory, starting at location 200: The first part of the first word indicates that this instruction loads a value into an accumulator. The Mode field specifies an addressing mode and, if appropriate, indicates a source register; assume that when used, the source register is R1, which has a value of 400. There is also a base register that contains the value 100. The value of 500 in location 201 may be part of the address calculation. Assume that location 399 contains the value 999, location 400 contains the value 1000, and so on. Determine the effective address and the operand to be loaded for the following address modes: a. Direct b. Immediate c. Indirect d. PC relative e. Displacement f. Register g. Register indirect h. Autoindexing with increment, using R1 4. Consider a processor that includes a base with indexing addressing mode. Suppose an instruction is encountered that employs this addressing mode and specifies a displacement of 1970, in decimal. Currently the base and index register contain the decimal numbers 48,022 and 8, respectively. What is the address of the operand? 5. Consider a hypothetical microprocessor generating a 16-bit address (for example, assume that the program counter and the address registers are 16 bits wide) and having a 16-bit data bus. a. What is the maximum memory address space that the processor can access directly if it is connected to a “16-bit memory”? b. What is the maximum memory address space that the processor can access directly if it is connected to an “8-bit memory”? c. What architectural features will allow this microprocessor to access a separate “I/O space”? d. If an input and an output instruction can specify an 8-bit I/O port number, how many 8bit I/O ports can the microprocessor support? How many 16-bit I/O ports? Explain. 6. Consider a hypothetical computer with an instruction set of only two n-bit instructions. The first bit specifies the opcode, and the remaining bits specify one of then-bit words of main memory. The two instructions are as follows: SUBS X Subtract the contents of location X from the accumulator, and store the result in location X and the accumulator. JUMP X Place address X in the program counter. A word in main memory may contain either an instruction or a binary number in twos complement notation. Demonstrate that this instruction repertoire is reasonably complete by specifying how the following operations can be programmed: a. Data transfer: Location X to accumulator, accumulator to location X b. Addition: Add contents of location X to accumulator c. Conditional branch d. Logical OR e. I/O Operations # NB: It’s an individual assignment and I expect a work off your own. Copying the solution one another results in a cancellation of your Assignment. Submission Date: 24:10:2014 E.C