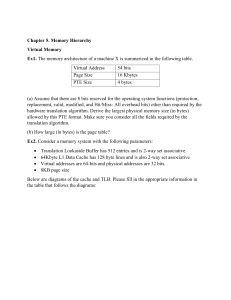

Justin Oettinger Professor Lee CS 250 6 December, 2018 HW5 Writeup 1. Write-back caches are also usually write-allocate caches because, in the case of misses, a writeallocate cache will bring the data from memory back and place it into cache so subsequent calls can be hits, thus improving efficiency. In the case of a write-non-allocate, the data would not be brought back into the cache, and would thus have to go down into main memory every time a miss was encountered, drastically harming the efficiency and demonstrating the need for writeallocate. 2. Tavg = T1hit + T1miss Tavg = 0.95(1) + 0.05(T1miss) Tavg = 0.95 + 0.05(T2hit + (0)T2miss) Since L2 has 100% hit rate, we have a zero in that factor. Tavg = 0.95 + 0.05(8) = 0.95 + 0.4 = 1.35 ns 3. a. Virtual pages = (virtual address space)/(page size) = (2^ 64) / (2^6 * 2^10) = 2^48 pages b. Physical pages = (physical address space)/(page size) = (4 * 2^ 30) / (2^6 * 2^10) = (2^2 * 2^ 30) / (2^16) = (2^32) / (2^16) = 2^16 pages c. Bits for VPN = 48 bits Bits for PPN = 16 bits d. 16 bits / (8 bits / byte) = 2 bytes e. 64 KB = 64000 bytes / 2bytes = 32000 PTEs f. 48 bits / (8 bits / byte) = 6 bytes 64000 B / 6 B ~ 10, 666 pointers per page g. 2^48 * 2 = 2^49 bytes h. Virtual page offset is 16 Physical page offset is 4 i. A TLB miss does not always lead to a page fault, since TLB’s are managed through either hardware, software, or both, which pushes the CPU to parse the page tables for an entry and performing the translation in the case of a TLB miss, leading to the mitigation of page faults and preventing some from occurring.