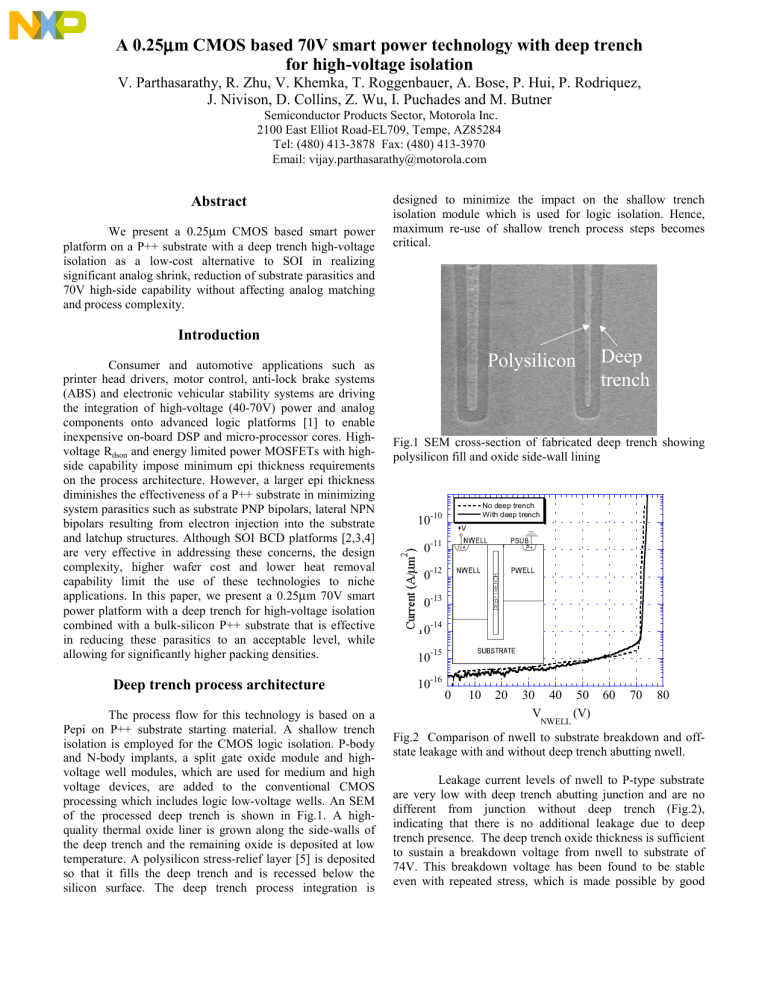

A 0.25µ µ m CMOS based 70V smart power technology with deep trench for high-voltage isolation V. Parthasarathy, R. Zhu, V. Khemka, T. Roggenbauer, A. Bose, P. Hui, P. Rodriquez, J. Nivison, D. Collins, Z. Wu, I. Puchades and M. Butner Semiconductor Products Sector, Motorola Inc. 2100 East Elliot Road-EL709, Tempe, AZ85284 Tel: (480) 413-3878 Fax: (480) 413-3970 Email: vijay.parthasarathy@motorola.com Abstract We present a 0.25µm CMOS based smart power platform on a P++ substrate with a deep trench high-voltage isolation as a low-cost alternative to SOI in realizing significant analog shrink, reduction of substrate parasitics and 70V high-side capability without affecting analog matching and process complexity. designed to minimize the impact on the shallow trench isolation module which is used for logic isolation. Hence, maximum re-use of shallow trench process steps becomes critical. Introduction Consumer and automotive applications such as printer head drivers, motor control, anti-lock brake systems (ABS) and electronic vehicular stability systems are driving the integration of high-voltage (40-70V) power and analog components onto advanced logic platforms [1] to enable inexpensive on-board DSP and micro-processor cores. Highvoltage Rdson and energy limited power MOSFETs with highside capability impose minimum epi thickness requirements on the process architecture. However, a larger epi thickness diminishes the effectiveness of a P++ substrate in minimizing system parasitics such as substrate PNP bipolars, lateral NPN bipolars resulting from electron injection into the substrate and latchup structures. Although SOI BCD platforms [2,3,4] are very effective in addressing these concerns, the design complexity, higher wafer cost and lower heat removal capability limit the use of these technologies to niche applications. In this paper, we present a 0.25µm 70V smart power platform with a deep trench for high-voltage isolation combined with a bulk-silicon P++ substrate that is effective in reducing these parasitics to an acceptable level, while allowing for significantly higher packing densities. Deep trench process architecture The process flow for this technology is based on a Pepi on P++ substrate starting material. A shallow trench isolation is employed for the CMOS logic isolation. P-body and N-body implants, a split gate oxide module and highvoltage well modules, which are used for medium and high voltage devices, are added to the conventional CMOS processing which includes logic low-voltage wells. An SEM of the processed deep trench is shown in Fig.1. A highquality thermal oxide liner is grown along the side-walls of the deep trench and the remaining oxide is deposited at low temperature. A polysilicon stress-relief layer [5] is deposited so that it fills the deep trench and is recessed below the silicon surface. The deep trench process integration is Polysilicon Deep trench Fig.1 SEM cross-section of fabricated deep trench showing polysilicon fill and oxide side-wall lining No deep trench With deep trench -10 10 -11 10 10-12 10-13 10-14 -15 10 -16 10 0 10 20 30 40 50 60 V (V) 70 80 NWELL Fig.2 Comparison of nwell to substrate breakdown and offstate leakage with and without deep trench abutting nwell. Leakage current levels of nwell to P-type substrate are very low with deep trench abutting junction and are no different from junction without deep trench (Fig.2), indicating that there is no additional leakage due to deep trench presence. The deep trench oxide thickness is sufficient to sustain a breakdown voltage from nwell to substrate of 74V. This breakdown voltage has been found to be stable even with repeated stress, which is made possible by good interface between the deep trench silicon sidewall and the high quality thermal oxide liner. The deep trench in this technology is used to significantly increase the analog packing density by bringing devices adjacent to each other across the deep trench, thereby enabling shrinks ranging from 50% for medium-voltage analog to >80% for high-voltage analog components compared to the 0.35µm SMOS7 technology [6]. In SMOS7, high-energy implant chains replaced the deep diffused implants, which were present in older diffusion based technologies [7]. Any further shrink in analog component size from here onwards becomes difficult to accomplish due to voltage requirements and significant reductions may become possible only with the deep trench isolation. However, when two nwell regions are placed adjacent with a deep trench separation, punchthrough under the deep trench becomes a concern. This can be avoided in P- substrates with punchthrough retardation implants [8] or simply by increasing the depth of the trench significantly. In our case, the problem is eliminated by optimized epi thickness and trench depth in conjunction with the P++ substrate, which acts as a very effective punch-through barrier. This is evident in Fig.3, where breakdown between an nwell1 and substrate is reached before punchthrough to an adjacent nwell2. In smart power applications, the harsh operating conditions of the power MOSFETs in the IC create ample situations for chip-level parasitics to impact circuit operation. Certain circuit topologies [10,11] cause transient electron injection from a negatively biased drain of a high-voltage high-side capable power MOSFET. While high-side requirements drive the need for thick epitaxial regions to prevent punch-through from source to substrate, this diminishes the effectiveness of the P++ substrate in lifetime killing of electrons. Here, the presence of a deep trench confines the injected to the P++ substrate where they recombine in a very short distance. Through appropriate design, the substrate injection collection ratio (Ic/Ie) can be reduced by more than 6 orders of magnitude from ~2X10-3 (no trench) to ~1.5X10-9 (with trench), as seen in Fig.4. 10-1 -3 10 -5 10 Ie (A) Ic: No deep trench 10-7 Ic: With deep trench 10-9 Inwell1 Inwell2 10-7 10 -8 10 -9 10-11 10-13 -10 10 0 -0.5 -1 -1.5 Ve (V) Fig.4 Comparison of collector current collection in parasitic substrate NPN transistor with and without deep trench 10-11 10-12 10-13 10 -14 0 10 10-15 Emitter to Collector Space=110µm P- sub 0 10 20 30 V 40 50 (V) 60 70 NWELL1 Fig.3 Off-state leakage currents of adjacent nwell regions across deep trench showing absence of punch-through 10 -2 10µm P-/P++ (No DT) 5µm P-/P++ (No DT) [1] 10-4 10-6 Parasitics suppression with deep trench Deep trench based processes have been integrated previously in CMOS architectures to suppress inter-well parasitics and CMOS thyristor latchup [9]. In mixed-signal signal applications, an immediate benefit of the deep trench is to reduce capacitances to substrate. In the present case, measured capacitance of a 500µm2 nwell to substrate junction is reduced from ~1.38X10-13 F to ~3.2X10-14 F, a reduction of 4X by the presence of a deep trench surrounding the nwell. 0.25µm SMOS P-/P++ Nominal DT 10-8 10-10 0 50 100 150 200 Collector Distance (µm) Fig.5 Substrate injection suppression ratio (Ic/Ie) as a function of distance to collector for different substrate types with and without deep trench Fig.5 shows the effectiveness of the deep trench in conjunction with the P++ substrate in suppressing minority carrier injection. For example if a few amps of injected current need to be reduced to few µAs of current, a 60µm region would suffice with the nominal deep trench. The impact of the deep trench on substrate injection suppression is more dramatic as the trench depth is increased. By comparison, even 5µm of P-epi on P++ substrate would require large moat areas around the power devices for such conditions. While a reduction in moat size can be accomplished by various passive and active guard ring schemes [11], these schemes consume area and can cause potentially unforeseen problems such as latchup or reduction in effectiveness due to nearby ground ties. With 5µm P-epi on P++ substrate, high-side capability is very difficult to realize. In the present technology, the deep trench enables the very low substrate injection ratios of 2X10-6 to be attained in distances of 50µm with high-side capability of 74V (Fig.6). Technology Platform SMOS5 [7] SMOS7 [6] BCD6 [1] 0.25µm SMOS Substrate Type P- substrate (thick epi) P- substrate (thin epi) 5µm P-/P++ (no DT) P-/P++ with Deep Tr. Typ. Ic/Ie ratio High-side at 50µm (log) Voltage (typ) -1.5 >100V -1.5 72V -2.5 50V -5.7 74V Maximum BVdss (typ) 85V 54V 48V 55V Fig.6 Comparison of different technology platforms for highside capability, maximum BVdss and substrate injection ratio 20 no deep trench with deep trench 15 analog nodes and may also have potential benefits for ESD protection. Device Performance Mismatch measurements of a self-aligned low-voltage thingate NMOS matched pair is shown in Fig.8. As expected, the drain current mismatch percentage is roughly related to the area of the device. Also, the drain current mismatch percentage is increased almost 2X in saturation bias compared to linear bias. This points to the Vth mismatch being the dominant factor due to the square dependence of drain current on threshold voltage in the saturation regime. The presence of deep trench in the vicinity of the matched pair results in negligible impact on drain current mismatch, indicating that trench stress has been minimized in this process. However, a matched pair with the deep trench surrounding only one device showed discernable systematic mismatch which suggests that care must be exercised in layouts of matched pairs. Linear bias (Vg=2.5V, Vd=0.1V) Saturation bias (Vg=2.5V, Vd=2.5V) Systematic mismatch Random mismatch Systematic mismatch Random mismatch η (∆Ιd/Id) σ (∆Ιd/Id) η (∆Ιd/Id) σ (∆Ιd/Id) Pair type and size No deep trench Wg=4.2µ, Lg=2.1µ 0.10% 0.31% 0.17% 0.57% With deep trench Wg=4.2µ, Lg=2.1µ 0.20% 0.40% 0.16% 0.66% No deep trench Wg=8.4µ, Lg=4.2µ 0.02% 0.15% 0.05% 0.27% With deep trench Wg=8.4µ, Lg=4.2µ 0.08% 0.12% 0.12% 0.24% Fig.8 Comparison of drain current mismatch data with and without deep trench in vicinity of the matched pair of a selfaligned low-voltage thin gate oxide NMOS 100 10 15 40 45 10 10 80 0.25 um SMARTMOS SMARTMOS7 TI LBC6 STM BCD6 20 2 5 -0.4 -0.5 -0.6 -0.7 -0.8 -0.9 -1 -1.1 -1.2 Vbe (V) 30 30 35 20 25 45 50 25 20 1 05 15 0 15 35 40 55 30 40 45 50 55 40 P-Body 5 10 0 Nwell 50 5 60 40 P45 20 0 10 20 30 40 50 60 BV (V) 70 80 dss Fig.7 Comparison of parasitic substrate PNP beta with and without deep trench isolation Fig.9 NLDMOS performance: (a) Off-state equipotential lines and (b) BVdss vs. Rdson tradeoff By surrounding an nwell isolation with a deep trench in all directions, the parasitic PNP between an isolated pwell and substrate is also significantly suppressed (Fig.7). Suppression of this parasitic PNP is particularly important when the anti-parallel diode of the LDMOS is used in the Hbridge high-side configuration [1]. In addition to these power LDMOS related situations, the deep trench is also useful in reducing system level latchup and parasitics at sensitive The NLDMOS device in this process is high-side capable with BVdss of 54V, which is obtained by a double RESURF action of a P- below an N- drift region [12]. The NLDMOS Rdson of 40mΩ-mm2 is 20% lower than in the 0.35µm SMOS7 process [13]. This improvement has been made possible by further optimizing RESURF of the N-drift from the P-body side (Fig.9(a)). The high-side capable RdsonBVdss trade-off in this process (Fig.9(b)) is the best reported to date for the voltage range under consideration. Due to the optimum RESURF action, the nwell drift region dose has been increased so that it can serve as the well for medium voltage PMOS devices as well as the base an isolated vertical PNPV. The resulting PNPV has a beta of 30, Vaf of 60V and BVceo and BVcbo of 22V and 48V respectively (Fig.10). Rdson (mΩ-mm2) Vth (V) 6.8 0.8 12 0.8 20 1.4 33 1.4 40 1.4 58 1.4 Device BVdss (V) NMV1 11.5 NMV2 18 NHV1 23 NHV2 42 NHV3 54 NHV4 75 Device BVdss (V) PMV1 -10 PMV2 -19 PHV1 -41.5 PHV2 -54 PHV3 -78 Rdson (mΩ-mm2) Vth (V) 25 -1 40 -1.2 95 -1.5 122 -1.5 185 -1.5 Conclusion Device Bvceo (V) Bvcbo (V) Beta Vaf (V) ft (MHz) NPNV 22 61 110 100 350 PNPV 22 48 30 60 500 PNPL 28 30 80 >300 Fig.10 Performance summary of NMOS, PMOS and bipolar device set in the 0.25µm smart power technology with highvoltage deep trench isolation The p-drift region in the PLDMOS devices is also optimized through appropriate RESURF action from the Nbody and an n-type region underneath the pwell. In this way, a maximum BVdss of 78V is obtained. The pwell drift region is employed as the well for medium voltage (5-10V) NMOS and for the base of an NPN with a beta of 110, Vaf of 100V and BVceo and BVcbo of 22V and 61V respectively (Fig.10). 0.25µm SMOS Area SMOS7 Analog 1X 0.30X Power 1X 0.80X Logic 1X 0.50X Fig.11 Summary of shrinks in the present 0.25µm smart power technology with deep trench compared to the 0.35µm SMOS7 technology. 10600 no deep trench with deep trench 10400 10000 9800 Voltage coefficient: -2 No deep trench = 1.32X10 /V -3 9400 With deep trench = 8.8X10 /V 0 2 4 6 V well 8 (V) In conclusion, we have developed and qualified a 0.25µm CMOS based high-side capable 70V smart power process on a P++ substrate with a deep trench high-voltage isolation and logic shallow trench isolation. The NLDMOS power devices integrated into this platform have the best Rdson-BVdss reported to date for the 10-70V range. By using a deep trench combined with a P++ substrate, we have realized significant analog shrink, reduction of substrate parasitics and 74V highside capability without affecting analog matching and process complexity. References [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] 10200 9600 A summary of device shrinks obtained in the present 0.25 µm SMOS technology is shown in Fig.11. Finer lithography results in a 50% logic shrink while isolating the analog components with deep trench allows for an average 70% analog shrink. In addition to reduction of analog device size, this produces additional performance benefits such as improvement in the voltage coefficient of an isolated nwell resistor (Fig.12). The substantially lower shrink of 20% in power device area is bringing the power device performance very close to the ideal 1-D silicon limit for lateral power devices. 10 12 14 Fig.12 Comparison of voltage dependence of resistance of an isolated nwell resistor with and without deep trench surrounding the resistor. A. Moscatelli et. al., pp.323-326, ISPSD, 2000. A. Ludikhuize et. al., pp.77-80, ISPSD, 2002. T. Letavic et. al., pp.73-76, ISPSD, 2002. S. Merchant et. al., pp.185-188, ISPSD, 2002. W. Yindeepol et. al., pp.151-152, IEEE Int. SOI Conf., 1998. V. Parthasarathy et. al., pp.317-320, ISPSD, 2000. S. Merchant et. al., pp.225-228, ISPSD, 1999. J. H. Klootwijk et. al., pp.200-204, ICMTS, 2000. H. Inokawa et. al., pp.218-219, Symp. On VLSI Technology, 1996. R. Zhu et. al., pp.184-186, BCTM, 1998. J. P. Laine et. al., pp.273-276, ISPSD, 2002. V. Parthasarathy et. al., pp.75-78, IEDM, 2000. R. Zhu et. al., pp.403-406, ISPSD, 2001.