UNIT - 2

Principles of Logic Circuits I

2.0

Objective

2.2

Logic Gates

2.1

2.3

2.4

2.5

2.6

Lesson Structure

Introduction

Logic Circuits

Combinational Circuits

2.4.1 Canonical and Standard Forms

2.4.2 Minimization of Gates

Design of Combinational Circuits

Examples of Logic Combinational Circuits

2.6.1 Adders

2.6.2 Decoders

2.6.3 Multiplexer

2.6.4 Encoder

2.6.5 Programmable Logic Array

2.6.6 Read Only Memory ROM

2.7

Summary

2.9

Suggested Readings

2.8

Questions

Principles of Logic Circuits

2.0 Objective

After

going through this unit we will be able to :

Define logic gates;

Describe the significance of Boolean algebra in digital circuit design;

Describe the Karnaugh map and necessity of minimizing the number of gates

in design;

Describe how basic mathematical operations like addition and subtraction, are

performed by computer; and

Define and describe some of the useful circuits of a computer system such as

Adders, multiplexers, ROM etc.

2.1 Introduction

In the previous unit we have discussed the basic configuration of computer

system, von Neumann architecture, data representations and simple instruction

execution paradigm. In this unit, we will be exposed to some of the basic

components that form the most essential parts of a computer such as logic gates,

binary adders, logic circuits combinational circuits etc. These circuits are the

backbone of any computer system and knowing them is quite essential. The

characteristics of integrated digital circuits are also discussed in this unit.

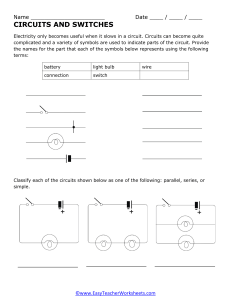

2.2 Logic Gates

A logic gates in an electronic circuit. The gates produce outputs depending on

their inputs Gates are the basic elements that produce signals of binary ‘o’ or ‘1’

representing a ‘false’ or ‘true’ or ‘low’ or ‘high’ voltage levels respectively.

In general there are three fundamental gates.

(i)

AND

(iii)

NOT

(ii)

OR

The Boolean function can be represented in the form of gates. We can

combine these gates to form some more specialized gates such as.

(i)

(ii)

AND + NOT = NAND

OR + NOT = NOR

These two gates are called universal gates because they can be used for

building all the fundamental gates (AND, OR and NOT). These gates are sometimes

called functionally complete gates. In addition to the above gate logics two more

gates are defined.

[ 30 ]

Principles of Logic Circuits

(i)

(ii)

EX OR (Exclusive – OR) = XOR

EXNOR (Exclusive – NOR) = XNOR

We can represent each gate through a distinct graphic symbol and its boolean

operation can be given by means of alzebric expression. The input and output

relation of these logic gates can be represented in tables known as truth tables. The

rotation and truth table for different logic gates are given below in figure 1 :

Name

NOT

Graphic Symbol

A

Truth Table

F

A

F

0

AND

OR

NAND

{AND +

NOT}

NOR

(OR + NOT)

EXOR

(Exclusive OR)

XNOR

(Exclusive

NOR)

A

F=A

1

1

Alzebric Function

0

F

A

0

0

1

1

B

0

1

0

1

F

0

0

0

1

F

A

A

0

0

1

1

B

0

1

0

1

F

0

1

1

1

F

A

A

0

0

1

1

B

0

1

0

1

F

1

1

1

0

F

B

0

1

0

1

F

1

0

0

0

F = A + B = A .B

A

A

0

0

1

1

F

B

0

1

0

1

F

0

1

1

0

F = AB + AB

=A+B

A

A

0

0

1

1

F

B

A

B

B

B

B

B

A

0

0

1

1

B

0

1

0

1

Figure 1 : Logic Gates

F

1

0

0

1

F = A .B = AB

F=A+B

F = A .B = A + B

F=A+ B

=A.B

EXOR (exclusive-OR) gate is a special gate which has the output one when its

inputs are not equal. XNOR is the inverse of XOR gate.

[ 31 ]

Principles of Logic Circuits

2.3 Logic Circuits

The fundamental gates AND, OR and NOT can be used to implement Boolean

function for different types of logic circuits. Let is consider for example, the Boolean

function :

F = B (A C )

B

F = B ( A + C)

A

C

Figure 2 : Logic Circuit

The relationship between this function and its binary variables A, B, C can be

represented in the truth table as shown below in figure 3 :

Input

A

0

B

C

0

1

0

0

0

1

0

1

1

1

1

0

0

1

0

1

0

1

0

0

1

1

F

0

1

0

Output

0

0

1

1

1

Figure : 3 Truth Table

1

Universal Gates : NAND and NOR logic can be used for the realization of all

the basic gates. Therefore NAND and NOR gates are known as universal gates.

NAND gate as universal gate.

NOT using NAND

AND using NAND

A

B

A

F = A. B = A

A. B

[ 32 ]

F = A. B = A .B

Principles of Logic Circuits

OR using NAND

A

B

A

F = A .B = A+B = A+B

B

Similarly NOR logic can also be used to construct the above siren fundamental

gates.

Boolean rules and laws

The three basic rules of Boolean alzebra are :

(i)

Commutative rule

(iii)

Distributive rule

(ii)

Associative rule

Commutative rule

(i)

(ii)

A+B=B+A

A B = B A

Associative rule

(i)

(ii)

A + (B + C) = (A + B) + C

A (B C) = (A B) C

Distributive rule

(i)

(ii)

A (B C) = A B A C

A (B C) = (A B) (A C)

Demorgan’s Law

(i)

(ii)

A B = A B

A B = A B

Other Rules

(i)

A+A=A

(iii)

A+O=A

(v)

AO = O

(ii)

(iv)

(vi)

(vii)

A+1=A

AA =A

A 1 = A

AA = A

[ 33 ]

Principles of Logic Circuits

(viii)

AA = O

(x)

A+AB = A

(xii)

A + AB = A + B

(ix)

A= A

(xi)

A (A + B) = A

(xiii)

AB + BC + B C = AB + C

2.4 Combinational Circuits

Combinational circuits are interconnected circuits of gates according to certain

rules. The output of combinational circuit are determined by the logical function of

their current input state, at any given instant of time. A combinational circuit has no

feed back loops. The combinational logic circuits are made up from basic logic such as

AND, OR and NOT gates that are connected together to produce more complicated

switching circuits. Any combinational circuits can also be implemented with only NAND

or NOR gates as these gates are universal gates.

The three ways of specifying the function of a combination logic circuit are :

(1)

Boolean alzebra–this form the alzebric expression showing the

operation of the logic circuit for each input variable.

(2)

Truth table–This defines the function of a logic gate by providing a

consise list that shows all the output states in tabular form for each

possible combination of input variable that the gate could encounter.

(3)

Logic diagram–This is a graphical representation of a logic circuit that

shows the connections of each individual logic gates, represented by

specific graphical symbol, that implement the logic circuit.

All three of these logic circuit representations are shown below in figure 4.

A

B

Logic Gates

(A.B)

Boolean Expression

F = (A. B).(A+B)

(A+B)

(a) Circuit diagram

[ 34 ]

Principles of Logic Circuits

A

B

F

0

1

0

0

0

1

1

0

1

(b) Truth table

0

0

0

Figure 4 : (a) Circuit diagram (b) Truth table

The basic design issue related to combinational circuits is Minimization of

number of gates. The normal circuit constants for combinational circuits are :

The depth of the circuit should not exceed a specific level. (figure 4 has the

depth 2.)

The number of input lines to a gates (fan in) and how many gates its output

can be fed (fan out ) are constraints by the circuit power/ constraints.

2.4.1 Canonical and Standard forms :

An algebraic expression can exist in two forms :

(i)

(i)

SOP (Sum of Products) e.g (A.B + ( A B )

POS (Product of Sums e.g (A + B). ( A B )

If a product terms of SOP expression contain every variable of that function

either in true or complement form that it is defined as a minterm or standard product.

This minterm will be true only for one combination of input values of the variables.

Let us consider a system of 3 input signals (variables) A,B & C : then it will have 8minterms rules as :

A B C , A B C , A B C , A BC , A B C , AB C & ABC

For n – input variables, the number of minterms = total number of possible

input combanations =2n.

Similar type of term used in POS form is called Maxterm or standard sum.

Maxterm is a term which ORs all input variables, either in the true or complement

form.

Let us consider with 3- input variable, we will have 8 maxterms such as :

(A + B + C), (A B C) , (A+ B +C), (A B C) , (A B C) , (A B C) ,

(A B C) and (A B C)

For n input variable number of Maxterms = 2n .

Figure 5 indirects 2n different minterm and Maxterms, where n is number of variable.

[ 35 ]

Principles of Logic Circuits

A

0

0

0

0

1

1

1

1

Variable’s Value

Minter

B

C

Term

0

1

ABC

m1

AB C

m3

0

0

1

0

1

1

0

0

AB C

0

AB C

1

1

Term

A+B+C

mo

AB C

0

1

1

AB C

Representation

m2

A B C

Mo

m4

A B C

M1

M2

A B C

M3

M4

M5

A B C

m6

M6

A B C

m7

ABC

Representation

A B C

m5

ABC

Maxter

M7

A B C

Figure 5 : 2n Minterms & Maxterms

We can represent any Boolean function alzebrically directly in minterm and

maxterm form from the truth table. For example the function F in the figure 6 in

represented in minterm form by ORing the terms where the output F is 1.

A

B

C

F

0

0

0

0

0

0

1

0

0

1

0

1

0

1

1

0

1

0

0

1

m4

1

0

1

1

m5

1

1

0

0

1

1

1

1

Figure 6 : Minterms by ORing

[ 36 ]

m2

m7

Principles of Logic Circuits

Thus F (A, B, C)

(2, 4,5,7)

= A B C A B C A B C ABC = m2 + m4 + m5 + m7 =

The complement can be obtained by ORing of the minterms corresponding to

the combinations that produce a 0 output in function. Thus

F (A,B,C) = mo + m1 + m3 + m6 that is

F =

(0, 1, 3, 6)

= A B C A B C A B C ABC

= A B C A B C A BC ABC

= (A B C ) (A B C ) (A B C ) (A B C )

= M o M1 M 3 M 6

= (0,1, 3, 6)

The symbol stands for ANDing maxterm. Thus SOP’s and POS are interconvertible, that is if one form is known then other form can directly be formed.

The Boolean function expressed as a sum of minterms or product of maxterms

has the property that each and every literal of the function should be present in each

and every term in either normal or complemented form.

Example of SOP

F = AC + B C A B C

A

C

B

F

C

A

B

C

Level 2

(OR Gates)

Level 1

(AND Gates)

[ 37 ]

Principles of Logic Circuits

Example of POS

A

C

B

F

C

B

C

A

Level 2

(AND Gates)

Level 1

(OR Gates)

2.4.2 Minimization of Gates

The simplification of Boolean expression is very useful for combinational circuit

design. The following three methods are used for this :

(i)

Alzebric simplification

(iii)

Quine Mc cluskey Method. (Beyond the scope of study).

(ii)

Karnaogh Maps

Alzebric Simplification

We have already discussed alzebric simplification. An alzebric expression can

exist in POS or SOP form The expression must be minimized before implementation.

The simplification is essential to minimize the cost of the logic network. The drawback

of this technique is that there are no specific rules for preceding step by step to

manipulate the process of simplification. For minimization of Boolean function having

more than three variable the alzebric method becomes inconvenient. For this

karnaugh map provider a better technique of simplification the alzebric function can

appear in many different form. But simplification of expression is sometimes difficult

as one may not know what rule to apply next. The karnaugh map is a simple and

direct approach of simplification of logic expression.

Karnaugh Map

The karnaugh map (K-Map) is a graphical technique for simplifying Boolean

function. The karnaugh map is a two-dimensional representation of a truth table. The

map is simply suited for simplifying Boolean function of 2 to 6 variables.

A Karnaugh map is diagram consisting of squares. Each square of the map

represents a minterm. Any logic can be written as a sum of products, that is sum of

minterms. A map of 2 variables contains 4 element (or squares), while for 3 variable it

contain 8 elements that is for n variable it contain 2n elements (or squares).

Example : Simplify F = AB C A B C A BC A B C

[ 38 ]

Principles of Logic Circuits

Solv : A B C A B C A B C A B C

= B C (A A ) A B C A B C

( ( A A ) 1)

= B (C A C ) A BC

= B (C A ) A BC

F= B C AB ABC

B

BC

A

AB

C

F

( B C A B A B C)

ABC

Figure 7 : Logic Diagram

The Logic diagram for the simplified Boolean expression is given is figure 7.

Thus if the expression is reduced then the number of gates required to build the

circuit is also reduced, which results in a more simplified circuit.

The step wise procedure for Karnaugh map is :

Step 1 :

Create a simple map depending on the number of variables in the

function. Special case is taken to represent variable in the map. The

value of only one variable change in two adjacent columns or rows. The

advantage of having change in one variable is that two adjacent columns

or rows represent a true or complement form of a single variable.

For example in figure 8 the columns which have positive A are adjacent and so

are the columns for A .

Decimal

0

1

2

3

A

B

0

0

1

1

0

1

0

1

A

0

1

(i)

[ 39 ]

B

0

1

2

3

0

1

Principles of Logic Circuits

Decimal A

0

1

2

3

4

5

6

7

Decimal

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

A

BC 00

0

0

1

4

01

11

10

5

7

6

1

3

2

(ii)

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

AB

CD

00

01

11

10

01

4

5

7

6

11

12

13

15

14

10

8

9

11

10

00

0

1

3

2

(iii)

Figure 8 (i) Two variables (ii) Three variables (iii) Four variables

Note : (i)

(ii)

(iii)

(iv)

The decimal equivalent are given to help and understand where the

position of the respective set lies. Each square can contain the value 0 or

1 or nothing.

The values 00, 01, 11 or 10 written on the top implies the value of the

respective variable.

Whenever the value of the variable is 0 it is said to represent its

compliment form.

The value of only one variable changes when we move form one row to

the next row or one column to the next column.

[ 40 ]

Principles of Logic Circuits

Step 2 :

Example :

Next the Karnaugh map maps the truth table. The value 1 is put in the

respective square belonging to the 1 value in the truth table. Rest of the

square are filled with 0.

Decimal A

0

1

2

3

4

5

6

7

Step 3 :

0

0

0

0

1

1

1

1

B

C

0

0

1

1

0

0

1

1

O

0

1

0

1

0

1

0

1

(i)

A

0

1

1

1

0

0

1

1

BC 00

01

11

10

0

1

3

2

0

1

4

0

5

0

1

0

7

1

1

6

1

1

(ii)

Figue 9 (i) Truth table (ii) Karnaugh Map

Now create simple alzebric expression from the K-map. These expression

are created by using adjency if we have two adjacent 1’s. The

expression can be simplified together since they differ only in 1 variable.

Similary we search for adjacent 4, 8 pairs and so on. As 1 can appear in

more than one adjacent pairs, we should reach for octets first then

quadrets and then for doublets. The following example will clarify this :

(The K-map of figure 9 (ii)).

BC

00

01

11

10

0

0

1

1

1

1

0

0

1

1

A

Figure 10 : K-map (mapping)

Let us see what pair can be considered in figure 10.

The pair are :

(i)

(ii)

The four 1’s in the four adjacent columns (right half of K-map)

The two 1’s in the top row (01 & 11 column).

The first pair of four 1’s can be represented as :

A B C A B C ABC ABC

[ 41 ]

Principles of Logic Circuits

= A B (C C ) AB (C C )

= A B AB = B ( A A ) = B.

The second pair of two 1’s can be represented as :

A B C A BC

= A C (B B ) = A C .

Thus the Boolean expression desired from this K-map is :

F = B AC

Note : This expression can directly be obtained from K-map ofter making doublet and

quadrets.

The expression so obtained is in SOP form. This expression can be expressed in

POS form also (already discussed in last section).

Don’t Care Condition

Boolean expression describe the behaviour of the logic networks. Each square

of a karnaugh map represents the response (i.e. output) of the network corresponding

of logic value of the input variables. Sometimes certain input combination never occur.

In such situation the output of the logic network are not specified on the K-map.

These situation are referred to as DON’T CARE CONDITIONS. These condition imply

that it does not matter whether the output produced is 0 or 1 for the specific input.

Example :

In calculation of BCD where 4-bits are used to represent decimal digits imply

we can represent 24 = 16 digits. But since we have only 10 decimal digits therefore 6

of those input combination values do not matter. These are called Don’t care

condition.

As the number of variable increase in K-map, it becomes difficult to keep track

on the input combination and corresponding outputs respectively. K-map is suited for

upto 6 variables. A tabular method was suggested to deal with the increasing number

of variables known as Quine Mcklusky they method.

2.5 Design of Combination Circuits

The digital circuits, which we use now-a-days, are constructed with NAND or

NOR gate instead of AND-OR-NOT gates. NAND and NOR gates are called universal

gates and can be used to implement any digital circuit (already discussed in earlier

sections).

[ 42 ]

Principles of Logic Circuits

2.6 Example of Logic Combinational Circuits

The design of combinational circuits can be demonstrated with some basic

combinational circuits like adders, Decoders, multiplexer Programmable Logic Array,

Read Only Memory (ROM) etc. Let us discuss each of these example briefly.

2.6.1 Adders

Adders are used for binary arithmetic. Addition and substraction circuit can be

used as the basis for implementation of multiplication and division.

A combinational circuit that performs addition of two bits is called a half

adder, while the combinational circuit that perform addition of three b its is called a

full adder.

Half Adder

0

+0

0

0

+1

1

s

s

1

+0

1

1

+1

10

s

{when, s = sum, c = cary}

c s

There addition can be implemented using truth tables as :

A

B

S

C

0

1

1

0

0

1

1

0

0

1

The K-map for S and C are :

K-map for S

A

0

1

B

0

1

1

0

0

1

0

0

1

0

0

1

K-map for C

A

0

1

B

0

1

0

1

0

0

Boolean expression for S = AB A B = A B and Boolean expression for C = AB

Logic diagram for half adder given below in the figure 11.

[ 43 ]

Principles of Logic Circuits

A

AB

B

S = AB + AB = A + B

AB

A

C = AB

B

Or

A

B

S=A+ B

C = AB

Block diagram of half adder

A

Haff

Adder

B

S

C

Figure 11 : Half adder

Full Adder

The truth table for full adder is given as

A

B

C

Sum

Carry

0

0

1

1

0

0

0

0

1

1

1

1

0

1

1

0

0

1

1

0

0

1

0

1

0

1

[ 44 ]

0

1

0

1

0

0

1

0

0

1

0

1

1

1

Principles of Logic Circuits

A

BC

K-map for sum

00

0

1

01

11

1

1

10

A

1

BC

K-map for Cary

00

01

0

1

1

11

1

1

Sum = A B C A B C A B C ABC

Carry x = ABC ABC = BC (A A) = BC

y = A B C ABC = AC ( B B) = AC

z = ABC ABC = AB (C C) = AB

Cary = x + y + z = BC + AC + AB

Logic Diagram for full Adder

A A

B B

C C

ABC

ABC

Sum

ABC

ABC

BC

AC

AB

Figure 12 : Full Adder

[ 45 ]

1

z

Boolean expression for sum and carry can be siren as :

(ii)

x

1

y

(i)

10

Carry

Principles of Logic Circuits

2.6.2 Decoders

A decoder is a combinational circuit that converts binary information from n

input lines to the maximum of 2n output lines. A binary code of n bits is capable of

representing upto 2n distinct elements of coded information. There can be 2 × 4, 3

× 8, 4 × 16, etc. type of decoders. Let us take an example of 3 × 8 decoder, which

decoders 3 bit information. Only one output line will be selected at one time to get

the value 1. Thus depending on the selected output line the information of the 3 bits

can be recognised or decoded.

I0

I1

I2

O0

O1

O2

O3

O4

O5

O6

O7

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

1

1

1

0

1

0

0

1

1

1

1

0

1

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0

0

(a) Truth Table

I0

I1

I2

Output (O0 to O7)

3×8

decoder

Enable (E)

(One of these 8 output lines

are selected) ( O0 to O7)

(b)

[ 46 ]

0

0

0

0

1

0

0

0

0

0

0

1

Principles of Logic Circuits

I0

I1

I2

a

b

c

d

e

f

g

h

000 = O0

001

010

011

100

101

110

111

O1

O2

O3

O4

O5

O6

O7

(c)

Figure 13 : 3 × 8 decoder

There are 8 AND gates named from ‘a’ to ‘h’, from which we are getting the

output numbered from O0 to O7. The output line selected is named 000 or 111 etc.

The output value of only one of the live will be 1 (given in the truth table). [The

enable line given in the block diagram is a good resource for combining two 3 × 8

decoders to make 4 × 16 decoder].

2.6.3 Multiplexers

Multiplexer or Data selector is also known as MUX. It is a device that allows

digits information from several sources to be routed into a single output line for

transmission over a common destination. It connects multiple input lines to a single

output line. At a specific time one of the input lines is selected and the selected

input passed on the output line.

[ 47 ]

Principles of Logic Circuits

In general if there are n data select lines then there are 2 n input lines to the

single output line. The multiplexing scheme thus defined is known as N × 1

multiplexer. An example of 4 × 1 MUX is given below in the figure 14.

S0

S1

O

I0

0

1

I1

I2

0

0

1

0

1

1

I1

I0

I3

I2

I3

S0

(a) Truth Table

I0

I1

I2

I3

4 ×1

Multiplexer

O

S1

(b) Block diagram 4 × 1 MUX

a

b

c

d

00

01

10

O

11

(c) Circuit diagram of 4 × 1 MUX

Figure 14 : 4 × 1 Multiplexer

For 4 × 1 mux, 4 AND gates are used named from ‘a’ to ‘d’ . Each AND gate is

connected to input line through I0 to I3 and two select line So and S1. For So = 0 and

S1 = 0 the input line becomes I0 for So = 0 and S1 = 1 the input line is I1 and so on.

[ 48 ]

Principles of Logic Circuits

Therefore by having two control lines we can have 4 × 1 mux. To have 8 × 1 Mux

we must have 3 control line. Similarly for n × 1 MUX we need to have n control lines.

The multiplexers are often used in replacement of logic gates and make the

design easier. It is also used in digital circuits for data and controlled signal routing.

The reverse circuit of multiplexing is called demultiplexing, where we have one

input line and data is transmitted to one of the possible 2n lines where ‘n’ represents

the number of selection lines.

2.6.4 Encoders

An encoder is a combinational circuit that perform a reverse function of the

decoder. An encoder has 2n input lines and ‘n’ output lines. Like 3 × 8 decoder, we

have 8 × 3 encoder, which encodes 8 bit information and produces 3 outputs

corresponding to binary numbers. This encoder is also called octal to binary encoder.

The truth table, Block diagram and circuit diagram of 8 × 3 encoder is given below :

I0

I1

I2

I3

I4

I5

I6

I7

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

D0

0

D2

0

0

0

0

1

D1

D3

D4

D5

D6

D7

(a) Truth Table

I0 – I7

8 ×3

Encoder

(b) Block Diagram

[ 49 ]

O0

O1

O2

O2

O1

O0

0

0

1

0

0

0

1

1

1

1

0

1

1

0

0

1

1

0

0

1

0

1

0

1

Principles of Logic Circuits

D1 D2 D3 D4 D5 D6 D7

O0

O1

O2

(c) Circuit diagram

Figure 15 : 8 × 3 encoder

The circuit is implemented using 3-OR gates whose inputs can be determined

from the truth table. The output can be expressed as :

O0 = I1 + I3 + I5 + I7

O1 = I2 + I3 + I6 + I7

O2 = I4 + I5 + I6 + I7

Note : A K-map can be down to determine the above function.

To avoid ambiguity the encoder circuit has input priority so that only one input

is encoded. The input with high subscript can be given higher priority. For example if

both D1 and D2 are 1 at the same time, then output, will be 010 since D2 has higher

priority than D1.

2.6.5 Programmable Logic Array (PLA)

With the advancement of technology the integration provided by the

integrated circuits technology has increased. This has resulted into production of one

to 10 gates on a single chip [Small Scale Integration (SSI)]. With large scale

integration (LSI), and very large scale integration (VLSI) we can put even more

gates on a chip and can make gate inter-connections on a chip. This integration and

connection brings the advantages of decreased cost, size and increased speed.

[ 50 ]

Principles of Logic Circuits

The drawback faced by VLSI chips is that for each logic function the layout of

gate and inter connection needs to be designed. The cost involved in making custom

designs is quite high. Thus, came the concept of programmable Logic Array, a

general purpose chip which can readily be adopted for any specific purpose at any

time.

The PLA are designed for SOP form of Boolean function and consist of regular

arrangements of NOT, AND and OR gates on a chip. Each input to the chip is passed

through a NOT gate, thus the input and its complement are available to each AND

gate. The output of each AND gate is made available for each OR gate and the

output of each OR gate is treated as chip output. By making appropriate connections

any logic function can be implemented in these Programmable Logic Array. An

example of PLA with 3 NOT gates, 3 AND and 3 OR gates is given below :

I0

I1

I2

a

b

c

I0 I1 I 2

I0 I1 I 2

I0 I1 I 2

O1

O1

Figure 16 : Programmable Logic Array

[ 51 ]

O2

Principles of Logic Circuits

2.6.6 Read Only Memory (ROM)

The Read Only Memory is an example of programmable Logic Device (PLD).

ROM is a device that includes both decoder and OR gates within a single IC

(Integrated Circuit) Package. The connection between the outputs of decoder and

inputs of OR gates can be specified for each particular configuration by

“programming” the ROM. The ROM is often used to implement a complex

combinational circuit in one IC package and thus eliminate all interconnecting wires.

ROM is a memory (storage) device in which fixed set of binary information is

stored. The binary information must first be specified by the user and then

embedded in the unit to form the required interconnection pattern.

Once a pattern is established for a ROM, it remains fixed even when power is

turned off and then on again.

A block diagram and a Logic diagram of Rom is siren below.

n input

2n × m

ROM

m output

(a) Rom block diagram

[ 52 ]

Principles of Logic Circuits

Adders

Input

A0

A1

A2

A3

A4

Minterm

5×32

decoder

0

1

2

3

.

.

.

31

F1

(b) Logic diagram

F2

F3

F4

Figure 17 : 32 × 4 ROM

Internally, the ROM is a combinational circuit with AND gates connected as a

decoder and a number of OR gates equal to the number of outputs in the unit.

The number of adders words in a ROM is determined from the fact than n

input lines are needed to specify 2n word. A ROM is some times specified by the total

number of bits it contains which is 2n × m.

For example, 128 bit ROM may be organized as 32 word of 4 bits each. This

means that the unit has 4 output lines and 5 input lines to specify 25 = 32 words.

The total number of bits stored in the unit is 32 × 4 = 128.

2.7 Summary

This unit provides the information regarding a basis of a computer system.

The basic components of circuits design are discussed such as AND, OR and NOT

gates. The key elements for the design of a combinational circuit like adders,

multiplexers, Encoder, etc. are discussed in this unit. With the advent of

Programmable Logic Array the designing of circuit is changing and now the scenario

is moving towards micro processors. You can refer to latest trends of design and

development including a hardware design language in the suggested readings.

[ 53 ]

Principles of Logic Circuits

2.8 Questions

1.

2.

3.

4.

5.

6.

7.

8.

9.

2.9

1.

2.

What are Logic gates and which gates are called as universal gates.

Simplify the Boolean function F (A, B, C, D) = (0, 2, 4, 6, 7, 8, 14,

15) and

F (A, B, C, D) = (1, 3, 4, 5, 10, 12, 13)

Draw the logic diagrams for the above question.

Show the implementation of AND, OR and NOT gates using universal

gates.

Prepare the truth table for the following Boolean expressions :

(i) AB A B ABC

(ii) (A B) (A B)

Simplify the following Boolean function in SOP and POS form by means

of Karnaugh-Maps.

F (A, B, C, D) = (0, 1, 3, 6, 8, 9, 12)

Find the optimal logic expression for the above function. Draw the

resultant logic diagram.

Describ Adders, Multiplexer and encoders.

What is PLA ? What are its advantages ?

Suggested Readings

Computer Architecture and Logic Design by Thomas. C. Bartee.

Digital Logic and computer design by Morris Man.

[ 54 ]