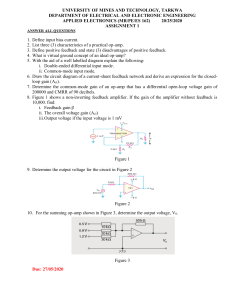

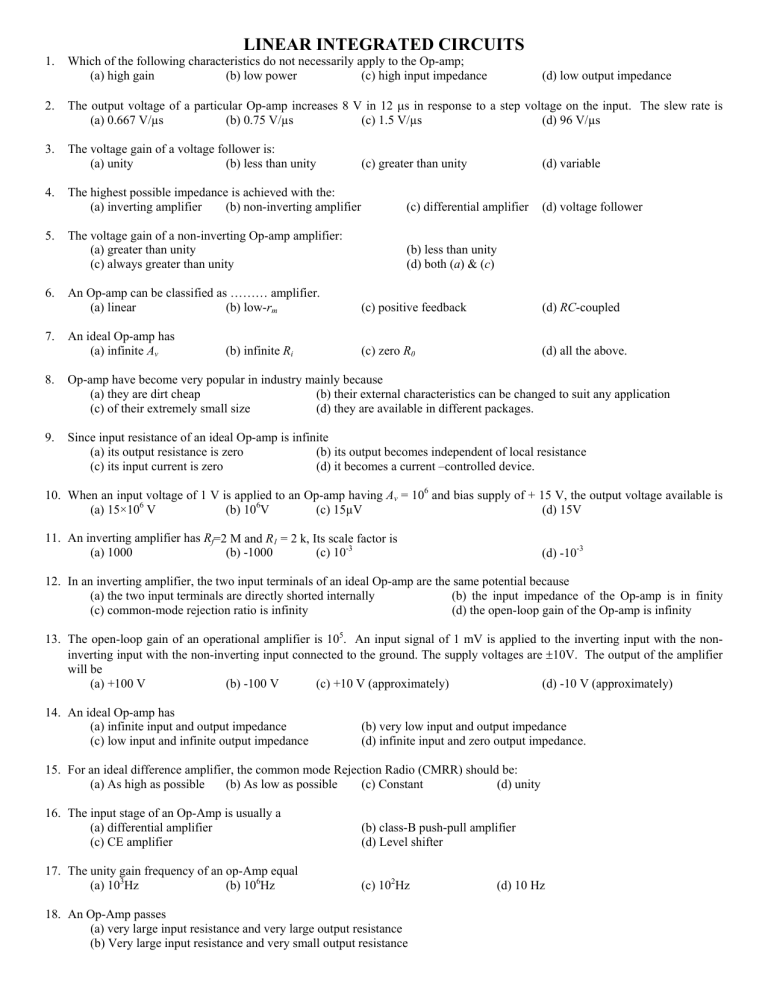

LINEAR INTEGRATED CIRCUITS 1. Which of the following characteristics do not necessarily apply to the Op-amp; (a) high gain (b) low power (c) high input impedance (d) low output impedance 2. The output voltage of a particular Op-amp increases 8 V in 12 μs in response to a step voltage on the input. The slew rate is (a) 0.667 V/µs (b) 0.75 V/µs (c) 1.5 V/µs (d) 96 V/µs 3. The voltage gain of a voltage follower is: (a) unity (b) less than unity 4. 5. 6. 7. (c) greater than unity (d) variable The highest possible impedance is achieved with the: (a) inverting amplifier (b) non-inverting amplifier (c) differential amplifier The voltage gain of a non-inverting Op-amp amplifier: (a) greater than unity (c) always greater than unity (b) less than unity (d) both (a) & (c) (d) voltage follower An Op-amp can be classified as ……… amplifier. (a) linear (b) low-rm (c) positive feedback (d) RC-coupled An ideal Op-amp has (a) infinite Av (c) zero R0 (d) all the above. (b) infinite Ri 8. Op-amp have become very popular in industry mainly because (a) they are dirt cheap (b) their external characteristics can be changed to suit any application (c) of their extremely small size (d) they are available in different packages. 9. Since input resistance of an ideal Op-amp is infinite (a) its output resistance is zero (b) its output becomes independent of local resistance (c) its input current is zero (d) it becomes a current –controlled device. 10. When an input voltage of 1 V is applied to an Op-amp having Av = 106 and bias supply of + 15 V, the output voltage available is (a) 15×106 V (b) 106V (c) 15µV (d) 15V 11. An inverting amplifier has Rf=2 M and R1 = 2 k, Its scale factor is (a) 1000 (b) -1000 (c) 10-3 (d) -10-3 12. In an inverting amplifier, the two input terminals of an ideal Op-amp are the same potential because (a) the two input terminals are directly shorted internally (b) the input impedance of the Op-amp is in finity (c) common-mode rejection ratio is infinity (d) the open-loop gain of the Op-amp is infinity 13. The open-loop gain of an operational amplifier is 105. An input signal of 1 mV is applied to the inverting input with the noninverting input with the non-inverting input connected to the ground. The supply voltages are ±10V. The output of the amplifier will be (a) +100 V (b) -100 V (c) +10 V (approximately) (d) -10 V (approximately) 14. An ideal Op-amp has (a) infinite input and output impedance (c) low input and infinite output impedance (b) very low input and output impedance (d) infinite input and zero output impedance. 15. For an ideal difference amplifier, the common mode Rejection Radio (CMRR) should be: (a) As high as possible (b) As low as possible (c) Constant (d) unity 16. The input stage of an Op-Amp is usually a (a) differential amplifier (c) CE amplifier (b) class-B push-pull amplifier (d) Level shifter 17. The unity gain frequency of an op-Amp equal (a) 103Hz (b) 106Hz (c) 102Hz 18. An Op-Amp passes (a) very large input resistance and very large output resistance (b) Very large input resistance and very small output resistance (d) 10 Hz (c) very small input resistance and very small output resistance (d) very small input resistance and very large output resistance 19. In a 741 Op-amp, There is 20 dB/decade fall-off starting at a relatively low frequency. This is due to: (a) applied load (b) internal compensation (c) impedance of the source (d) power dissipation in the chip. 20. The input differential stage of Op-amp 741 is biased at about 10 µA current. Such a low current of the input stage gives (a) high CMRR (b) high differential gain (c) low CMRR (d) high input impedance. 21. A differential amplifier is invariably used in the input stage of all Op-amp. This is done basically to provide the Op-amp with a very high (a) CMRR (b) bandwidth (c) slew-rate (d) open-loop gain 22. The slew rate of an Op-amp is 0.5 V/μs The maximum frequency of a sinusoidal input of 2 Vrms that can be handled without excessive distortion is (a) 3kHz (b) 30kHz (c) 200kHz (d) 2MHz 23. In a circuit if the open loop gain is 106 and output voltage is 10 V, the differential voltage should be (a) 10μV (b) 0.1 V (c) 100μV (d) 1μV. 24. An Op-amp has a common-mode gain of 0.01 and a differential mode gain of 105. Its common mode rejection ratio would be: (a)10-7 (b) 10 -3 (c)103 (d) 107 25. When in a negative scalar, both R1 and Rf are reduced to zero, the circuit functions as (a) integrator (b) subtractor (c) comparator (d) unity follower 26. The two terminals of an Op-amp are known as (a) positive and negative (b) differential and non-differential (c) inverting and non- inverting (d) high and low 27. The purpose of a comparator is to (a) amplify an input voltage (b) detect the occurrence of a changing input voltage (c) maintain a constant output when the d.c. input voltage changes (d) produce a change in output when an input voltage equals the reference voltage 28. The Op-amp comparator circuit uses (a) positive feedback (b) negative feedback (c) regenerative feedback (d) no feedback 29. The feedback path in an Op-amp differentiator consists of (a) a resistor (b) a capacitor (c) a resistor and a capacitor in series (d) a resistor and a capacitor in parallel 30. The feedback path in an Op-amp integrator consists of (a) a resistor (b) a capacitor (c) a resistor and a capacitor in series (d) a resistor and a capacitor in parallel 31. For the high-pass circuit to act as a differentiator, the time constant must be (a) small (b) very small in comparison to the time period of the input signal (c) very high in comparison to the time period of the input signal (d) of moderate value 32. The effect of a finite gain of an operational amplifier used in an integrator is that (a) it would not integrate (b) the slope of output will vary with time (c) the final values of the output will vary with time (d) there will be instability in the circuit 33. In an PLL, lock occurs when the (a) input frequency and the VCO frequency are the same (b) phase error is 180˚ (c) VCO frequency is double the input frequency (d) phase error is 90˚ 34. The essential blocks of a phase-locked loop (PLL)are phase detector, amplifier, (a) high-pass filter and crystal controlled oscillator (b) low-pass filter and crystal controlled oscillator (c) high-pass filter and voltage controlled oscillator (d) low-pass filter and voltage controlled oscillator 35. A second-order band-pass active filter can be obtained by cascading a low-pass second-order section having cut-off frequency, fOH with a high-pass second-order having cut-off frequency, fOL, provided (a) fOH > fOL (b) fOH < fOL (c) fOH = fOL (d) fOH ≤ 1 fOL 2 36. Higher order active filters are used for (a) bandwidth (b) gain in the passband (c) impedance (d) higher roll-of rate 37. In an Op-amp series voltage regulator, output voltage depends on (a) Zener voltage (b) voltage divider resistors (c) output voltage (d) both (a) and (b) 38. In a feedback series regulator circuit, the output voltage is regulated by controlling the (a) magnitude of input voltage (b) gain of the feedback transistor (c) reference voltage (d) voltage drop across the series pass transistor 39. An Op-amp shunt regulator differs from the series regulator in the sense that its control element is connected in (a) series with line resistor (b) parallel with the resistor (c) parallel with load resistor (d) parallel with input voltage 40. A switching voltage regulator can be of the following type: (a) step-down (b) step-up (c) inverting (d) all of the above 41. In an inverting type switching regulator, output voltage is …….. input voltage (a) lesser than (b) greater than (c) equal to (d) opposite to 42. The output voltage of a step-down type switching voltage regulator depends on (a) input voltage (b) duty cycle (c) transistor on time (d) all of the above 43. As compared to voltage regulators made up of discrete components, IC regulators have the inherent advantages of (a) self protection against over-temperature (b) remote control (c) current limiting (d) all of the above 44. A three terminal monolithic IC regulator can be used as (a) an adjustable output voltage regulator alone (c) a current regulator and a power switch (b) an adjustable output voltage regulator and a current regulator (d) a current regulator alone 45. In a switched-mode power supply (SMPS), after conversion of a.c. supply to a highly filtered d.c. voltage, a switching transistor is switched ON and OFF at a very high speed by a pulse width modulator (PWM) which generates very high frequency square pulses. The frequency of the pulses is typically in the range of (a) 100 Hz – 200 Hz (b) 500 Hz – 1Hz (c) 2 kHz – 5kHz (d) 20 kHz – 50 kHz 46. In a zero-level detector, the output changes state when the input (a) is positive (b) is negative (c) crosses zero (d) has a zero rate of change 47. Noise on the input of a comparator can cause the output to (a) hang up in one state (b) go to zero (c) change back and forth erratically between two states (d) produce the amplified noise signal 48. The effects of noise can be reduced by (a) lowering the supply voltage (b) using positive feedback (c) using negative feedback (d) using hysteresis (e) answers (b) & (c) 49. If the voltage gain for each input of a summing amplifier with a 4.7 KΩ feedback resistance is unity, the input resistance must have a value of (a) 4.7KΩ (b) 4.7KΩ divided by the no. of inputs (c) 4.7KΩ times the no. of inputs. 50. An average amplifier has five inputs. The ratio Rf/Ri must be (a) 5 (b) 0.2 (c) 1 51. In an integrator, the feedback element is a (a) resistor (b) capacitor (c) zener diode (d) voltage divider 52. For a step input, the output of an integrator is a (a) pulse (b) triangular waveform (c) spike (d) ramp 53. The rate of change of integrator’s output voltage in response to a step input is set by the (a) RC time constant (b) amplitude of step input (c) current through the capacitor (d) all of these 54. In a differentiator, the feedback element is a (a) resistor (b) capacitor (c) zener diode (d) voltage divider 55. The output of a differentiator is proportional to (a) the RC time constant (b) the rate at which input is changing (c) the amplitude of the input (d) answers (a) and (b) 56. When you apply a triangular waveform to the input of a differentiator, the output is (a) a DC level (b) an inverted triangular waveform (c) a square waveform (d) the first harmonic of triangular waveform. 57. Typically an instrumentation amplifier has an external resistance use for (a) establishing the input impedance (b) setting the voltage gain (c) setting the current gain 58. Instrumentation amplifier are used primarily in (a) high noise environment (b) medical equipment (c) test instrument (d) filter circuits 59. An OTA is basically a (a) voltage-to-current amplifier (b) current-to-voltage amplifier (c) voltage-to-voltage amplifier (d) current-to-current amplifier 60. In an OTA, the transconductance is controlled by the (a) dc supply voltage (b)input signal voltage (c)manufacturing process (d) a bias current 61. The voltage gain of an OTA circuit is set by (a) the dc supply voltage (b) transconductance only (c) transconductance and load resistor (d) bias current and supply voltage 62. The operation of a log amplifier is based on the (a) non-linear operation of an op-amp (b) the logarithmic characteristics of a PN junction (c) the reverse breakdown characteristics of a PN junction (d) the logarithmic charge and discharge of an RC circuit. 63. The units of measurement of slew rate of an opamp is (a) Volts / μ sec (b) μ volt/sec (c) dB (d) It is a dimensionless quantity. 64. While making measurements with an opamp, it was observed that currents flowing towards inverting and non inverting inputs were 4μA and 2μA. The input bias current in this case would be (a) 4μA (b) 2μA (c) 3μA (d) 2.5μA 65. While making measurements with an opamp, it was observed that currents flowing towards inverting and non inverting inputs were 4μA and 2μA. The input offset current in this case would be (a) 4μA (b) 2μA (c) 3μA (d) 2.5μA 66. An opamp having an open loop differential gain of 110 dB and a CMRR rating of 100dB will have an open loop common mode gain of (a) 100dB (b) 110dB (c) 10dB (d) zero 67. One of the following is a low noise opamp (a) μA741 (b) μA747 (c) LM 318 (d) NE 5534 68. With reference to astable mode of operation of timer 555, one of the following statements is true (a) Trigger terminal is always shorted to threshold terminal (b) Reset terminal is always grounded (c) Reset terminal is always at +VCC (d) Trigger terminal is left open 69. One of the following is an adjustable positive voltage IC regulator (a) μA 79G (b) μA78G (c) LM 323 (d) LM 340 70. A phase locked loop consists of the following principal components (a) The phase comparator, the VCO and the Error Amplifier (b) The phase comparator, VCO and LPF (c) The Phase comparator, the LPF and the Error Amplifier (d) none of these 71. A higher bandwidth low pass filter in a PLL signifies (a) Greater capture range and lesser lock up time (b) Greater capture range and Greater lock up time (c) Lesser capture range and lesser lock up time (d) Smaller capture range and lesser lock up range. 72. When a PLL is being used as a frequency synthesizer, the output is taken from (a) the LPF output (b) The VCO output (c) The output of phase comparator (d) None of these 73. When a PLL is used as a phase modulator, the modulating signal is injected (a) at the input of LPF (b) at the input of VCO (c) at the input of phase comparator (d) from the output of LPF. 74. The tracking range of a PLL (a) is same as its lock range (b) is same as capture range (c) using an high gain error amplifier (d) reducing the gain of error amplifier. 75. A phase locked loop works on the principle of feedback that is ______ in nature. (a) Regenerative (b) Degenerative (c) Either a or b (d) Does not work on the principle of feedback. 76. The phase comparator conversion gain is measured in (a) Volts per radian (b) Radians per volt (c) Radians (d) It is a dimension less quantity 77. The capture range does not depend on one of the following factors (a) Band edge of LPF (b) VCO characteristics (c) Closed loop gain of PLL (d) None of these 78. One of the following is a monolithic IC used in TV vision IF system (a) CA 3065 (b) CA 920 (c) TDA 440 S (d) CA 1044 79. If the critical frequency of a low-pass filter is increased, the bandwidth will (a) increase (b) decrease (c) not change 80. If the Q of a band-pass filter is increased, the bandwidth will (a) increase (b) decrease (c) not change 81. The term pole in filter terminology refers to (a) a high-gain op-amp (b) one complete active filter (c) a single RC circuit (d) the feedback circuit 82. A single resistor and a single capacitor can he connected to form a filter with a roll-off rate of (a) -20 dB/decade (b) -40 dB/decade (e) -6 dB/octave (d) answers (a) and (c) 83. A band-pass response has (a) two critical frequencies (b) one critical frequency (c) a flat curve in the passband (d) a wide bandwidth 122. The lowest frequency passed by a low-pass filter is (a) 1 Hz (b) 0 Hz (c) 10 Hz (d) dependent on the critical frequency 123. The quality factor (Q) of a band-pass filter depends on (a) the critical frequencies (b) only the bandwidth (c) the center frequency and the bandwidth (d) only the center frequency 124. The damping factor of a filter is set by (a) the negative feedback circuit (b) the positive feedback circuit (c) the frequency selective network (d) the gain of the op-amp The damping factor of an active filter determines the (a) voltage gain (b) critical frequency (c) response characteristic (d) roll-off rate The number of poles in a filter affect the (a) voltage gain (b) bandwidth (d) roll-off rate 125. 126. 127. 128. Sallen- Key filters are (a) single-pole filters (c) center frequency (b) second-order filters (c) Butterworth filters When filters are cascaded, the roll-off rate (a) increases (b) decreases (d) band-pass filters (c) does not change 129. When a low-pass and a high-pass filter are cascaded to get a band-pass filter, the critical frequency of the lowpass filter must be (a) equal to the critical frequency of the high-pass filter (b) less than the critical frequency of the high-pass filter (c) greater than the critical frequency of the high-pass filter 130. When the gain of a filter is minimum at its center frequency, it is (a) a band-pass filter (b) a band-stop filter (c) a notch filter (d) answers (b) and (c) 131. A maximally flat frequency response is known as Chebyshev (b) Butterworth (c) Bessel (d) Colpitts 132. In the case of line regulation. (a) when the temperature varies, the output voltage stays constant (b) when the output voltage changes, the load current Stays constant (c) when the input voltage changes, the output voltage stays constant (d) when the load changes, the output voltage stays constant 133. In the case of load regulation, (a) when the temperature varies. the output voltage stays constant (b) when the input voltage changes, the load current stays constant (c) when the load changes, the load current stays constant (d) when the load changes, the output voltage stays constant 134. All of the following are parts of a basic voltage regulator except (a) control element (b) sampling circuit (c) voltage-follower (d) error detector (e) reference voltage 135. The basic difference between a series regulator and a shunt regulator is (a) the amount of current that can be handled (b) the position of the control element (c) the type of sample circuit (d) the type of error detector 136. In a basic series regulator, VOUT is determined by (a) the control element (b) the sample circuit (a) (c) the reference voltage (d) answers (b) and (c) 137. The main purpose of current limiting in a regulator is (a) protection of the regulator from excessive current (b) protection of the load from excessive current (c) to keep the power supply transformer from burning up (d) to maintain a constant output voltage 138. In a linear regulator, the control transistor is conducting (a) a small part of the time (b) half the time (c) all of the time (d) only when the load current is excessive 139. In a switching regulator, the control transistor is conducting (a) part of the time (b) all of the time (c) only when the input voltage exceeds a set limit (d) only when there is an overload 140. The voltage gain of an OTA circuit is set by (a) a feedback resistor (c) the transconductance and the load resistor (b) the transconductance only (d) the bias current and supply voltage An OTA is basically a (a) voltage-to-current amplifier (c) current-to-current amplifier (b) current-to-voltage amplifier (d) voltage-to-voltage amplifier 141. 142. The operation of a logarithmic amplifier is based on the (a) nonlinear operation of an op-amp (b) logarithmic charac. of a pn junction (c) reverse breakdown charac. of a pn junction (d) logarithmic charge and discharge of an RC circuit 143. If the input to an antilog amplifier is x, the output is proportional to (b) ex (c) ln x (d) e-x (a) elnx 106. 107. 108. A sample-and-hold circuit is used in _______________________. A diode in the feedback loop of an op-amp behaves as a ______________. An integrated circuit (IC) op-amp has (a) two inputs and two outputs (b) one input and one output (c) two inputs and one output 109. Which of the following characteristics does not necessarily apply to an op-amp? (a) High gain (b) Low power (c) High input impedance (d) Low output impedance op 110. In the differential mode (a) opposite polarity signals are applied to the inputs (c) the outputs are different amplitudes (b) the gain is I1 (d) only one supply voltage is used In the common mode (a) both inputs are grounded (c) an identical signal appears on both inputs (b) the outputs are connected together (d) the output signals are in-phase 111. 112. 113. Common-mode gain is (a) very high (b) very low (c) always unity If Ad = 3500 and Ac = 0.35, the CMRR is (a) 1225 (b) 10,000 (c) 80 dB (d) unpredictable (d) answers (b) and (c) 114. Of the values listed, the most realistic value for open-loop gain of an op-amp is (a) 1 (b) 2000 (c) 80 dB (d) 100,000 115. A certain op-amp has bias currents of 50µA and 49.3µA. The input offset current is (a) 700 nA (b) 99.3µA (c) 49.7µA (d) none of these 116. The output of a particular op-amp increases 8 V in 12 µs. The slew rate is (a) 96 V/µs (b) 0.67 V/µs (c) l.5 V/µs (d) none of these 117. The purpose of offset nulling is to (a) reduce the gain (c) zero the output error voltage 118. (b) equalize the input signals (d) answers (b) and (c) A certain non-inverting amplifier has a Ri of 1.0 kΩ and an Rf 100 kΩ. The closed-loop gain is (a) 100,000 (b) 1000 (c) 101 (d) 100 119. A certain inverting amplifier has a closed-loop gain of 25. The op-amp has an open-loop gain of 100,000. If another op-amp with an open-loop gain of 200,000 is substituted in the configuration, the closed-loop gain (a) doubles (b) drops to 12.5 (c) remains at 25 (d) increases slightly 120. A voltage-follower (a) has a gain of 1 (b) is non-inverting (c) has no feedback resistor 121. The midrange open-loop gain of an op-amp (a) extends from the lower critical frequency to the upper critical frequency (b) extends from 0 Hz to the upper critical frequency (c) rolls off at 20 dB/decade beginning at 0 Hz (d) answers (b) and (c) 122. The frequency at which the open-loop gain is equal to 1 is called (a) the upper critical frequency (b) the cut-off frequency (c) the notch frequency (d) the unity-gain frequency 123. Each RC circuit in an op-amp (a) causes the gain to roll off at -6 dB/octave (c) reduces the midrange gain by 3 dB (d) has all of these (b) causes the gain to roll off at - 20 dB/decade (d) answers (a) and (b) 124. If a certain op-amp has a midrange open-loop gain of 200,000 and a unity-gain frequency of 5 MHz, the gainbandwidth product is (a) 200,000 Hz (b) 5,000,000 Hz (c) 1 X 1012 Hz (d) not determinable from the information 144. In a zero-level detector, the output changes state when the input (a) is positive (b) is negative (c) crosses zero (d) has a zero rate of change 145. Noise on the input of a comparator can cause the output to (a) hang up in one state (b) go to zero (c) change back and forth erratically between two states (d) produce the amplified noise signal 146. The effects of noise can be reduced by (a) lowering the supply voltage (c) using negative feedback (d) using hysteresis (b) using positive feedback (e) answers (b) and (d) 147. A comparator with hysteresis (a) has one trigger point (b) has two trigger points a variable trigger point (d) is like a magnetic circuit 148. (a) 5 An averaging amplifier has five inputs. The ratio Rf/Ri must be (b) 0.2 (c) 1 149. (a) resistor In an integrator, the feedback element is a (b) capacitor (c) zener diode (d) voltage divider 150. (a) a pulse For a step input, the output of an integrator is (b) a triangular waveform (c) a spike (d) a ramp (c) has 151. The rate of change of an integrator's output voltage in response to a step input is set by (a) the RC time constant (b) the amplitude of the step input (c) the current through the capacitor (d) all of these 152. (a) resistor In a differentiator, the feedback element is a (b) capacitor (c) zener diode (d) voltage divider 153. The output of a differentiator is proportional to (a) the RC time constant (b) the rate at which the input is changing (c) the amplitude of the input (d) answers (a) and (b) 154. When you apply a triangular waveform to the input of a differentiator, the output is (a) a dc level (b) an inverted triangular waveform (c) a square waveform (d) the first harmonic of the triangular waveform 155. Typically. an instrumentation amplifier has an external resistor used for (a) establishing the input impedance (b) setting the voltage gain (c) setting the current gain (d) interfacing with an instrument 156. In an OTA, the transconductance is controlled by (a) the dc supply voltage (b) the input signal voltage (c) the manufacturing process (d) a bias current 108. 109. A certain op-amp has an open loop gain of 80,000. The maximum output levels of this particular device are ±12V when the dc supply voltages are ±15V. If a differential voltage of 0.15 Vrms is applied between the inputs, what is the peak-to-peak value of the output? 110. Determine the output level (max. positive or max. negative) for each comparator shown below. U1 1V - Vo + uA741 111. Determine the output level (max. positive or max. negative) for each comparator shown below. U2 2V + uA741 Vo 112. Determine the output level (max. positive or max. negative) for each comparator shown below. U3 7V - Vo + uA741 5Vdc 113. Calculate VUT for the Schmitt trigger circuit shown below, if VO(max) = ±10V. R Vi U4 - Vo + R1 47k uA741 R2 18k 114. Calculate VLT for the Schmitt trigger circuit shown below, if VO(max) = ±10V. R Vi U4 - Vo + R1 47k uA741 R2 18k 115. Calculate VH for the Schmitt trigger circuit shown below, if VO(max) = ±10V. R Vi U4 - Vo + R1 47k uA741 R2 18k 116. Find the output voltage when the input voltages shown in figure below are applied to the scaling adder. +2V 10k 10k U6 +3V - 33k +3V Vo + 91k uA741 +6V 180k 117. A certain OTA with a transconductance of 5000µS has a load resistance of 10KΩ. If the input voltage is 100mV, what is the output current? 118. A certain OTA with a transconductance of 5000µS has a load resistance of 10KΩ. If the input voltage is 100mV, what is the output current? What is the output voltage? 119. Determine the output voltage for the log amplifier shown below. Assume IS = 60nA. 1.5V 47k U8 - Vo + uA741 120. Determine the output voltage for the anti-log amplifier shown below. Assume IS = 60nA. 0.225V 10k U7 + uA741 Vo