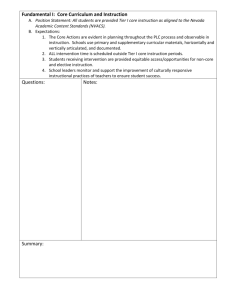

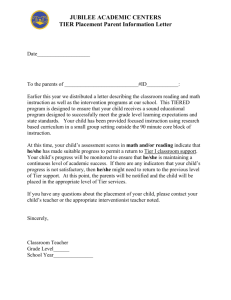

Four Tiers – “Tee” Intersection ● ● ● ● Tier One – Minimum requirement to pass lab and the course (60/100) Tier Two – Adds more complexity (75/100) Tier Three – Adds more complexity to Tier Two (95/100) Tier Four – Adds more complexity to Tier Three 105/100 2 The DLD project is to be performed in two to three weeks at the end of the semester. A minimum of Tier One must be completed to pass the lab and the course. Each tier adds complexity to the previous tier and is award an increasing number of points. The number of points out of 100 are shown in the table. Four Tier Structure Order of Completion Suggested Folder Structure 3 Since each tier is an enhancement of the previous tier start with Tier One and work yourself up the ladder to the tier to which you and your partner(s) agree.. Use a tree structure for each tier. The Timing Module of Tier One will be the same for all subsequent tiers. The Decoder Module will add more output signals as you move up from Tier One. The finite state machine, FSM Module, will add new states as you move up from Tier One. Each the previous discussed modules should be software simulated to test and verify that they work properly. Only add the prescaler in the folder Tier i for I = 1 to 4. Background Material ● ● ● Read section 9.7 in lecture notes first Read and reread project description Watch Project Video 4 I would suggest that you read or view the background material in the order presented above. Think about and discuss with your partner(s) your design approach for each of the modules. State Transition Diagram 4-Way Intersection Red48 Grn26 Ylw48 Ylw26 Grn48 Red26 Reset Note one-timer cycle E and not three – short, medium, and long 5 Each module that is based on a finite state machine should have state transition diagram similar to what is shown above. This diagram was taken out of section 9.7 in the lecture notes. The name of each of the six states used in the FSMmodule is listed on the state transition diagram. In addition the reset state is indicated. If you use the State Machine Editor/Wizard to implement the design, you can add these details in the State Machine Wizard. Please note this design only uses one timing cycle labeled E. Your design will have three called short, medium, and long. T-Intersection Phase Sets Tier One No Preferential Turn Left ● Phase 1 and Phase 6 ● Phase 4 and Phase 8 ● Ignore special signals for Phase 3 and Phase 7 6 Your project is based on a tee-intersection with roads coming from the east, west, and south. Each lane of traffic has a phase associated with it. Two phantom lanes coming from the north are included in the counting sequence. This is a hold over from section 9.7 in the lecture notes. Each non-conflicting traffic flow lanes are combined into phase sets. In this diagram we have phase sets [Φ1Φ6] and [Φ4 Φ8]. Note the phases Φ3, right turn lane from west, and Φ7, left turning lane from east, are not in the phase sets and consequently signal lights. They would only see red, yellow, and green signals and would use normal right-of-way rules to make their turns. All four tiers require a timing module that meets the design requirements listed above. The FSM module will use the appropriate signal of short, medium, or large to detect the end of the signal for that phase set and will send a resetting signal back to the timer module. Decoder Module Tier One ● ● ● P[1] to P[8] from FSM TI from FSM SG, SY, SR, EG, EY, and ER to display the trafic signal lamps. 8 The decoder module will receive the phase signals P[1] through P[8] with phantom phases P[2] and P[5] included. You may make these discrete signals or signal vectors. The same is true for TI to be discussed later. The six traffic signals listed above will be the outputs. It is assumed for this tier EG would be wired in parallel with WG, EY with WY, and ER with WR. Concatenation of P and TI ● ● ● P, (8 DOWN TO 1), and TI, (1 DOWN TO 0), come from FSM TIP, (10 Down TO 1), local to Architecture TIP <= TI & P; -Concatenation 9 If you treat P and TI as vectors, you may find is useful to concatenate the signal vector P and the signal vector TI into a single signal vector I called TIP. Within the decoder module architecture the signal TIP was declared as a vector of 10 down to 1. Then to perform the concatenation the statement TIP <= TI & P; was placed following the BEGIN phrase. Within the WITH – SELECT block a ten signal vector is used with the WHEN phrase. You may use the discrete red LEDs to indicate which signal are lite. Or you may use the seven segment displays. The figure above show one possible set of assignments. While the colors will not be correct, their relative positions will be correct. This set of assignments should work all the way through Tier Four. Finite State Machine ● ● Write your own VHDL Use State Machine Editor/Wizard 11 To implement the FSM module you have two approaches. You can write your own VHDL from scratch or you can use the State Machine File tools within Quartus Prime. These tools consist of a State Machine Editor which is a graphics editor and a State Machine Wizard. One your design is enetered into the State Machine tools, you select the HDL icon and Quartus Prime will implement all of the VHDL for you. I have placed several tutorial on Brightspace for the lab which should help you learn how to use this tool. Phases & Timer Interval ● P[1] – South Left Turn ● P[2] – Unused ● TI[1:0] Description 00 Right-of-Way has Green P[3] – West Right Turn 01 Preferential Turn has Arrow 10 Right-of-Way has Yellow ● P[4] – East Thru 11 Conflicting Traffic has Red ● P[5] – Unused ● P[6] – South Right Turn ● P[7] – East Left Turn ● P[8] – West Thru 12 The definition for the P and TI signals are listed above. The TI[1:0] is a translation of Table 3 in the project description. The layout shown above summarize the inputs and outputs for each module. The prescaler may be embedded in the timing module or an LPM_COUNTER. It is assumed the the tophierarchy will be a BDF. Tier Two breaks the intersection into the three cardinal directions of east, west, and south. The timer module does not need to change. The finite state machine module will add P[3] and P[7] phases. You will now have three phase sets instead of two used in Tier One. Add the signals WG, WY, and WR as outputs to the decoder module. Tier Three Add Loop Detectors ● Timing Module stays the same ● FSM ● – Six individual phases are now possible – Use six phase set, see project description – South phase set, East - West past sets – End with Phase set P4-P8 – Each phase responds to loop detectors (Lj = ‘1’ Use; Lj = ‘0’ Skip) Decoder adds STG, STY, ETG, ETY, WTG, and WTY 15 In Tier Three the timing module stays the same. All six of the phases participate in six phase sets. You must determine the phase sets based on hints in the project description. Each phase also has a loop detector labeled L[1] through L[8] and is associated with phase P[1] through P[8] respectively. The loop detectors should determine the next state the finite state machine should enter. Thus L 8 down to 1 inputs should be added to the finite state machine module. The decoder module should add the outputs STG (south turning green), STY (south turning yellow), ETG, ETY, WTG, and WTY. Tier Four Skip “Carless” Phase Set ● Timing Module no change ● FSM – Skip car-less phase sets ● Decoder no change ● May want to add module 16 Tier Four changes the timing of the traffic light controller. The same timing is used for the traffic light controller but with the following addition. In none of the loop detectors associated with the active phases are active but another loop detector Lj is active, then the finite state machine module begins the process of transitioning to a phase set that includes phase Φ j.