Electronics 245

Lecture 2

Semiconductor Theory – Chapter 1

1.1 – Semiconductor Materials and Properties

1.1.1 – Intrinsic Semiconductors

1.1.2 – Extrinsic Semiconductors

What is a Semiconductor?

Key Concepts

• Insulator

• Electricity cannot pass through these materials.

• Examples: glass, wood, plastic etc.

• Conductor

• Electricity can pass easily through the material due to its low

resistance.

• Examples: aluminium, copper, etc.

• Semiconductor

• Materials with electrical conductivity somewhere between

insulators and conductors.

• Examples: silicon, germanium etc.

Band Theory of Solids

Key Concepts

• Electrical conductivity ≡ movement of electrically

charged particles

• Require electrons in the conduction band

• Band gap distance represents energy required to break

covalent bonds

Valency

• Bohr atomic model

• Valence electrons in outer “shell” or

orbital

• Valency → chemical reactivity

• Elements grouped according to valency

Key Concepts

Elemental and Compound Semiconductors

• Elemental

• Made up of a single element

• Compound

• Made up of more than one element

Silicon Crystal Lattice

Intrinsic semiconductors

• Silicon very popular as elemental semiconductor

• Four valence electrons. Can therefore form covalent bonds with 4

neighbouring atoms

• All valence electrons used in bonding process

Breaking Covalent Bonds

Intrinsic semiconductors

T = 0 [K]

• @ Temperature, T = 0 [K]

• All bonding positions filled

• Applied electric field will not move electrons

• No charge flows ∴ insulator

• @ Temperature, T > 0 [K]

• An electron could gain sufficient thermal energy to

break its covalent bond

• Electron in conduction band and positively charged

empty state

• Minimum energy required is called bandgap energy

T > 0 [K]

Bandgap Energy

• Electrons which have gained 𝑬𝒈 now exist in the

conduction band

• Free electrons – can act as charge carriers

• 𝑬𝒗 – maximum energy of valence energy band

• 𝑬𝒄 – minimum energy of conduction band

• 𝑬𝒈 – bandgap energy

• Silicon bandgap energy ≈ 1eV (of the order of)

Intrinsic semiconductors

Concept of a “hole”

• Breaking of covalent bond creates empty,

positively charged, space

• Adjacent valence electrons with sufficient

thermal energy could move into the free

position

• Moving positive charge called a hole.

• Holes are charge carriers ∴ contribute to

current flow

Intrinsic semiconductors

Intrinsic Carrier Concentration

• Intrinsic semiconductor consists of one element ie. Single-crystal

material

• Density of electrons and holes are equal

• Number of electrons in conduction band, intrinsic carrier

concentration, 𝑛𝑖 :

• 𝑛𝑖 =

−𝐸𝑔

𝐵𝑇 3Τ2 𝑒 2𝑘𝑇

[#Τcm3 ]

• 𝐵 – coefficient for semiconductor material, in

• 𝑇 – temperature in Kelvin, K

• 𝐸𝑔 – bandgap energy in eV

• 𝑘 – Boltzmann’s constant = 86 x 10-6 eV/K

3

cm−3 K − Τ2

1cm

Intrinsic Carrier Concentration Example

Calculate the intrinsic carrier concentration in silicon at 𝑇 = 300 K

3Τ2

𝑛𝑖 = 𝐵𝑇

𝑛𝑖 = (5.23 x

𝑒

−𝐸𝑔

2𝑘𝑇

𝑘 = 86 x 10−6

−1.1

Τ2 2∙86x10−6 ∙300

15

3

10 )(300) 𝑒

𝑛𝑖 = 1.5 x 1010 cm−3

Extrinsic Semiconductors

• Low concentration of free electrons in intrinsic

semiconductors ∴ low currents

• Impurities are introduced (doping) to alter the

electrical properties

• The foreign elements are then the main

contributor to charge carriers

• For group 4 elemental semiconductors, desirable

impurities are from group III or V

Two Categories of Extrinsic Semiconductors

• n-type semiconductors

• Group V impurities added

• Contains donor impurities which donate an electron

• Greater number of electrons compared to holes

n-type semiconductors

• p-type semiconductors

• Group III impurities added

• Contains acceptor impurities which accept an electron

• Greater number of holes compared to electrons

p-type semiconductors

Conductivity in an Extrinsic Semiconductor

• Doping allows control of the charge carrier concentration which is directly

proportional to the conductivity of the semiconductor.

• The relationship between electron and hole concentrations:

𝑛𝑜 𝑝𝑜 = 𝑛𝑖2 :

𝑛𝑜 − concentration of free electrons

𝑝𝑜 − concentration of holes

𝑛𝑖 − intrinsic carrier concentration

𝑛𝑖 = 𝐵𝑇 3Τ2 𝑒

−𝐸𝑔

2𝑘𝑇

If donor concentration 𝑁𝑑 ≫ 𝑛𝑖 :

If acceptor concentration 𝑁𝑎 ≫ 𝑛𝑖 :

𝑛𝑜 ≅ 𝑁𝑑

𝑝𝑜 ≅ 𝑁𝑎

𝑛𝑖2

∴ 𝑝𝑜 = 𝑁

𝑑

∴ 𝑛𝑜 =

𝑛𝑖2

𝑁𝑎

Extrinsic Carrier Concentration Example

Calculate the thermal equilibrium electron and hole concentrations

Consider silicon at 𝑇 = 300 K doped with phosphorous at a concentration of 𝑁𝑑 = 1016 cm−3 . For silicon 𝑛𝑖 =

1.5 x 1010 cm−3 .

𝑛𝑜 𝑝𝑜 = 𝑛𝑖 2

𝑝𝑜 =

𝑛𝑖 2

𝑁𝑑

=

𝑛𝑜 ≅ 𝑁𝑑 = 1016 cm−3

(1.5 x 1010 )2

1016

= 2.25 x 104 cm−3

Consider silicon at 𝑇 = 300 K doped with boron at a concentration of 𝑁a = 5 x 1016 cm−3 .

𝑝𝑜 ≅ 𝑁𝑎 = 5 x 1016 cm−3

𝑛𝑜 =

𝑛𝑖 2

𝑁𝑎

=

(1.5 x 1010 )2

5 x 1016

= 4.5 x 103 cm−3

Observation – what do the results tell us about the carrier concentrations after doping in relation to 𝒏𝒊 ?

Example

Find the concentration of electrons and holes in a sample of germanium

that has a concentration of donor atoms equal to 1015 cm−3 . Is the

semiconductor n-type or p-type?

First – calculate the intrinsic carrier concentration of germanium

𝑛𝑖 = 𝐵𝑇 3Τ2 𝑒

−𝐸𝑔

2𝑘𝑇

= 1.66x1015 300

𝑛𝑜 𝑝𝑜 = 𝑛𝑖 2

𝑝𝑜 =

𝑛𝑖 2

𝑁𝑑

=

3Τ2

𝑒

−0.66

2 86x10−6 300

𝑛𝑜 ≅ 𝑁𝑑 = 1016 cm−3

(2.4 x 1013 )2

1015

= 5.76 x 1011 cm−3

This is an n-type semiconductor

Why?

= 2.4 x 1013 cm−3

In Conclusion

Electronics 245

Lecture 3

Semiconductor Theory – Chapter 1

1.1.3 – Drift and Diffusion Currents

1.1.4 – Excess Carriers

1.2 – The pn Junction

1.2.1 – The Equilibrium pn Junction

COPYRIGHT

Copyright © 2020 Stellenbosch University

All rights reserved

DISCLAIMER

This content is provided without warranty or representation of any kind. The

use of the content is entirely at your own risk and Stellenbosch University (SU)

will have no liability directly or indirectly as a result of this content.

The content must not be assumed to provide complete coverage of the

particular study material. Content may be removed or changed without

notice.

The video is of a recording with very limited post-recording editing. The video

is intended for use only by SU students enrolled in the particular module.

Drift and Diffusion Currents

• Drift – movement of carriers due to force exerted by

an Electric field

• Diffusion – movement of carriers due to concentration

gradients

• Mobile electrons and/or holes are required for current

Drift Current (n-type)

• For n-type, applied 𝐸 creates a force in the opposite

direction

• Electrons reach a drift velocity, 𝑣𝑑𝑛 :

• 𝑣𝑑𝑛 = −𝜇𝑛 𝐸

• 𝜇𝑛 → electron mobility

• Movement (drift) of electrons produces a drift current

density, 𝐽𝑛 :

• 𝐽𝑛 = −𝑒𝑛𝑣𝑑𝑛 = 𝑒𝑛𝜇𝑛 𝐸

• 𝑛 → concentration of electrons

• 𝑒 → magnitude of charge (1.6 x 10−19 )

Drift Current (p-type)

• For p-type, applied 𝐸 creates a force in the same

direction

• Holes reach a drift velocity, 𝑣𝑑𝑝 :

• 𝑣𝑑𝑝 = 𝜇𝑝 𝐸

• 𝜇𝑝 → hole mobility

• Movement (drift) of holes produces a drift current

density, 𝐽𝑝 :

• 𝐽𝑝 = 𝑒𝑝𝑣𝑑𝑝 = 𝑒𝑝𝜇𝑝 𝐸

• 𝑝 → concentration of holes

• 𝑒 → magnitude of charge (1.6 x 10−19 )

Total Drift Current

• Semiconductor contains free electrons and holes

• Total drift current density, 𝐽:

• 𝐽 = 𝐽𝑛 + 𝐽𝑝 = 𝑒𝑛𝜇𝑛 𝐸 + 𝑒𝑝𝜇𝑝 𝐸 = 𝜎𝐸 =

• 𝜎 = 𝑒𝑛𝜇𝑛 + 𝑒𝑝𝜇𝑝 → conductivity

• 𝜌=

1

𝜎

1

𝐸

𝜌

→ resistivity

• Conductivity related to concentration of free electrons and holes

• Conductivity controlled by doping:

• n-type → 𝑛 >> 𝑝

• p-type → 𝑝 >> 𝑛

𝜇𝑛 - typically 1350 cm2 ΤV − s

𝜇𝑝 - typically 480 cm2 ΤV − s

• Conductivity vs doping concentration is not linear

• Drift velocity saturation ≈ 107cm/s

• Carrier mobility is also a function of impurity concentrations.

Drift Current Example 1.3

Calculate the drift current density for silicon at 𝑇 = 300 K doped with arsenic

atoms at a concentration of 𝑁𝑑 = 8 x 1015 𝑐𝑚−3 . Assume mobility values of 𝜇𝑛 =

1350𝑐𝑚2Τ𝑉 − 𝑠 and 𝜇𝑝 = 480𝑐𝑚2Τ𝑉 − 𝑠. Assume the applied electric field is 100V/cm.

𝑛𝑜 ≅ 𝑁𝑑 = 8 x 1015 cm−3

∴ 𝑝𝑜 =

𝑛𝑖 2

𝑁𝑑

=

(1.5 x 1010 )2

8 x 1015

𝑛𝑖 = 1.5 x 1010 cm−3

= 2.81 x 104 cm−3

𝐽 = 𝐽𝑛 + 𝐽𝑝 = 𝑒𝑛𝜇𝑛 𝐸 + 𝑒𝑝𝜇𝑝 𝐸

𝐽 = 1.6 x 10−19 8 x 1015 1350 100 + 1.6 x 10−19 2.81 x 104 480 100

∴ 𝐽 = 172.8 AΤcm2

Diffusion Current

• 𝐽𝑛 =

𝑑𝑛

𝑒𝐷𝑛

𝑑𝑥

• 𝐷𝑛 → electron diffusion coefficient

•

𝑑𝑛

𝑑𝑥

→ gradient of electron concentration

• 𝐽𝑝 = −𝑒𝐷𝑝

𝑑𝑝

𝑑𝑥

• 𝐷𝑝 → hole diffusion coefficient

•

𝑑𝑝

→

𝑑𝑥

gradient of hole concentration

Einstein Relation

• Mobility and the diffusion coefficient are related by Einstein’s

relation:

•

𝐷𝑝

𝜇𝑝

=

𝐷𝑛

𝜇𝑛

=

𝑘𝑇

𝑒

= 𝑉𝑇

• 𝑉𝑇 ≅ 0.026 𝑉 @ 300 𝐾 – room temperature

• 𝑉𝑇 is the thermal voltage

• 𝑘 = 1.38 x 10−23 J/K

Also Boltzmann’s constant…

Excess Carriers

• Up to this point we have assumed thermal equilibrium*

• Breaking covalent bonds creates electron-hole pair

• Called excess electrons and holes

• Electron and hole concentrations increase above their thermal equilibrium values

• Total carrier concentration represented by:

• 𝑛 = 𝑛𝑜 + 𝛿𝑛

• 𝑝 = 𝑝𝑜 + 𝛿𝑝

• where:

• thermal equilibrium concentration is 𝑛𝑜 , 𝑝𝑜

• excess concentration is 𝛿𝑛, 𝛿𝑝.

• Electron-hole recombination occurs.

• Mean time that the excess carriers exist is called the excess carrier lifetime.

*Thermal equilibrium: balanced system – no net effect

The pn Junction

1.2.1

Formed when a p-type and n-type are adjacent to one

another

Two Categories of Extrinsic Semiconductors

• n-type semiconductors

•

•

•

•

•

Contains donor impurities which donate an electron

Greater number of electrons compared to holes

Electrons are the majority carrier

Holes are the minority carrier

Group V impurities added

n-type semiconductors

• p-type semiconductors

•

•

•

•

•

Contains acceptor impurities which accept an electron

Greater number of holes compared to electrons

Electrons are the minority carrier

Holes are the majority carrier

Group III impurities added

p-type semiconductors

The Equilibrium pn Junction

• p-type and n-type semiconductor joined at 𝑡 = 0.

• x = 0 → metallurgical junction

• Different concentrations

• Diffusion current until equilibrium across junction

• Equilibrium → steady-state without external influence.

Space-Charge/Depletion Region

• Electric field set up by charge separation

• Electric field repels the diffusion of carriers

across the junction

• Thermal equilibrium occurs when E-field and

diffusion forces balance

• Space charge/depletion region.

• No mobile electrons or holes

• The potential voltage set up is given by:

• 𝑉𝑏𝑖 =

• 𝑘 =

𝑘𝑇

𝑁 𝑁

ln 𝑎 2 𝑑

𝑒

𝑛𝑖

1.38 x 10−23

= 𝑉𝑇 ln

J/K

𝑁𝑎 𝑁𝑑

𝑛𝑖2

Also Boltzmann’s constant…

Space-Charge/Depletion Region

Example 1.5

Calculate the built-in potential barrier of a pn junction.

Consider a silicon pn junction at T = 300 K, doped at 𝑁𝑎 = 1016 cm−3 in the pregion, and 𝑁𝑑 = 1017 cm−3 in the n-region.

𝑛𝑖 = 1.5 x 1010 cm−3

𝑉𝑏𝑖 = 𝑉𝑇 ln

𝑁𝑎 𝑁𝑑

𝑛𝑖2

Silicon at room temperature

= 0.026 ln

1016 1017

1.5 x 1010 2

= 0.757 V

Comment – The magnitude of 𝑉𝑏𝑖 is not a strong function of the doping concentrations.

Therefore the value of 𝑉𝑏𝑖 is usually within 0.1 V to 0.2 V of the above value of 0.757 V

for silicon pn junctions.

In Conclusion

Electronics 245

Lecture 4

Semiconductor Theory – Chapter 1

1.2 – The pn Junction

1.2.2 – The Reverse-Biased pn Junction

1.2.3 – Forward-Biased pn Junction

1.2.4 – Ideal Current-Voltage Relationship

1.2.5 – pn Junction Diode

Reverse-Biased pn Junction

• Apply a voltage, 𝑉𝑅 , to the pn junction

(equilibrium).

• An additional Electric Field, 𝐸𝐴 , is applied to

the junction.

• The magnitude of the total Electric Field

increases.

• The width of the space charge region

increases.

• This polarity of the applied voltage is called

reverse bias.

Carrier Concentrations – Reverse Bias

• Apply a reverse-bias voltage.

• What happens to the minority carriers?

• Carriers swept across the junction near

edge of depletion region.

• Steady state is achieved.

Steady-state minority carrier concentration

Junction Capacitance

•

•

•

•

•

•

An increase in 𝑉𝑅 .

Electric field increases - reverse bias.

Width of the space charge region increases.

Additional charges are uncovered.

A capacitance is associated with the pn junction – charge separation.

This junction, or depletion layer, capacitance is given by:

• 𝐶𝑗 = 𝐶𝑗𝑜 1 +

𝑉𝑅 −1Τ2

,

𝑉𝑏𝑖

• 𝐶𝑗𝑜 - Junction capacitance at 0 V.

Exercise Problem

A silicon pn junction at 𝑇 = 300 K is doped at 𝑁𝑑 = 1016 cm−3 and 𝑁𝑎 =

1017 cm−3 . The junction capacitance is to be 𝐶𝑗 = 0.8 pF when a reverse

bias voltage of 𝑉𝑅 = 5 V is applied. Find the zero-biased junction

capacitance 𝐶𝑗𝑜.

𝑉𝑅 −1Τ2

𝐶𝑗 = 𝐶𝑗𝑜 1 + 𝑉

? 𝑏𝑖

𝑉𝑏𝑖 = 0.026 𝑙𝑛

0.8 = 𝐶𝑗𝑜 1 +

𝐶𝑗𝑜 = 2.21 pF

(1017 )(1016 )

(1.5 x1010 )2

−1Τ2

5

0.757

𝑁𝑎 𝑁𝑑

𝑉𝑏𝑖 = 𝑉𝑇 ln

𝑛𝑖2

= 0.757 V

Forward-Biased pn Junction

• Zero applied voltage – barrier prevents

diffusion across the space-charge region.

• Apply a forward bias voltage, 𝑣𝐷 .

• Note the polarity of the voltage source.

• Introduces a counter-acting E-field, 𝐸𝐴 .

• Width of space charge region decreases as

net Electric Field decreases.

• Diffusion occurs. Why?

• Current flows.

Carrier Concentrations – Forward Bias

• As the potential barrier is reduced, diffusion starts

to occur.

• Majority carriers cross the junction to become

minority carriers.

• Steady state is achieved.

• Diffusion and recombination occur simultaneously.

• Important for switching applications later on.

Steady-state minority carrier concentration.

Ideal Current-Voltage Relationship

• Relation to describe the applied voltage to the current flowing

through the pn junction:

• 𝑖𝐷 = 𝐼𝑆 𝑒

𝑣𝐷

𝑛𝑉𝑇

−1

.

• 𝐼𝑆 - reverse-bias saturation current

• 𝑛 – emission coefficient or ideality factor.

• Here we can see:

• Reverse bias – no, or very small, current flow

• Forward bias – exponential current flow.

The pn Junction Diode

• Operation approximated by ideal characteristics.

• Equation – ideal current-voltage relationship

• Can think of as a switch

• Two modes of operation, off and on

off

The diode circuit symbol

𝑖𝐷 = 𝐼𝑆 𝑒

𝑣𝐷

𝑛𝑉𝑇

.

−1

on

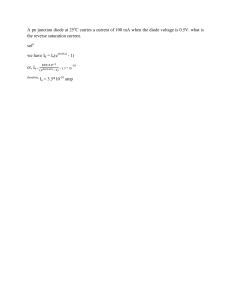

Example (TYU 1.7)

A silicon pn junction diode at 𝑇 = 300 K has a reverse-saturation current of

𝐼𝑆 = 10−16 A. (a) Determine the forward-bias diode current for 𝑉𝐷 = 0.55 𝑉

(b) Find the reverse-bias diode current for 𝑉𝐷 = −0.55 𝑉.

a) 𝑖𝐷 = 𝐼𝑆 𝑒

𝑣𝐷

𝑛𝑉𝑇

𝑖𝐷 = 10−16

b) 𝑖𝐷 = 10−16

or

−1

.

𝑒

𝑒

0.55

0.026

−0.55

0.026

.

.

− 1 = 0.15381 μA

− 1 = −10−16 A

a) 𝑖𝐷 = 𝐼𝑆 𝑒

𝑣𝐷

𝑛𝑉𝑇

.

𝑖𝐷 = 10−16

b) 𝑖𝐷 = 10−16

𝑒

0.55

0.026

.

𝑒

Observation - What is the difference between these two approaches?

Can neglect the −𝟏 for 𝑣𝐷 > +0.1 V

−0.55

0.026

.

= 0.15381 μA

= 6.5−26 A

Temperature Effects

• 𝐼𝑆 and 𝑉𝑇 are both functions of temperature.

• An increase in temperature increases the number

of free carriers (𝑛𝑖 ).

• 𝑉𝑇 =

𝑘𝑇

𝑒

• The current-voltage relation of a diode will

therefore also vary with temperature.

• For the same current, a lower 𝑣𝐷 is required

if 𝑇 increases.

Reverse Breakdown

• E-field increases until covalent bonds start to break.

• Electron-hole pairs are created.

• Electrons are swept into the n region.

• Holes are swept into the p region.

• This increases with increasing reverse bias voltage

until breakdown occurs.

• There are various breakdown mechanisms.

• Avalanche breakdown is the most common.

• Breakdown voltage is a function of the doping

concentrations.

• The breakdown voltage of a diode is called the Peak

Inverse Voltage (PIV).

• The PIV depends on the fabrication parameters of

the diode. Usually between 50 – 100 V.

• Special application includes the zener diode with a

PIV as low as 5 V.

Avalanche breakdown

Switching Transients

• Examine the pn junction diodes switching characteristics.

• @ t < 0, 𝑖𝐷 = 𝐼𝐹 =

𝑉𝐹 − 𝑣𝐷

𝑅𝐹

• Excess charge stored in n and p regions.

• The excess charge must be removed when switching from

forward to reverse bias.

• Large currents flow in reverse direction.

−𝑉𝑅

𝑅𝑅minority

Steady-state

• 𝑖𝐷 = −𝐼𝑅 ≅

carrier concentration.

concentration

𝑡𝑠 - storage time

𝑡𝑓 - fall time

In Conclusion

Electronics 245

Lecture 5

Semiconductor Theory – Chapter 1

1.3 - Diode Circuits: DC Analysis and Models

1.3.1 – Iteration and Graphical Analysis Techniques

1.3.2 – Piecewise Linear Models

1.3.3 – Computer Simulation and Analysis

The Ideal Diode

• The ideal diode does not attempt to approximate the ideal

current-voltage relationship.

• We use the ideal diode to determine the logic states.

• Two states are possible:

• Reverse bias – off.

• Conducting – on.

ideal current-voltage relationship

ideal diode

on

ideal diode I-V characteristics

off

Ideal Diode Model - Example

The output waveform is rectified

DC Analysis of Diode Circuits

• Characteristic I-V relation is nonlinear.

• Can’t we just use the equation, 𝑖𝐷 = 𝐼𝑆 𝑒

• Techniques:

•

•

•

•

𝐼𝑆 𝑒

𝑉𝐷

𝑛𝑉𝑇

𝑉𝑃𝑆 = 𝐼𝑆 𝑅 𝑒

• Notation:

• 𝐼𝐷 = 𝐼𝑆 𝑒

KVL

𝑉𝑃𝑆 = 𝐼𝐷 𝑅 + 𝑉𝐷

Iteration.

Graphical techniques. 𝐼𝐷 =

Piecewise linear modelling.

Computer analysis.

𝑉𝐷

𝑛𝑉𝑇

−1

.

𝑣𝐷

𝑛𝑉𝑇

−1

.

𝑉𝐷

𝑛𝑉𝑇

.

− 1 + 𝑉𝐷

Transcendental Equation

−1 ?

.

Iteration

Techniques:

Iteration.

Graphical techniques.

Piecewise linear modelling.

Computer analysis.

• Trial and Error

KVL

1. 𝑉𝑃𝑆 = 𝐼𝐷 𝑅 + 𝑉𝐷

2. 𝐼𝐷 = 𝐼𝑆 𝑒

𝑉𝐷

𝑛𝑉𝑇

3. 𝑉𝑃𝑆 = 𝐼𝑆 𝑅 𝑒

−1

Ideal Current-Voltage Relationship

.

𝑉𝐷

𝑛𝑉𝑇

− 1 + 𝑉𝐷

.

• We know 𝑉𝐷 is somewhere near 0.6 V.

• Guess values until LHS = RHS in Equation 3.

Example - Iteration

Determine the diode voltage for the circuit shown. Consider a diode with a given

reverse-saturation current of 𝐼𝑆 = 10−13 A.

KVL

• 𝑉𝑃𝑆 = 𝐼𝐷 𝑅 + 𝑉𝐷

• 𝐼𝐷 = 𝐼𝑆 𝑒

𝑉𝐷

𝑛𝑉𝑇

• 𝑉𝑃𝑆 = 𝐼𝑆 𝑅 𝑒

−1

Ideal Current-Voltage Relationship

.

𝑉𝐷

𝑛𝑉𝑇

.

− 1 + 𝑉𝐷

• 5 = (10−13 )(2000) 𝑒

𝑉𝐷

(1)(0.026)

.

− 1 + 𝑉𝐷

𝑹𝑯𝑺

• 𝑉𝐷 = 0.6 V → 𝑅𝐻𝑆 = 2.7 V

• 𝑉𝐷 = 0.65 V → 𝑅𝐻𝑆 = 15.1 V

• 𝑉𝐷 = 0.625 V → 𝑅𝐻𝑆 = 6.1 V

• 𝑉𝐷 = 0.619 V → 𝑅𝐻𝑆 = 4.99 V

• 𝐼𝐷 = 2.19 mA

Try Exercise Problem

1.8 on page 37

Load Lines

Techniques:

Iteration.

Graphical techniques.

Piecewise linear modelling.

Computer analysis.

KVL

• 𝑉𝑃𝑆 = 𝐼𝐷 𝑅 + 𝑉𝐷

• 𝐼𝐷 = 𝐼𝑆 𝑒

𝑉𝐷

𝑛𝑉𝑇

−1

Ideal Current-Voltage Relationship

.

• We have two expressions that we want to solve

simultaneously.

• The solution exists somewhere on this curve

• Find a curve for the circuit. Look at axes:

• 𝑉𝐷 vs. 𝐼𝐷 - solve for 𝐼𝐷

• 𝐼𝐷 =

𝑉𝑃𝑆

𝑅

𝑉𝐷

−

𝑅

This is called a load line

• Intersection is called the quiescent point (Q-point)

• Same answer as iteration technique!

• Problem with this approach?

Recap on the Diode I-V Characteristic

𝐼𝐷 = 𝐼𝑆 𝑒

𝑉𝐷

𝑛𝑉𝑇

−1

𝐼𝐷 = 𝐼𝑆 𝑒

Ideal Current-Voltage Relationship

.

Temperature

1

diode

I-V characteristics

−Ideal

1

Ideal

Current-Voltage

Relationship

𝑉𝐷

𝑛𝑉𝑇

.

3

Reverse Breakdown

Ideal representation

The diode circuit and symbol

Temperature

Reverse Breakdown

2

off

on

Techniques:

Iteration.

Graphical techniques.

Piecewise linear modelling.

Computer analysis.

Piecewise Linear Model

Ideal I-V characteristics

• Goal of the piecewise linear model:

• Amend the ideal diode representation to something more accurate.

• Piecewise linear – approximate using straight lines.

Slope =

1

𝑟𝑓

• Two lines are used in the piecewise linear approximation:

• Why only two?

• Reverse bias - off

• Forward bias - on

• Transition between on and off approximated with 𝑉𝛾

•

• 𝑉𝛾 is called the turn-on, or cut-in, voltage.

1

Slope of forward bias give by

𝑟𝑓

• 𝑟𝑓 is called the forward diode resistance.

𝑉𝛾

Reverse bias - off

Forward bias - on

Piecewise Linear Model

Ideal I-V characteristics

• Reverse bias - off

Slope =

1

𝑟𝑓

• 𝑉𝐷 < 𝑉𝛾

• Forward bias - on

• 𝑉𝐷 ≥ 𝑉𝛾

• 𝑉𝐷 = 𝐼𝐷 𝑟𝑓 + 𝑉𝛾

• 𝑉𝛾 stays constant in this approximation. It

cannot change!

• What if 𝑟𝑓 = 0 Ω ?

• Slope

𝑉𝛾

Reverse bias - off

Forward bias - on

Piecewise Linear Model - Example

Determine the diode voltage and current in the circuit shown in Figure

below, using a piecewise linear model. Also determine the power dissipated

in the diode.

Assume piecewise linear diode parameters of 𝑉𝛾 = 0.6 V and 𝑟𝑓 = 10 Ω.

Forward biased …

𝑰𝑫 =

𝑽𝑷𝑺 −𝑽𝜸

𝑹+𝒓𝒇

=

𝟓 −𝟎.𝟔

𝟐𝟎𝟎𝟎+𝟏𝟎

𝑰𝑫 =

𝑽𝑷𝑺 −𝑽𝜸

𝑹+𝒓𝒇

𝟓 −𝟎.𝟕

= 𝟐𝟎𝟎𝟎+𝟎 = 𝟐. 𝟏𝟓 𝐦𝐀

𝑽𝑫 = 𝑽𝜸 + 𝒓𝒇 ∙ 𝑰𝑫 = 𝟎. 𝟕 𝐕

𝑰𝑫 = 𝟐. 𝟏𝟗 𝐦𝐀

𝑽𝑫 = 𝑽𝜸 + 𝒓𝒇 ∙ 𝑰𝑫 = 𝟎. 𝟔 + 𝟏𝟎 ∙ 𝟐. 𝟏𝟗𝐱𝟏𝟎−𝟑 = 𝟎. 𝟔𝟐𝟐 𝐕

𝑷𝑫 = 𝑽𝑫 𝑰𝑫 = 𝟐. 𝟏𝟗𝐱𝟏𝟎−𝟑 ∙ 𝟎. 𝟔𝟐𝟐 = 𝟏. 𝟑𝟔 𝐦𝐖

NB – We often assume 𝑽𝜸 = 𝟎. 𝟕 𝐕 and 𝒓𝒇 = 𝟎 𝛀 for silicon pn

junction diodes. How can we do that?

Techniques:

Iteration.

Graphical techniques.

Piecewise linear modelling.

Computer analysis.

Piecewise Linear Model – Load Line

• Assume 𝑉𝐷 = 𝑉𝛾 = 0.7 V and 𝑟𝑓 = 0 Ω – simplicity.

• The simplified piecewise linear approximation is drawn.

• The solution exists somewhere on this line.

• Derive circuit load line:

• 𝑉𝑃𝑆 = 𝐼𝐷 𝑅 + 𝑉𝛾

KVL

• 5 = 2000 ∙ 𝐼𝐷 + 𝑉𝛾

• Draw the load line on the piecewise linear curve:

• Intersection point is the solution – called Q-point.

• Let’s change the controllable circuit parameters:

• A – 𝑉𝑃𝑆 = 5 V, 𝑅 = 2 kΩ

• B – 𝑉𝑃𝑆 = 5 V, 𝑅 = 4 kΩ

• C – 𝑉𝑃𝑆 = 2.5 V, 𝑅 = 2 kΩ

• D - 𝑉𝑃𝑆 = 2.5 V, 𝑅 = 4 kΩ

The Q-point is the DC operating point and is

controlled with the external circuit. We will do this in

depth when we ‘bias’ circuits.

Piecewise Linear Model – Load Line

• The diode is reverse biased. Why?

• Draw piecewise linear approximation for

the diode.

• Derive circuit load line:

• 𝑉𝑃𝑆 = 𝐼𝑃𝑆 𝑅 − 𝑉𝐷 = −𝐼𝐷 𝑅 − 𝑉𝐷

• 𝐼𝐷 = −

𝑉𝑃𝑆

𝑅

−

𝑉𝐷

𝑅

=−

5

2000

−

𝑉𝐷

2000

• Find x and y axis intersection point.

• Where is the Q-point?

• What does the Q-point tell us?

Techniques:

Iteration.

Graphical techniques.

Piecewise linear modelling.

Computer analysis.

Computer Analysis Example

Determine the diode current and voltage characteristics of the

circuit shown in Figure.

2

1

This is an example

VI 1 0 dc

R1 1 2 2000

D1 2 0 1N4007

* 1N4007 MCE General Purpose Diode

.MODEL 1N4007 D(IS=7.02767e-09 RS=0.0341512

+N=1.80803 EG=1.05743

+XTI=5 BV=1000 IBV=5e-08 CJO=1e-11

+VJ=0.7 M=0.5 FC=0.5 TT=1e-07

+KF=0 AF=1)

.dc VI 0 15 0.1

.control

run

plot v(2)

plot -i(VI)

.endc

.end

≈ 0.7 V

𝑉𝛾

Computer Analysis Example 2

Determine the diode voltage and current in the circuit shown

in Figure below.

Use the 1N4007 diode model.

This is an example

VPS 1 0 5

R1 1 2 2000

D1 2 0 1N4007

* 1N4007 MCE General Purpose Diode

.MODEL 1N4007 D(IS=7.02767e-09 RS=0.0341512

+N=1.80803 EG=1.05743

+XTI=5 BV=1000 IBV=5e-08 CJO=1e-11

+VJ=0.7 M=0.5 FC=0.5 TT=1e-07

+KF=0 AF=1)

.control

op

print v(2)

print -i(VPS)

.endc

.end

• So, 𝑉𝐷 = 0.5919 V and 𝐼𝐷 = 2.204 mA

• Piecewise linear using 𝑟𝑓

• 𝑉𝐷 = 0.622 V & 𝐼𝐷 = 2.190 mA

• Piecewise linear & load line

• 𝑉𝐷 = 0.7 V & 𝐼𝐷 = 2.150 mA

• Iteration

• 𝑉𝐷 = 0.619 V & 𝐼𝐷 = 2.190 mA

• Why is it different from our other

techniques?

1

2

0

In Conclusion

Electronics 245

Lecture 6

1.4 - AC Equivalent Analysis

1.4.1 – Sinusoidal Analysis

1.4.2 – Small-Signal equivalent Circuit

Current-Voltage Relationships

• Let’s first consider the DC I-V

relationship of the diode.

• Small AC signal, 𝑣𝑖 , superimposed on 𝑉𝑃𝑆

• The diode I-V relation now becomes:

• 𝑖𝐷 ≅ 𝐼𝑆 𝑒

• 𝑖𝐷 = 𝐼𝑆 𝑒

𝑉𝐷𝑄 + 𝑣𝑑

𝑣𝐷

𝑛𝑉𝑇

𝑉𝐷𝑄

.

− 1 = 𝐼𝑆 𝑒

∙ 𝑒

𝑉𝑇

𝑉𝑇

𝑣𝑑

𝑉𝑇

.

.

• If AC signal is small:

• 𝑒

𝑣𝑑

𝑉𝑇

≅1+

Add an AC source

𝑣𝑑

𝑉𝑇

* Definitions *

Current and Voltage both

𝒓𝒅 − small-signal incremental resistance or diffusion resistance.

constant w.r.t. - DC

𝒈𝒅 − small-signal incremental conductance or diffusion conductance.

Taylor series expansion

𝑉𝐷𝑄

• 𝐼𝐷𝑄 = 𝐼𝑆 𝑒

𝑉𝑇

• So,

• 𝑖𝐷 = 𝐼𝐷𝑄 1 +

• Finally,

• 𝒊𝑫 =

𝑰𝑫𝑸

• 𝑣𝑑 =

𝑉𝑇

𝑽𝑻

𝐼𝐷𝑄

𝑣𝑑

𝑉𝑇

= 𝐼𝐷𝑄 +

∙ 𝒗𝒅 = 𝒈𝒅 ∙ 𝒗𝒅

𝐼𝐷𝑄

𝑉𝑇

∙ 𝑣𝑑 = 𝐼𝐷𝑄 + 𝑖𝑑

𝐼𝐷𝑄

∙ 𝑖𝑑 = 𝑟𝑑 𝑖𝑑

𝑉𝐷𝑄

𝑉𝐷𝑄

Circuit Analysis

• To analyse this circuit, we split the problem.

• Steps:

• First analyse DC circuit.

• As we have done to this point.

• Second analyse AC circuit.

• For the AC circuit:

• 𝒗𝒅 =

𝑽𝑻

𝑰𝑫𝑸

∙ 𝒊𝒅 = 𝒓𝒅 𝒊𝒅

• Replace diode with its small-signal incremental

resistance, 𝒓𝒅 .

Summary:

Steps to solve:

1. Analyse DC

Get 𝐼𝐷𝑄 & 𝑉𝐷𝑄

2. Analyse AC

1

𝑉𝑇

𝑟𝑑 =

=

𝑔𝑑

𝐼𝐷𝑄

DC

AC

Circuit Analysis - Example

Find 𝑖𝐷 and 𝑣𝑂 in the circuit below. Assume circuit and diode parameters of

𝑉𝑃𝑆 = 5 V, 𝑅 = 5 kΩ, 𝑉𝛾 = 0.6 V, and 𝑣𝑖 = 0.1 sin𝜔𝑡 V.

DC

• First the DC analysis:

• 𝐼𝐷𝑄 =

𝑉𝑃𝑆 − 𝑉𝛾

𝑅

=

5 −0.6

5000

𝑉𝛾 = 0.6 V

= 880 μA

• 𝑉𝑜 = 𝐼𝐷𝑄 𝑅 = 880 μA 5000 = 4.4 V

• Then the AC analysis:

𝑉𝑇

𝐼𝐷𝑄

• 𝑖𝑑 =

𝑣𝑖

𝑟𝑑 +𝑅

=

26 mV

880 μA

=

= 29.5 Ω

0.1 sin𝜔𝑡

29.5+5

= 19.9 sin𝜔𝑡 μA

• 𝑣𝑜 = 𝑖𝑑 𝑅 = 99.5 sin𝜔𝑡 mV

• 𝑖𝐷 = 𝐼𝐷𝑄 + 𝑖𝑑 = 880 + 19.9 sin𝜔𝑡 μA

• 𝑣𝑂 = 𝑣𝑜 + 𝑉𝑜 = 4.4 + 0.0995 sin𝜔𝑡 V

AC

𝑣𝑖 = 0.1 sin𝜔𝑡 (V)

• 𝑟𝑑 =

𝑅 = 5kΩ

𝑉𝑃𝑆 = 5 V

𝑟𝑑 =?29.5 Ω

𝑅 = 5kΩ

Frequency Response

• Consider the carrier concentration under

steady-state for a forward-bias DC source.

• Charge separation is measured by capacitance.

• What happens under AC conditions?

• Voltage across the junction changes.

• Charge concentration changes with the

voltage:

• 𝐶𝑑 =

𝑑𝑄

𝑑𝑉𝐷

• 𝐶𝑑 - Diffusion capacitance

Steady-state minority carrier concentration.

Small-Signal Equivalent Circuit

• The small-signal equivalent circuit is derived from the

equation for admittance:

Complete circuit

• ∴Add in parallel.

• We have two representations:

• The complete circuit.

• The simplified circuit.

• 𝐶𝑑 - diffusion capacitance

• 𝐶𝑗 - junction capacitance

• 𝑟𝑑 - small-signal incremental resistance or diffusion resistance.

• 𝑟𝑠 - series resistance of the n and p regions

• Difference between the two?

• 𝐶𝑑 generally much larger than 𝐶𝑗 - neglected.

• 𝑟𝑠 is small – neglected.

Simplified circuit

In Conclusion

Electronics 245

Lecture 7

Semiconductor Theory – Chapter 1

1.5 - Other Diode Types

Diode Circuits – Chapter 2

2.1 - Rectifier Circuits

2.1.1 – Half-Wave Rectifier

Solar Cell

• Photons are converted to electrical energy.

• How?

• When a photon hits the cell, it is absorbed by the

semiconductor material (typically silicon).

• This only occurs if the photon energy is greater than the

bandgap energy.

• Otherwise, the photon will be reflected, or will pass through

the silicon.

• The absorbed photon passes energy to an electron

in the depletion region. An electron-hole pair is

formed.

• Electrons will flow through the load and a DC

current is measured.

http://cheap-photovoltaic-energy.blogspot.com/2012/07/photovoltaiccells-generating.html

Light-Emitting Diode (LED)

• Electrical energy → light energy.

• Similar characteristics to a pn junction diode.

• Still passes current one way.

• Fabricated using a very thin layer of heavilydoped semiconductor material.

• How does it work?

• When forward-baised, depletion region narrows.

Diffusion occurs.

• Electrons from the conduction band recombine with

holes in the valence band.

• This recombination produces energy.

• Holes are at a lower energy.

• Excess energy must be released.

• Direct bandgap semiconductors used.

• Photons are released. The spectral

wavelength depends on the material and

doping.

VectorStock.com/15452093

Schottky Barrier Diode

• Fabricated by joining a metal with a moderately

doped n-type semiconductor.

• Circuit symbol for the Schottky barrier diode.

• The I-V relation is similar to the pn junction.

• The same ideal diode equation can be used!

• Turn on voltage is lower for Schottky diode.

• Distinct differences to note:

• Current mechanism.

• Switching times.

• Reverse-saturation current.

Schottky Barrier Diode

The reverse saturation currents of a pn junction diode and a Schottky

diode are 𝐼𝑠 = 10−12 A and 10−8 A, respectively. Determine the forwardbias voltages required to produce 1 mA in each diode.

Pn Junction diode

𝐼𝐷 = 𝐼𝑆 𝑒

𝑉𝐷 = 𝑉𝑇 ln

𝑉𝐷

𝑉𝑇

.

𝐼𝐷

𝐼𝑆

= 0.026 ∙ ln

0.001

10−12

= 0.539 V

0.001

10−8

= 0.299 V

Schottky diode

𝑉𝐷 = 𝑉𝑇 ln

𝐼𝐷

𝐼𝑆

= 0.026 ∙ ln

A lower voltage is required across the diode for the same current

because of the larger reverse saturation current.

Schottky Barrier Diode

A pn junction diode and a Schottky diode both have forward-bias currents of

1.2 mA. The reverse-saturation current of the pn junction diode is 𝐼𝑠 = 4 × 10−15 A.

The difference in forward-bias voltages is 0.265 V. Determine the reverse-saturation

current of the Schottky diode.

For the pn junction diode, 𝐼𝐷 = 𝐼𝑆 𝑒

𝑉𝐷 ≅ 𝑉𝑇 ln

𝑉𝐷

𝑉𝑇

.

𝐼𝐷

𝐼𝑆

𝑉𝐷 = 0.026 ln

1.2 x 10−3

4 x 10−15

= 0.6871 V

The Schottky diode voltage will be smaller:

𝑉𝐷 = 0.6871 − 0.265 = 0.4221 V

𝐼𝐷 ≅ 𝐼𝑆 𝑒

𝐼𝑆 =

𝑉𝐷

𝑉𝑇

.

1.2 x 10−3

𝑒

0.4221

0.026

= 1.07 x 10−10 A

Zener Diode

• Designed to “break down” at low voltages.

• This is useful for certain applications.

• When a constant voltage is required in a circuit for a

wide range of current values.

• The breakdown voltage is given as a positive

value.

• 𝑉𝑍 = 𝐼𝑍 𝑟𝑍 + 𝑉𝑍0

• A large current is possible.

• The circuit must be designed to limit the current.

• The value of 𝑟𝑍 is typically in the range of a

few ohms or tens of ohms. This gives a steep

slope.

Zener Diode – Design Example

Consider the circuit shown. Assume that the Zener diode breakdown

voltage is 𝑉𝑍 = 5.6 V and the Zener resistance is 𝑟𝑍 = 0 Ω. The current in

the diode is to be limited to 3 mA.

We can determine the voltage across 𝑅 and we know the

current:

𝑅=

𝑉𝑃𝑆 − 𝑉𝑍

𝐼

=

10 − 5.6

0.003

= 1.47 kΩ

𝑃𝑍 = 𝐼𝑍 𝑉𝑍 = 3 5.6 = 16.8 mW

The zener diode must be able to dissipate this power

without being damaged. This is an important consideration

in design problems.

1

3

2

Rectifier Circuits

2.1

Converting AC to DC

1

2

3

4

4

Half-Wave Rectifier

• Determine the transfer characteristics.

• What are transfer characteristics?

• Transfer function, i.e. mapping input to

output. Do this graphically.

• Find transition point - consider node 1.

• If 𝑉(1) = 0 V, the diode, 𝐷1 , is off.

• For 𝐷1 to switch on, 𝑣𝑆 ≥ 𝑉𝛾 .

• If 𝑣𝑆 ≥ 𝑉𝛾 , then 𝑣𝑂 = 𝑣𝑆 − 𝑉𝛾 .

• Draw the transfer characteristics.

Summary:

• 𝑣𝑆 < 𝑉𝛾

• Diode 𝐷1 is off

• 𝑣𝑂 = 0 V

• 𝑣𝑆 ≥ 𝑉𝛾

• Diode 𝐷1 is on

• 𝑣𝑂 = 𝑣𝑆 − 𝑉𝛾

1

𝐷1

+ 𝑉𝛾 −

off

on

Half-Wave Rectifier

• Analyse the circuit.

•

𝑣𝐼

𝑣𝑆

=

𝑁1

𝑁2

1

𝐷1

𝑉𝛾𝐷 −

+ 𝑉

Use transformer turn ratio.

• From the previous slide…

• Whenever 𝑣𝑆 ≥ 𝑉𝛾 , diode 𝐷1 is on.

on

off

• 𝑣𝑂 = 𝑣𝑆 − 𝑉𝛾

• Whenever 𝑣𝑆 < 𝑉𝛾 , diode 𝐷1 is off.

• 𝑣𝑂 = 0 V

• 𝑉𝐷 = 𝑣𝑆

Why?

on

off

on

on

off

on

𝑉𝛾

Peak Inverse

Voltage

Half-Wave Rectifier - Example

Consider the circuit shown. Assume 𝑉𝐵 = 12 V , 𝑅 = 100 Ω , and 𝑉𝛾 = 0.6 V . Also

assume 𝑣𝑠 𝑡 = 24sin𝜔𝑡 V . Determine the peak diode current, maximum reversebias diode voltage, and the fraction of the cycle over which the diode is

conducting.

Peak diode current:

𝑖𝐷(𝑝𝑒𝑎𝑘) =

𝑉𝑆 − 𝑉𝐵 − 𝑉𝛾

𝑅

=

Node 𝑉𝑋 = 𝑉𝐵 + 𝑉𝛾

24 −12 −0.6

100

= 114 mA

Maximum reverse bias voltage:

𝑣𝑅(𝑚𝑎𝑥) = 𝑉𝑆 + 𝑉𝐵 = 24 + 12 = 36 V

Diode conduction cycle:

𝑣𝐼 = 24sin𝜔𝑡1 = 12.6

𝜔𝑡1 = 𝑠𝑖𝑛−1

12.6

24

= 31.7°

𝜔𝑡2 = 180 − 31.7 = 148.3°

𝑃𝑒𝑟𝑐𝑒𝑛𝑡𝑎𝑔𝑒 𝑡𝑖𝑚𝑒 =

V𝑋 + V𝛾 -

148.3 −31.7

360

x 100 = 32.4 %

𝑉𝑋 = 12.6 V - in forward bias

Diode on when 𝑉𝑆 ≥ 𝑉𝑋

−

𝑉𝑆

+

V𝐵

In Conclusion

Electronics 245

Lecture 8

Diode Circuits – Chapter 2

2 – Rectifier Circuits

Recap of Half-Wave Rectification

2.1.2 Full-Wave Rectification

Half-Wave Rectifier

𝑣𝑠 < 𝑉𝛾 → 𝑣𝑜 = 0 V

off

PIV

Peak Inverse Voltage (PIV)

𝑣𝑜 = 𝑣𝑠 − 𝑉𝛾

on

Center-Tapped Full-Wave Rectifier

- +

• Rectify the full wave – even the negative half cycle.

• 𝑣𝑠 is drawn from a center-tapped secondary winding

of a transformer.

• 𝑣𝐼 positive half cycle:

•

•

•

•

𝑣𝑠 is in its positive half cycle.

𝐷1 - forward bias & 𝐷2 - reverse bias.

What does the equivalent circuit look like?

𝑣𝑂 = 𝑣𝑠 − 𝑉𝛾 .

•

•

•

•

•

𝑣𝑠 is in its negative half cycle.

𝐷1 - reverse bias & 𝐷2 - forward bias.

What does the equivalent circuit look like?

𝑣𝑠 + 𝑉𝛾 + 𝑣𝑂 = 0.

𝑣𝑂 = −𝑣𝑠 − 𝑉𝛾 .

Remember 𝑣𝑠 is in the –’ve half cycle!

+ -

+

+ -

• 𝑣𝐼 negative half cycle:

• Draw the transfer characteristics.

Rectified output voltage, 𝑣𝑂 .

Full-Wave Bridge Rectifier

• When 𝑣𝑠 is positive:

•

•

•

•

Diodes

Diodes

KVL →

𝑣𝑂 = 𝑣𝑠

𝐷1 and 𝐷2 are on – forward bias.

𝐷3 and 𝐷4 are off – reverse bias.

𝑣𝑠 = 2𝑉𝛾 + 𝑣𝑂

− 2𝑉𝛾

•

•

•

•

Diodes 𝐷3 and 𝐷4 are on – forward bias.

Diodes 𝐷1 and 𝐷2 are off – reverse bias.

KVL → 𝑣𝑠 + 2𝑉𝛾 + 𝑣𝑂 = 0

𝑣𝑂 = −𝑣𝑠 − 2𝑉𝛾

Remember 𝑣𝑠 is in the –’ve half cycle!

• When 𝑣𝑠 is negative:

x

x

x

x

Full-Wave Bridge Rectifier

Negative Rectification

• Same circuit, but diode polarities are

inverted.

• Apply the same logic as used for the positive

rectification circuit.

• When 𝑣𝑠 is positive:

•

•

•

•

Diodes 𝐷3 and 𝐷4 are on – forward bias.

Diodes 𝐷1 and 𝐷2 are off – reverse bias.

KVL → −𝑣𝑠 + 2𝑉𝛾 − 𝑣𝑂 = 0

𝑣𝑂 = −𝑣𝑠 + 2𝑉𝛾

•

•

•

•

Diodes 𝐷1 and 𝐷2 are on – forward bias.

Diodes 𝐷3 and 𝐷4 are off – reverse bias.

KVL → 𝑣𝑠 + 2𝑉𝛾 − 𝑣𝑂 = 0

𝑣𝑂 = 𝑣𝑠 + 2𝑉𝛾

• When 𝑣𝑠 is negative:

Full-Wave Rectifier Example

Compare voltages and the transformer turns ratio in two full-wave rectifier circuits.

Consider the rectifier circuits shown in Circuit 1 and Circuit 2 below. Assume the input

voltage is from a 120 V(rms), 60 Hz ac source. The desired peak output voltage, 𝑣𝑂 , is 9 V,

and the diode cut-in voltage is assumed to be 𝑉𝛾 = 0.7 V.

𝑣𝑠(𝑚𝑎𝑥) = 𝑣𝑂(𝑚𝑎𝑥) + 𝑉𝛾 = 9 + 0.7 = 9.7 V

9.7

2

𝑣𝑠(𝑟𝑚𝑠) =

𝑁1

𝑁2

=

120

6.86

= 6.86 V

𝑃𝐼𝑉 = 𝑣𝑅(𝑚𝑎𝑥) = 2𝑣𝑠(𝑚𝑎𝑥) − 𝑉𝛾

= 2 9.7 − 0.7 = 18.7 V

≅ 17.5

Rectifier Circuit 1

𝑣𝑠(𝑚𝑎𝑥) = 𝑣𝑂(𝑚𝑎𝑥) + 2𝑉𝛾 = 9 + 2 0.7 = 10.4 V

𝑣𝑠(𝑟𝑚𝑠) =

𝑁1

𝑁2

Rectifier Circuit 2

=

120

7.35

10.4

2

= 7.35 V

𝑃𝐼𝑉 = 𝑣𝑅(𝑚𝑎𝑥) = 𝑣𝑠(𝑚𝑎𝑥) − 𝑉𝛾

= 10.4 − 0.7 = 9.7 V

≅ 16.3

What conclusions can we draw from this example?

Exercise Problem 2.2(a)

Consider the bridge circuit shown with an input voltage 𝑣𝑆 = 𝑉𝑀 sin𝜔𝑡 . Assume a diode

cut-in voltage of 𝑉𝛾 = 0.7 V. Determine the fraction (percent) of time that the diode 𝐷1

is conducting for peak sinusoidal voltages of 𝑉𝑀 = 12 V.

Consider only one cycle. Why?

When is 𝐷1 on?

𝑣𝑂 = 𝑣𝑆 − 2𝑉𝛾

12 sin𝜔𝑡 − 2 0.7 = 0

𝜔𝑡1 = 𝑠𝑖𝑛−1

1.4

12

= 6.7°

By symmetry, 𝜔𝑡2 = 180 − 6.7 = 173.3°

% 𝑡𝑖𝑚𝑒 =

173.3 −6.7

360

𝑫𝟏 on 𝑫𝟏 off

x 100 = 46.3 %

𝜔𝑡1

𝜔𝑡2

In Conclusion

Electronics 245

Lecture 9

Diode Circuits – Chapter 2

2.1 – Rectifier Circuits

2.1.3 – Rectifier Filters

2.1.4 – Detectors

2.1.5 – Voltage Doublers

Rectifier with an RC Filter

• Describe using the half-wave rectifier.

• Add a capacitor in parallel with 𝑅.

•

•

•

•

•

•

Capacitor charges with 𝑣𝑆 (𝑟𝑓 𝐶 is small).

Diode switches off near peak (𝑅𝐶 is large).

Capacitor begins to discharge.

Capacitor discharge rate (𝑒 −𝑡Τ𝜏 ).

Steady-state output voltage.

When does the diode switch off?

• Output voltage of full-wave rectifier.

Time constants NB!

full-wave rectifier

half-wave rectifier

Ripple Voltage – Half-Wave Rectifier

Output voltage can be determined when the diode is

off – discharge of capacitor with 𝑒 −𝑡Τ𝜏 from max.

𝑣𝑂 𝑡 = 𝑉𝑀 𝑒 −𝑡

𝑉𝐿 = 𝑉𝑀 𝑒 −𝑇

′ Τ𝜏

= 𝑉𝑀 𝑒 −𝑡

′ Τ𝑅𝐶

′ Τ𝑅𝐶

𝑉𝑟 = 𝑉𝑀 − 𝑉𝐿 = 𝑉𝑀 1 − 𝑒 −𝑇

′ Τ𝑅𝐶

𝑇 ′ ≪ 𝑅𝐶:

𝑒 −𝑇

′ Τ𝑅𝐶

≅ 1 − 𝑇 ′ Τ𝑅𝐶

𝑉𝑟 = 𝑉𝑀 1 − (1 −

𝑇 ′ Τ𝑅𝐶)

𝑇 ′ ≅ 𝑇𝑝 if 𝑉𝑟 is small

𝑉𝑟 ≅ 𝑉𝑀

𝑓=

𝑉𝑟 =

1

𝑇𝑝

𝑉𝑀

𝑓𝑅𝐶

𝑇𝑝

𝑅𝐶

=

𝑇′

𝑉𝑀

𝑅𝐶

Neglecting 𝑽𝜸

Ripple Voltage - Exercise Problem

Assume the input signal to a rectifier circuit has a peak value of 𝑉𝑀 = 12 V and is at a

frequency of 60 Hz. Assume the output load resistance is 𝑅 = 2 kΩ and the ripple voltage is to

be limited to 𝑉𝑟 = 0.4 V. Determine the capacitance required to yield this specification for a

(a) half-wave rectifier and (b) full-wave rectifier.

a) 𝑉𝑟 =

𝐶=

𝑉𝑀

𝑓𝑅𝐶

𝑉𝑀

𝑓𝑅𝑉𝑟

𝐶 =

b) 𝑉𝑟 =

𝐶=

𝐶 =

(12)

(60)(2000)(0.4)

Back to the derivation:

𝑉𝑟 ≅ 𝑉𝑀

= 250 𝜇𝐹

𝑉𝑟 =

𝑉𝑀

2𝑓𝑅𝐶

𝑉𝑀

2𝑓𝑅𝑉𝑟

(12)

2(60)(2000)(0.4)

𝑓=

𝑇𝑝

𝑅𝐶

1

2𝑇𝑝

𝑉𝑀

2𝑓𝑅𝐶

𝑓

= 125 𝜇𝐹

Rectifier Design – Exercise Problem

The input voltage to the half-wave rectifier below is 𝑣𝑆 = 75 sin[2𝜋(60)𝑡] V . Assume a

diode cut-in voltage of 𝑉𝛾 = 0. The ripple voltage is to be no more than 𝑉𝑟 = 4 V. If the

filter capacitor is 50 μF, determine the minimum load resistance that can be connected

to the output.

Half-wave rectifier:

𝑉𝑟 =

𝑅=

𝑅=

𝑉𝑀

𝑓𝑅𝐶

𝑉𝑀

𝑓𝑉𝑟 𝐶

75

(60)(4)(50 x 10−6 )

𝑅 = 6.25 kΩ

NB: Work through design example 2.4 in your text book.

Rectifier Filter - Example

The circuit shown below is used to rectify a sinusoidal input signal with a peak voltage

of 120 V and a frequency of 60 Hz . If the output voltage cannot drop below 100 V ,

determine the required value of the capacitance 𝐶. The transformer has a turns ratio of

𝑁1 ∶ 𝑁2 = 1 ∶ 1 , where 𝑁2 is the number of turns on each of the secondary windings.

Assume the diode cut-in voltage is 0.7 V and the output resistance is 2.5 kΩ.

𝑣𝐼 = 120 sin 2𝜋60𝑡 V

𝑉𝛾 = 0.7 V

This is a full-wave rectifier.

𝑣𝑆 = 𝑣𝐼

𝑉𝑀 = 120 − 0.7 = 119.3 V

𝑉𝐿 = 100 V

𝑉𝑟 = 119.3 − 100 = 19.3 V

𝐶=

𝑉𝑀

2𝑓𝑅𝑉𝑟

𝐶=

119.3

2(60)(2500)(19.3)

𝐶 = 20.6 μF

Diode Conduction Time & Current

• Diode conducts for a brief period near the peak of the

sinusoidal input signal.

• The capacitor current during charging is approximately

triangular.

• Equations of importance for the full-wave and half-wave

rectifier:

𝑖𝐷𝑝𝑒𝑎𝑘 =

𝑖𝐷𝑎𝑣𝑔 =

𝑽𝑴

𝑹

𝟏+ 𝝅

𝟐𝑽𝑴

𝑽𝒓

𝑽𝑴

𝑹

𝟏 + 𝟐𝝅

𝟐𝑽𝑴

𝑽𝒓

𝟏

𝝅

𝟏

𝟐𝝅

𝟐𝑽𝒓

𝑽𝑴

∙

𝟐𝑽𝒓

𝑽𝑴

𝑽𝑴

𝑹

∙

𝑽𝑴

𝑹

𝟏+

𝝅

𝟐

𝟏+𝝅

𝟐𝑽𝑴

𝑽𝒓

𝟐𝑽𝑴

𝑽𝒓

NB: Work through design example 2.4 in your text book.

𝑑𝑣𝑂 𝑣𝑂

𝑖𝐷 = 𝐶

+

𝑑𝑡

𝑅

Detectors

•

•

•

•

•

An early application of semiconductor diodes.

What is amplitude modulation?

What is demodulation?

Why would you modulate/demodulate a signal?

How does the circuit work?

Voltage Doubler

• A class of voltage multiplier circuits.

• What are voltage multipliers used for – typical

applications?

• This circuit is very similar the full-wave rectifier.

• How does it work?

• Negative input cycle.

• Positive input cycle.

• Same ripple as rectifier circuits.

Negative input cycle.

1

1

2

Positive input cycle.

2

In Conclusion

Electronics 245

Lecture 10

Diode Circuits – Chapter 2

2.2 Zener Diode Circuits

2.2.1 Ideal Voltage Reference

2.2.2 Zener Resistance and Percent Regulation

2.3 Clipper and Clamper Circuits

2.3.1 Clippers

2

1

Zener Diode Circuits

2.2

Regulator Circuits

1

2

3

3

Ideal Voltage Reference Circuit

•

•

•

Determine the input resistance, 𝑅𝑖 :

𝑉𝑃𝑆 − 𝑉𝑍

𝐼𝐼

𝑉𝑃𝑆 − 𝑉𝑍

.

𝐼𝑍 + 𝐼𝐿

Assumption – ideal zener diode, i.e. 𝑟𝑍 = 0 Ω.

•

𝑅𝑖 =

•

But we want to design for a variable range…

•

𝐼𝑍 =

=

Solve above equation for 𝐼𝑍 :

𝑉𝑃𝑆 − 𝑉𝑍

𝑅𝑖

− 𝐼𝐿 .

Purpose of this circuit?

Extents of variation:

1. 𝐼𝑍

𝑚𝑖𝑛

when 𝑰𝑳(𝒎𝒂𝒙) , and 𝑽𝑷𝑺(𝒎𝒊𝒏)

2. 𝐼𝑍(𝑚𝑎𝑥) when 𝑰𝑳(𝒎𝒊𝒏) , and 𝑽𝑷𝑺(𝒎𝒂𝒙)

•

Insert these expressions into the equation for 𝑅𝑖 and solve:

•

•

𝑹𝒊 =

𝑽𝑷𝑺(𝒎𝒊𝒏) − 𝑽𝒁

𝑰𝒁(𝒎𝒊𝒏) + 𝑰𝑳(𝒎𝒂𝒙)

and

𝑹𝒊 =

𝑽𝑷𝑺(𝒎𝒂𝒙) − 𝑽𝒁

𝑰𝒁(𝒎𝒂𝒙) + 𝑰𝑳(𝒎𝒊𝒏)

solve

𝑽𝑷𝑺(𝒎𝒊𝒏) − 𝑽𝒁 ∙ 𝑰𝒁(𝒎𝒂𝒙) + 𝑰𝑳(𝒎𝒊𝒏) = 𝑽𝑷𝑺(𝒎𝒂𝒙) − 𝑽𝒁 ∙ 𝑰𝒁(𝒎𝒊𝒏) + 𝑰𝑳(𝒎𝒂𝒙)

•

We know range of input voltage and of the output load current (by design).

•

𝐼𝑍(𝑚𝑖𝑛) and 𝐼𝑍(𝑚𝑎𝑥) are then the only two unknowns!

•

Design choice → 𝐼𝑍(𝑚𝑖𝑛) = 0.1𝐼𝑍(𝑚𝑎𝑥) . Could select different limit…

•

Solve:

•

𝐼𝑍(𝑚𝑎𝑥) =

𝐼𝐿(𝑚𝑎𝑥) ∙ 𝑉𝑃𝑆(𝑚𝑎𝑥) − 𝑉𝑍 −𝐼𝐿(𝑚𝑖𝑛) ∙ 𝑉𝑃𝑆(𝑚𝑖𝑛) − 𝑉𝑍

𝑉𝑃𝑆(𝑚𝑖𝑛) −0.9𝑉𝑍 −0.1𝑉𝑃𝑆(𝑚𝑎𝑥)

Example - Ideal Voltage Reference Circuit

Design a voltage regulator using the circuit shown. The voltage regulator is to power

a car radio at 𝑉𝐿 = 9 V from an automobile battery whose voltage may vary between

11 and 13.6 V . The current in the radio will vary between 0 (off ) to 100 mA (full

volume).

𝐼𝑍(𝑚𝑎𝑥) =

𝐼𝑍(𝑚𝑎𝑥) =

𝐼𝐿(𝑚𝑎𝑥) ∙ 𝑉𝑃𝑆(𝑚𝑎𝑥) − 𝑉𝑍 −𝐼𝐿(𝑚𝑖𝑛) ∙ 𝑉𝑃𝑆(𝑚𝑖𝑛) − 𝑉𝑍

𝑉𝑃𝑆(𝑚𝑖𝑛) −0.9𝑉𝑍 −0.1𝑉𝑃𝑆(𝑚𝑎𝑥)

0.1 ∙ 13.6 − 9 − 0∙ 11 − 9

11 − 0.9(9) −0.1(13.6)

≅ 300 mA

𝑃𝑍(𝑚𝑎𝑥) = 𝐼𝑍(𝑚𝑎𝑥) ∙ 𝑉𝑍 = 300 9 = 2.7 W

𝑅𝑖 =

𝑉𝑃𝑆(𝑚𝑎𝑥) − 𝑉𝑍

𝐼𝑍(𝑚𝑎𝑥) + 𝐼𝐿(𝑚𝑖𝑛)

𝑃𝑅𝑖 =

𝑉𝑃𝑆(𝑚𝑎𝑥) − 𝑉𝑍

𝐼𝑍(𝑚𝑖𝑛) =

=

2

𝑅𝑖

𝑉𝑃𝑆(𝑚𝑖𝑛) − 𝑉𝑍

𝑅𝑖

13.6 − 9

0.3 + 0

=

= 15.3 Ω

13.6 − 9 2

15.3

− 𝐼𝐿(𝑚𝑎𝑥) =

= 1.4 W

11 − 9

15.3

− 0.1 = 30.7 mA

Observations:

•

𝐼𝑍(𝑚𝑖𝑛) is approximately 10 % of 𝐼𝑍(𝑚𝑎𝑥) as specified by the design equations.

•

Zener diode and resistor need to be capable of handling the min power

ratings.

Analyse Variation using Load Lines

• Consider the previous example. Where are the Q-points on

the breakdown curve?

• Get the circuit load line i.t.o. 𝑉𝑍 and 𝐼𝑍 :

•

𝑣𝑃𝑆 − 𝑉𝑍

𝑅𝑖

= 𝐼𝑍 +

• 𝑉𝑍 = 𝑣𝑃𝑆

𝑉𝑍

𝑅𝐿

𝑅𝐿

𝑅𝑖 + 𝑅𝐿

− 𝐼𝑍

𝑅𝑖 𝑅𝐿

𝑅𝑖 + 𝑅𝐿

Load Line Equation

• What are the extents of the circuit variables?

• 𝐼𝐿 = 0 → 100 mA, so 𝑅𝐿 = ∞ → 90 Ω

• 𝑣𝑃𝑆 = 11 → 13.6 V & 𝑅𝑖 = 15 Ω

Why?

• A: 𝑣𝑃𝑆 = 11 V, 𝑅𝐿 = ∞, 𝑉𝑍 = 11 − 𝐼𝑍 (15)

• B: 𝑣𝑃𝑆 = 11 V, 𝑅𝐿 = 90 Ω, 𝑉𝑍 = 9.43 − 𝐼𝑍 (12.9)

• C: 𝑣𝑃𝑆 = 13.6 V, 𝑅𝐿 = ∞, 𝑉𝑍 = 13.6 − 𝐼𝑍 (15)

• D: 𝑣𝑃𝑆 = 13.6 V, 𝑅𝐿 = 90 Ω, 𝑉𝑍 = 11.7 − 𝐼𝑍 (12.9)

• What if we increased the resistance?

• E: 𝑅𝑖 = 25 Ω, 𝑣𝑃𝑆 = 11 V, 𝑅𝐿 = 90 Ω, 𝑉𝑍 = 8.61 − 𝐼𝑍 (19.6)

{

Resistance and Percentage Regulation

•

•

•

•

For the ideal voltage reference circuit, we assumed

an ideal zener diode, 𝑟𝑍 = 0 Ω.

Here we inspect the voltage fluctuation for a nonzero slope, 𝑟𝑍 > 0 Ω.

For the non-ideal case, then, we model 𝑟𝑍 . Now 𝑉𝐿

changes with 𝐼𝑍 .

Two figures of merit are used to assess how good

the voltage regulator is.

Calculated with the load disconnected!

•

•

•

𝑆𝑜𝑢𝑟𝑐𝑒 𝑅𝑒𝑔𝑢𝑙𝑎𝑡𝑖𝑜𝑛 =

𝐿𝑜𝑎𝑑 𝑅𝑒𝑔𝑢𝑙𝑎𝑡𝑖𝑜𝑛 =

∆𝑣𝐿

∆𝑣𝑃𝑆

x 100 %

𝑣𝐿𝑛𝑜 𝑙𝑜𝑎𝑑 − 𝑣𝐿𝑓𝑢𝑙𝑙 𝑙𝑜𝑎𝑑

𝑣𝐿𝑓𝑢𝑙𝑙 𝑙𝑜𝑎𝑑

x 100 %

𝑽𝒁 = 𝑽𝒁𝟎 + 𝑰𝒁 𝒓𝒁

∆𝑣𝐿 - change in output voltage.

∆𝑣𝑃𝑆 - change in input voltage.

𝑣𝐿𝑛𝑜 𝑙𝑜𝑎𝑑 - output voltage for zero load current.

𝑣𝐿𝑓𝑢𝑙𝑙 𝑙𝑜𝑎𝑑 - output voltage for max load current.

Use 𝑣𝑃𝑆(𝑚𝑎𝑥) for both! See example on next slide.

The circuit approaches an ideal voltage regulator as

these two metrics approach zero.

Example - Resistance and Percentage Regulation

Determine the source regulation and load regulation of a voltage regulator circuit. Consider the

circuit below and assume a Zener resistance of 𝑟𝑍 = 2 Ω, and 𝑅𝑖 = 15.3 Ω. The current in the radio

will vary between 0 (off ) to 100 mA (full volume).

𝑽𝒁 = 𝑽𝒁𝟎 + 𝑰𝒁 𝒓𝒁

𝟏𝟏 ≤ 𝑉𝑃𝑆 ≤ 𝟏𝟑. 𝟔 𝐕, 𝑉𝑍𝑂 = 9 V

𝑆𝑜𝑢𝑟𝑐𝑒 𝑅𝑒𝑔𝑢𝑙𝑎𝑡𝑖𝑜𝑛 =

∆𝑣𝐿

∆𝑣𝑃𝑆

x 100 %

Calculated with the load disconnected!

Get ∆𝑣𝐿 from 𝐼𝑍 for 𝑽𝑷𝑺(𝒎𝒂𝒙) and 𝑽𝑷𝑺(𝒎𝒊𝒏) .

+

𝑽𝒁𝟎

−

𝟏𝟑.𝟔 − 9

= 265.9 mA

𝑣𝐿(𝑚𝑎𝑥) = 9 + 2 0.2659 = 9.532 V

15.3+2

𝟏𝟏 − 9

𝐼𝑍 =

= 115.6 mA

𝑣𝐿(𝑚𝑖𝑛) = 9 + 2 0.1156 = 9.231 V

15.3+2

9.532 −9.231

𝑆𝑜𝑢𝑟𝑐𝑒 𝑅𝑒𝑔𝑢𝑙𝑎𝑡𝑖𝑜𝑛 =

x 100 % = 11.6 %.

13.6 −11

𝐼𝑍 =

𝐿𝑜𝑎𝑑 𝑅𝑒𝑔𝑢𝑙𝑎𝑡𝑖𝑜𝑛 =

𝑣𝐿𝑛𝑜 𝑙𝑜𝑎𝑑 − 𝑣𝐿𝑓𝑢𝑙𝑙 𝑙𝑜𝑎𝑑

𝑣𝐿𝑓𝑢𝑙𝑙 𝑙𝑜𝑎𝑑

x 100 %

Use 𝑣𝑃𝑆(𝑚𝑎𝑥) for both!

𝑣𝐿𝑛𝑜 𝑙𝑜𝑎𝑑 → 𝐼𝐿 = 0

𝐼𝑍 =

𝟏𝟑.𝟔 − 9

15.3+2

= 265.9 mA

𝑣𝐿𝑛𝑜 𝑙𝑜𝑎𝑑 = 9 + 2 0.2659 = 9.5324 V

𝑣𝐿𝑓𝑢𝑙𝑙 𝑙𝑜𝑎𝑑 → 𝐼𝐿 = 100 mA

𝐼𝑍 =

𝟏𝟑.𝟔 −(9+𝐼𝑍 2 )

15.3

− 0.1 = 177.5 mA

𝐿𝑜𝑎𝑑 𝑅𝑒𝑔𝑢𝑙𝑎𝑡𝑖𝑜𝑛 =

9.5324 −9.355

9.355

𝑣𝐿𝑓𝑢𝑙𝑙 𝑙𝑜𝑎𝑑 = 9 + 2 0.1775 = 9.355 V

x 100 % = 1.89 %

Observations?

Clipper and Clamper Circuits

2.3

Wave-shaping Circuits

Clipper Circuits

•

•

•

•

•

•

+

𝑉𝛾

−

𝑉𝑥 < 𝑉𝐵 + 𝑉𝛾

The current is zero and 𝑣𝐼 = 𝑉𝑥 = 𝑣𝑂 .

• So, the diode is off for 𝑣𝐼 < 𝑉𝐵 + 𝑉𝛾 .

• 𝑣𝑂 = 𝑣𝐼 .

The diode is on:

•

•

𝑉𝑥

Also called limiter circuits.

• Used to “limit” or “clip” the signal at specified levels.

Let’s consider the single diode clipper circuit.

The diode is off:

𝑣𝐼 ≥ 𝑉𝐵 + 𝑉𝛾

• 𝑣𝑂 = 𝑉𝐵 + 𝑉𝛾 irrespective of 𝑣𝐼 .

What does 𝑣𝑂 look like?

off

on

off

Clipper Circuits

• Let’s consider the double-limiter circuit.

• Also called a parallel-based clipper circuit.

• 𝐷1 on and off as in previous slide.

• Looking at branch for 𝐷2 - reverse of 𝐷1 .

• Note – bottom node is reference ground!

• Analyse this branch in another way:

• What is the voltage, 𝑉𝑥 , at which the diode,

𝐷2 , goes from the off state to the on state?

• 𝑉𝑥 = −𝑉𝐵2 − 𝑉𝛾 .

• If greater than this voltage, 𝐷2 is off.

• What does 𝑣𝑂 look like?

• Transfer characteristics?

𝑉𝑥

𝑉𝑥

+

−

𝑉𝛾

𝑉𝛾

−

+

Clipper Circuits – Zener Diodes

•

•

•

Let’s consider the double-limiter circuit again…

• But replace the DC batteries with zener diodes.

What would the transfer characteristics look like?

Exactly the same if 𝑉𝑍1 = 𝑉𝐵1 and 𝑉𝑍2 = 𝑉𝐵2 !

Note 𝑽𝒁 polarity

In reverse breakdown!

Clipper Circuits – Another Variation

•

•

•

A negative DC offset is applied → 𝑉𝐵 .

This shifts the DC operating point down by 𝑉𝐵 !

Transition point?

•

•

•

•

𝑉𝑥

−

𝑉𝛾

𝑉𝑥 = −𝑉𝛾 = 𝟎

+

The diode is off when:

•

𝑉𝑥 > −𝑉𝛾 = 𝟎

•

𝑣𝐼 − 𝑉𝐵 > −𝑉𝛾 = 𝟎

• 𝑣𝑂 = 𝑣𝐼 − 𝑉𝐵

The diode is on when:

•

𝑉𝑥 = −𝑉𝛾 = 𝟎

•

𝑣𝐼 − 𝑉𝐵 ≤ −𝑉𝛾 = 𝟎

•

𝑣𝑂 = −𝑉𝛾 = 𝟎

What does 𝑣𝑂 look like?

•

Note 𝑉𝛾 = 0

off

on

off

on

Parallel-Based Clipper Design Example

Design a parallel-based clipper that will yield the voltage transfer function shown

below. Assume diode cut-in voltages of 𝑉𝛾 = 0.7 V.

•

What does the circuit look like?

•

For 𝑣𝐼 > 2.5 V

•

•

•

•

𝑣𝑂 increases with increasing 𝑣𝐼 .

•

We need a resistor in this branch.

•

𝑉𝑥1 = 𝑉1 + 𝑉𝛾 = 2.5 V

•

DC source, 𝑉1 = 1.8 V

For −5 ≤ 𝑣𝐼 ≤ 2.5 V

•

Both parallel diodes are off

•

𝑣𝑂 = 𝑣𝐼

Work through example 2.7

For 𝑣𝐼 < −5 V

•

𝑣𝑂 is constant.

•

𝑉𝑥2 = −𝑉2 − 𝑉𝛾 = −5 V

•

DC source, 𝑉2 = 4.3 V

𝑉𝑥1

To determine the resistor values, use the gradient when 𝑣𝐼 > 2.5 V

•

∆𝑣𝑜

∆𝑣𝐼

•

𝑅2

𝑅1 +𝑅2

=

1

3

=

Δ𝑣𝑂 = Δ𝑣𝐼

1

3

𝑅2

𝑅1 + 𝑅2

∴ 𝑅1 = 2𝑅2

𝑉𝑥2

In Conclusion

Electronics 245

Lecture 11

Diode Circuits – Chapter 2

2.3 Clipper and Clamper Circuits

2.3.2 Clampers

2.4 Multiple Diode Circuits

2.4.1 Example Diode Circuits

Clamper Circuits

• Clamper circuits shift a voltage waveform by a DC level.

• Consider the clamper circuit, and the input voltage, 𝑣𝐼 .

• Assuming that 𝑣𝐶 𝑡 = 0 = 0 V, 𝑟𝑓 = 0 Ω, and 𝑉𝛾 = 0 V.

• 𝑡 ≤ 𝑇Τ4:

• Diode conducts, so 𝑣𝑂 = 𝑣𝛾 = 0 V.

• Voltage drop over capacitor.

• Charges with 𝑣𝐼 to 𝑣𝐶 = 𝑣𝑀 :

• 𝑡 > 𝑇Τ4 (steady-state is reached):

• Diode becomes reverse biased and switches off – open circuit.

• The voltage 𝑣𝐶 remains constant @ 𝑣𝑀 . Why?

KVL

• What does the output voltage waveform look like?

• 𝑣𝑂 = 𝑣𝐼 − 𝑣𝐶 = 𝑣𝑀 sin 𝜔𝑡 − 𝑣𝑀

• Does the diode switch on again?

• Ideal vs. practical scenarios.

• Output “clamped” at 0 V.

Clamper Circuits

• What happens if we add a DC voltage source in series with an ideal diode?

•

Assuming that 𝑣𝐶 𝑡 = 0 = 0 V, 𝑟𝑓 = 0 Ω, and 𝑉𝛾 = 0 V:

• 𝑡 ≤ 𝑇Τ4:

• Capacitor charges to:

• −𝑣𝑆 + 𝑣𝐶 + 𝑣𝐵 = 0

KVL

• 𝑣𝐶 = 𝑣𝑀 − 𝑣𝐵

Note: 𝒗𝑴 is the maximum input voltage @ 𝑻Τ𝟒

• 𝑡 > 𝑇Τ4 (steady-state is reached):

• Diode is off:

• Capacitor voltage is constant – large RC time constant.

• 𝑣𝑂 = 𝑣𝑆 − 𝑣𝐶 = 𝑣𝑆 − 𝑣𝑀 + 𝑣𝐵

• ∴ 𝑣𝑂 = 𝑣𝑀 sin 𝜔𝑡 − 𝑣𝑀 + 𝑣𝐵

Sine wave input

Square wave input

Example 2.8

Find the steady-state output of the diode-clamper circuit shown. The input 𝑣𝐼 is

assumed to be a sinusoidal signal whose dc level has been shifted with respect to a

receiver ground by a value 𝑉𝐵 during transmission. Assume 𝑉𝛾 = 0 V and 𝑟𝑓 = 0 Ω for the

diode.

The diode is initially reverse-biased.

For 0 ≤ 𝑡 < 𝑡1 :

Why?

𝐶 does not charge

𝑣𝑜 = 𝑣𝐼 + 𝑉𝐵

At 𝑡 = 𝑡1 :

Diode becomes forward biased.

𝑣𝑜 = 0 V because 𝑉𝛾 = 0 V.

Now the capacitor begins to charge.

At 𝑡 =

3

𝑇:

4

Note current flow for polarity

−𝑉𝐵 − (−𝑉𝑆 ) − 𝑉𝐶 = 0

KVL

𝑉𝐶 = 𝑉𝑆 − 𝑉𝐵

The capacitor is charged to the max of 𝑉𝐶 = 𝑉𝑆 − 𝑉𝐵 .

For 𝑡 >

3

𝑇:

4

The input starts to increase and the diode is once again reverse biased.

Steady state is reached where 𝑣𝑜 = 𝑣𝑖 + 𝑉𝐵 + 𝑉𝐶 = 𝑣𝑖 + 𝑉𝑆

Clamper Circuit - Exercise Problem 2.8

Sketch the steady-state output voltage for the input signal given for the circuit shown.

Assume 𝑉𝛾 = 0 V & 𝑟𝑓 = 0 Ω.

+ 𝑣𝐶 −

Apply a square wave input signal

First positive half-cycle:

𝑣𝑂 = 2 V because 𝑉𝛾 = 0 V.

𝑣𝐶 charges to 3 V.

First negative half cycle:

𝑣𝑂 = −8 V because Δ𝑣𝑖 = 10 V…

or

𝑣𝑂 = 𝑣𝑖 − 𝑣𝐶 = (−5) − 3 = −8 V

Multiple Diode Circuits

2.4

Single Diode Circuits

Problem-Solving Technique for

Multi-Diode Circuits

• Guess whether individual diodes are “on” or “off”.

• Analyse the circuit to determine if the solution is consistent with the initial guess.

• Steps:

1.

Assume the state of a diode and replace it with the circuit equivalent.

2.

Analyse the “linear circuit”.

3.

Evaluate the resulting state of each diode. If it violates the initial assumption, then the

assumption was incorrect.

4.

If the initial assumption is proven incorrect, then a new assumption must be made. Repeat

from step 1.

Forward bias - on

Reverse bias - off

Two-Diode Circuit Example

•

•

Assume 𝑉 + > 𝑉 − and 𝑉 + − 𝑉 − > 𝑉𝛾 .

Without this possibility, 𝐷2 will never turn on!

Determine the transfer function of this circuit.

•

•

•

Now we want to guess which diode is on/off. Make an educated guess!

Evaluate for 𝑣𝐼 across a range of step points. Look at the DC circuit…

When 𝑣𝐼 = 𝑉 − :

• 𝐷1 is off and 𝐷2 is on. Why?

𝑣 ′ is always greater than 𝑉 − . Note the current flow and 𝑅2 .

• 𝑖𝑅1 = 𝑖𝑅2 = 𝑖𝐷2 .

• 𝑣𝑂 = 𝑉 + − 𝑖𝑅1 𝑅1

•

•

•

𝑖𝑅1 =

𝑉 + − 𝑉 − − 𝑉𝛾

𝑅1 + 𝑅2

• The equations above will be true until 𝑣𝐼 is large enough to turn 𝐷1 on.

• Note that 𝑣 ′ = 𝑣𝑂 − 𝑉𝛾 .

• So 𝐷1 will turn on when 𝑣𝐼 = 𝑣 ′ + 𝑉𝛾 = 𝑣𝑂

When 𝑣𝐼 = 𝑣𝑂 :

• 𝐷1 is on and 𝐷2 is on.

• This state is valid until 𝑣𝐼 = 𝑉 + . Why?

When 𝑣𝐼 = 𝑉 + :

• 𝐷2 turns off.

• 𝑣𝑂 = 𝑉 + . Why?

• This state is valid for increasing 𝑣𝐼 .

Transfer Characteristics

In Conclusion

Electronics 245

Lecture 12

Bipolar Junction Transistors (BJT) – Chapter 5

5.1.1 Transistor Structures

5.1.2 – npn Transistor: Forward-Active Mode Operation

COPYRIGHT

Copyright © 2020 Stellenbosch University

All rights reserved

DISCLAIMER

This content is provided without warranty or representation of any kind. The

use of the content is entirely at your own risk and Stellenbosch University (SU)

will have no liability directly or indirectly as a result of this content.

The content must not be assumed to provide complete coverage of the

particular study material. Content may be removed or changed without

notice.

The video is of a recording with very limited post-recording editing. The video

is intended for use only by SU students enrolled in the particular module.

Transistor Structures

• Two types of Bipolar Junction Transistors (BJTs)

• pnp BJT

• npn BJT

• Three terminals – emitter, collector and base.

• The name tells you about the arrangement.

• Operation depends on the two pn junctions being

in close proximity.

• Width of the base is narrow.

• Actual structure much more complicated than

the simple block diagrams.

• Device is not symmetrical electrically.

• Emitter and collector geometry.

• Impurity doping concentrations.

• Switching the BJT around in a circuit will

impact its operation.

npn Transistor: Forward-Active

• The BJT has two pn junctions.

• There are four possible biasing states.

• In forward-active operating mode:

• B-E junction is forward biased.

• B-C junction is reverse biased.

• The transistor is also said to be biased in the

active region.

• Notation is NB!

Transistor Currents

• BJT biased in forward-active mode.

• B-E is forward biased

• Electrons injected from n to p region

• An excess minority carrier concentration is

created in the base.

• Electrons diffuse across the base

• The base is narrow, so recombination is

minimal

• B-C is reverse biased.

• Electrons are swept across the B-C junction

by the strong E-field.

• Electrons are “collected” to generate the

collector current.

Emitter Current

• B-E junction is forward biased.

• We expect that the current, 𝑖𝐸 , will be an

exponential function of voltage 𝑉𝐵𝐸 .

• 𝑖𝐸 = 𝐼𝐸𝑂 𝑒 𝑣𝐵𝐸Τ𝑉𝑇 − 1 ≈ 𝐼𝐸𝑂 𝑒 𝑣𝐵𝐸Τ𝑉𝑇

• Electrons flow from left to right.

• Current flows from right to left.

• 𝐼𝐸𝑂 is dependent on the junction parameters.

• Is also directly proportional to the B-E

junction’s cross-sectional area.

• 𝐼𝐸𝑂 typically ranges from 10−12 to 10−16 A

Collector Current

• Emitter current primarily due to electron

injection.

• Number of electrons reaching the collector per

unit time is proportional to the number of

electrons injected into the base.

• This is the main component of the collector

current.

• Collector current is therefore proportional to

𝑣𝐵𝐸 and is independent of B-C voltage.

• This device looks like a constant-current source.

• Collector current is controlled by the voltage

across the BE junction.

• 𝑖𝐶 = 𝐼𝑆 𝑒 𝑣𝐵𝐸Τ𝑉𝑇

Base Current

• Base current has two components

• B-E junction is forward-biased.

• 1) Holes are injected from B to E.

• 𝑖𝐵1 𝛼 𝑒 𝑣𝐵𝐸Τ𝑉𝑇

• Holes do not contribute to collector current.

• 2) Holes recombine with injected electrons.

• The “lost” holes must be replaced

• This recombination current is directly

proportional to the number of electrons

being injected into B from E.

• 𝑖𝐵2 𝛼 𝑒 𝑣𝐵𝐸Τ𝑉𝑇

• Total base current, 𝑖𝐵 , is:

• 𝑖𝐵 𝛼 𝑒 𝑣𝐵𝐸Τ𝑉𝑇

• 𝑖𝐵 is much smaller than 𝑖𝐶 and 𝑖𝐸

Common-Emitter Current Gain

• 𝑖𝐵 , 𝑖𝐶 , and 𝑖𝐸 are all exponential functions of 𝑣𝐵𝐸

•

𝑖𝐵 and 𝑖𝐶 are linearly related:

•

𝑖𝐶

𝑖𝐵

= 𝛽

• 𝛽 − common-emitter current gain.

• 𝛽 considered constant for a given transistor

• We will see later that it does actually vary…

• Usually 50 < 𝛽 < 300.

• 𝛽 is dependent on the transistor fabrication.

Common-Emitter Configuration

• Reconfigure the BJT to make the Emitter “common”.

• In forward-active mode:

•

B-E junction is forward biased. 𝑣𝐵𝐸 = 𝑉𝐵𝐸(𝑜𝑛)

•

B-C junction is reverse biased.

• 𝑉𝐶𝐶 = 𝑣𝐶𝐸 + 𝑖𝐶 𝑅𝐶

• 𝑉𝐶𝐶 must be large enough for B-C junction to be

reverse biased.

• 𝑖𝐵 is controlled by 𝑉𝐵𝐵 and 𝑅𝐵

•

𝑖𝐶

𝑖𝐵

= 𝛽 → 𝑖𝐶 = 𝛽𝑖𝐵

• If 𝑉𝐵𝐵 = 0 V, 𝑖𝐵 = 0 A and then 𝑖𝐶 = 0 A

• This condition is called cut-off.

Current Relationships

• Treat BJT as a single node.

• 𝑖𝐸 = 𝑖𝐶 + 𝑖𝐵

• If the BJT is in forward-active mode:

• 𝑖𝐶 = 𝛽𝑖𝐵

• 𝑖 𝐸 = 𝑖𝐵 𝛽 + 1

• 𝑖𝐵 =

• 𝑖𝐶 =

𝑖𝐸

𝛽+1

𝛽

𝛽+1

• 𝑖 𝐶 = 𝛼 𝑖𝐸

Sub into 𝑖𝐶 = 𝛽𝑖𝐵

𝑖𝐸

𝛼=

𝛽

𝛽+1

• 𝛽 − common-emitter current gain.

• 𝛼 − common-base current gain.

• Always slightly less than 1

• If 𝛽 ≫ 1, then 𝛼 ≈ 1 and 𝑖𝐶 ≈ 𝑖𝐸

In Conclusion

Electronics 245

Lecture 13

Bipolar Junction Transistors – Chapter 5

5.1.3 – pnp Transistor: Forward-Active Mode Operation

5.1.4 – Circuit Symbols and Conventions

5.1.5 – Current-Voltage Characteristics

5.1.6 – Nonideal Transistor Leakage Currents and

Breakdown Voltage (self-study)

COPYRIGHT

Copyright © 2020 Stellenbosch University

All rights reserved

DISCLAIMER

This content is provided without warranty or representation of any kind. The

use of the content is entirely at your own risk and Stellenbosch University (SU)

will have no liability directly or indirectly as a result of this content.

The content must not be assumed to provide complete coverage of the

particular study material. Content may be removed or changed without

notice.

The video is of a recording with very limited post-recording editing. The video

is intended for use only by SU students enrolled in the particular module.

pnp BJT: Forward-Active Mode

• In Forward-Active Mode:

• B-E junction is forward biased (𝑣𝐸𝐵 )

• B-C junction is reverse biased (𝑣𝐶𝐵 ).

• The pnp BJT operation is exactly the same as the

npn BJT (mechanisms are mirrored).

• Holes diffuse across B-E junction and are swept

across the B-C junction by the E-field.

• Pay attention to flow of electrons and holes as well

as notation.

• Current flow opposite to npn!

• Current Equations are the same (notation):

• 𝑖𝐸 = 𝐼𝐸𝑂 𝑒 𝑣𝐸𝐵Τ𝑉𝑇 .

• 𝑖𝐶 = 𝛼𝑖𝐸 = 𝐼𝑆 𝑒 𝑣𝐸𝐵Τ𝑉𝑇 .

• 𝑖𝐵 = 𝑖𝐵1 + 𝑖𝐵2 𝛼 𝑒 𝑣𝐸𝐵Τ𝑉𝑇

• 𝑖𝐵 = 𝐼𝐵𝑂 𝑒 𝑣𝐸𝐵Τ𝑉𝑇 =

𝑖𝐶

𝛽

=

𝐼𝑆 𝑣 Τ𝑉

𝑒 𝐸𝐵 𝑇

𝛽

Circuit Symbols and Conventions

Current-Voltage Characteristics

• Look at the common-base configuration.

npn

pnp

• Analyse 𝑖𝐶 and 𝑖𝐸 vs 𝑣𝐶𝐵 or 𝑣𝐵𝐶

• When B-C is reverse biased:

• BJT is in forward-active mode.

• 𝑖𝐶 = 𝛼𝑖𝐸

• Application - Nearly an ideal constant-current source.

• When the B-C junction becomes forward biased

• The BJT is no longer in forward-active mode.

• The current relations we have derived no longer apply.

• Why do the curves extend into negative voltage values?

• Why does the collector current reduce?

Common-Base Configuration

Current-Voltage Characteristics

• Look at the common-emitter configuration.

• Analyse 𝑖𝐶 and 𝑖𝐵 vs 𝑣𝐶𝐸 or 𝑣𝐸𝐶

• When B-C is reverse biased:

• BJT is in forward-active mode.

• Use 𝑖𝐶 = 𝛽𝑖𝐵

−

− 𝑣

𝐵𝐸

𝑣𝐶𝐸

+

+

−

𝑣𝐶𝐵 +

• When the B-C junction becomes forward biased

• The BJT is no longer in forward-active mode.

• The current relations we have derived no longer apply.

• Why are the curves now only on the positive voltage

axis?

• If 𝑖𝐶 = 𝛽𝑖𝐵 , then why is there a slope?

Common-Emitter Configuration

The Early Effect

•

Extrapolate curves to the negative x-axis intersection.

•

Intersection point is called the Early voltage.

•

𝑣𝐶𝐸 = −𝑉𝐴

•

Given as a positive quantity.

•

Same effect for pnp

•

For a given 𝑣𝐵𝐸 , if 𝑣𝐶𝐸 increases:

•

B-C space charge region width increases

•

Neutral base width decreases

•

Gradient of base minority carrier concentration increases

•

Diffusion current increases, so 𝑖𝐶 increases

In forward-active mode:

•

•

Common-Emitter Configuration

•

𝑖𝐶 = 𝐼𝑆 𝑒 𝑣𝐵𝐸 Τ𝑉𝑇 ∙ 1 +

𝑣𝐶𝐸

𝑉𝐴

The slope of the curves is

1

𝑟0

𝑽𝑨 = ∞ ?

=

Δ𝑖𝐶

ቚ

Δ𝑣𝐶𝐸 𝑣

𝐵𝐸

= 𝑐𝑜𝑛𝑠𝑡𝑎𝑛𝑡

•

Where 𝑟0 is the output resistance seen looking into the collector.

•

𝑟0 ≅

𝑉𝐴

𝐼𝐶

Example - The Early Effect

The output resistance of a bipolar transistor is 𝑟𝑜 = 225 kΩ at 𝐼𝐶 = 0.8 mA. (a) Determine

the Early voltage. (b) Using the results of part (a), find 𝑟𝑜 at 𝐼𝐶 = 0.08 mA.

a) 𝑟0 =

𝑉𝐴

𝐼𝐶

𝑉𝐴 = 𝑟0 𝐼𝐶 = 225 kΩ 0.8 mA = 180 V

b) 𝑟0 =

𝑉𝐴

𝐼𝐶

180 V

= 0.08 mA = 2.25 MΩ

Example 2 - The Early Effect

Assume that 𝐼𝐶 = 1 mA at 𝑉𝐶𝐸 = 1 V, and that 𝑉𝐵𝐸 is held constant. Determine 𝐼𝐶 at 𝑉𝐶𝐸 =

10 V if 𝑉𝐴 = 75 V.

constant

a) 𝐼𝐶 = 𝐼𝑆

↓

𝑒 𝑉𝐵𝐸 Τ𝑉𝑇

∙ 1+

𝑉𝐶𝐸

𝑉𝐴

At 𝑉𝐶𝐸 = 1 V and 𝐼𝐶 = 1 mA

1 mA = 𝐼𝑆 𝑒 𝑉𝐵𝐸 Τ𝑉𝑇 ∙ 1 +

1

75

𝐼𝑆 𝑒 𝑉𝐵𝐸 Τ𝑉𝑇 = 0.9868 mA

At 𝑉𝐶𝐸 = 10 V and 𝑉𝐴 = 75 V

𝐼𝐶 = 0.9868 mA

𝐼𝐶 = 1.12 mA

∙ 1+

10

75

In Conclusion

Electronics 245

Lecture 15

Bipolar Junction Transistors – Chapter 5

5.2.2 – Load Line and Modes of Operation (Examples)

5.2.3 – Voltage Transfer Characteristics

COPYRIGHT

Copyright © 2020 Stellenbosch University

All rights reserved

DISCLAIMER

This content is provided without warranty or representation of any kind. The

use of the content is entirely at your own risk and Stellenbosch University (SU)

will have no liability directly or indirectly as a result of this content.

The content must not be assumed to provide complete coverage of the

particular study material. Content may be removed or changed without

notice.

The video is of a recording with very limited post-recording editing. The video

is intended for use only by SU students enrolled in the particular module.

Example (TYU 5.7)

For the circuit shown, assume 𝛽 = 50. Determine 𝑉𝑂 , 𝐼𝐵 , and 𝐼𝐶 for: (a) 𝑉𝐼 = 0.2 V, and

(b) 𝑉𝐼 = 3.6 V . Then, calculate the power dissipated in the transistor for the two

conditions. Assume 𝑉𝐵𝐸(𝑜𝑛) = 0.7 V and 𝑉𝐶𝐸(𝑠𝑎𝑡) = 0.2 V.

a) When 𝑉𝐼 = 0.2 V, the transistor is in cutoff because 𝑉𝐼 < 𝑉𝐵𝐸(𝑜𝑛)

𝐼𝐵 = 𝐼𝐶 = 0 A. 𝑉𝑂 = 5 V. 𝑃 = 0 W.

b) When 𝑉𝐼 = 3.6 V, the transistor is on because 𝑉𝐼 > 𝑉𝐵𝐸(𝑜𝑛)

Assume forward-active mode.

𝐼𝐵 =

𝑉𝐼 − 𝑉𝐵𝐸(𝑜𝑛)

𝑅𝐵

=

3.6 −0.7

640

= 4.5313 mA

𝐼𝐶 = 𝛽𝐼𝐵 = 50 0.0045313 = 226.5625 mA

𝑉𝐶𝐸 = 5 − 𝑅𝐶 𝐼𝐶 = 5 − 440 0.2265625 = −94.6875 V

∴ The transistor is driven into saturation.

𝐼𝐶 =

𝐼𝐶

𝐼𝐵

=

𝑉 + − 𝑉𝐶𝐸(𝑠𝑎𝑡)

𝑅𝐶

10.9

4.53

=

5 − 0.2

440

= 10.9091 mA

= 2.41 < 𝛽

𝑃 = 𝐼𝐵 𝑉𝐵𝐸(𝑜𝑛) + 𝐼𝐶 𝑉𝐶𝐸(𝑠𝑎𝑡) = 5.35 mW

𝑽𝑪𝑬 < 𝑽𝑪𝑬(𝒔𝒂𝒕)

𝑽𝑶 = 𝑽𝑪𝑬(𝒔𝒂𝒕)

Example (TYU 5.8)

For the circuit shown, let 𝛽 = 50, and determine 𝑉𝐼 such that 𝑉𝐵𝐶 = 0 V. Calculate the

power dissipated in the transistor.

−

𝑉𝐶𝐸 = 𝑉𝐵𝐸 + 𝑉𝐶𝐵

𝑉𝐶𝐸 = 0.7 + 0 = 0.7 V = 𝑉𝑂

𝐼𝐶 =

5 −0.7

440

𝐼𝐵 =

𝐼𝐶

𝛽

=

− 𝑣

𝐵𝐸

𝑣𝐶𝐸

+

+

−

𝑣𝐶𝐵 +

= 9.77 mA

0.0097

50

= 0.195 mA

𝑉𝐼 = 𝐼𝐵 𝑅𝐵 + 𝑉𝐵𝐸(𝑜𝑛) = 0.195 mA 640 + 0.7 = 0.825 V

𝑃 = 𝐼𝐵 𝑉𝐵𝐸(𝑜𝑛) + 𝐼𝐶 𝑉𝐶𝐸 = 0.195 mA 0.7 + 9.77 mA 0.7 = 6.98 mW

+

𝑉𝐶𝐸

−

Voltage Transfer Characteristics

Develop the voltage transfer curves for the circuits.

Assume npn transistor parameters of 𝑉𝐵𝐸(𝑜𝑛) = 0.7 V, 𝛽 = 120, 𝑉𝐶𝐸(𝑠𝑎𝑡) = 0.2 V, and 𝑉𝐴 = ∞, and

pnp transistor parameters of 𝑉𝐸𝐵(𝑜𝑛) = 0.7 V, 𝛽 = 80, 𝑉𝐸𝐶(𝑠𝑎𝑡) = 0.2 V, and 𝑉𝐴 = ∞.

npn Transistor:

𝑉𝐼 ≤ 0.7 V

Transistor is in cut off.

𝐼𝐵 = 𝐼𝐶 = 0 A, 𝑉𝑂 = 5 V

𝑉𝐼 > 0.7 V

Transistor Qn turns on. Forward-active mode.

𝐼𝐵 =

𝑉𝐼 −0.7

𝑅𝐵

𝐼𝐶 = 𝛽𝐼𝐵 =

𝛽 𝑉𝐼 −0.7

𝑅𝐵

𝑉𝑂 = 5 − 𝐼𝐶 𝑅𝐶 = 5 −

𝑅𝐶 𝛽 𝑉𝐼 −0.7

𝑅𝐵

𝑽𝑰 ↑, 𝑽𝑶 ↓

Valid for 0.2 ≤ 𝑉𝑂 ≤ 5 V.

@ saturation, 0.2 = 5 −

(5000)(120) 𝑉𝐼 −0.7

(150000)

𝑉𝐼 = 1.9 V

pnp Transistor

4.3 ≤ 𝑉𝐼 ≤ 5 V

Transistor is in cut off.

𝐼𝐵 = 𝐼𝐶 = 0 A, 𝑉𝑂 = 0 V

𝑉𝐼 < 4.3 V

Transistor Qp turns on. Forward-active mode.

𝐼𝐵 =

5 −0.7 − 𝑉𝐼

𝑅𝐵

5 −0.7 − 𝑉𝐼

𝑅𝐵

5 −0.7 − 𝑉𝐼

𝛽𝑅𝐶

𝑅

𝐼𝐶 = 𝛽𝐼𝐵 = 𝛽

𝑉𝑂 = 𝐼𝐶 𝑅𝐶 =

𝐵

Valid for 0 ≤ 𝑉𝑂 ≤ 4.8 V.

@ saturation, 4.8 = (80)(8000)

5 −0.7 − 𝑉𝐼

200000

𝑉𝐼 = 2.8 V

NgSpice Simulation (Example 5.6)

4

BJT Voltage Transfer Curve (Example 5.6; Fig 5.27a)

Vin 1 0 DC

R1 1 2 150k

R2 3 4 5k

Vp 4 0 5

Qn 3 2 0 2N2222

* 2N2222 BJT model

.model 2N2222 NPN(IS=1E-14 VAF=100 BF=200 IKF=0.3

+ XTB=1.5 BR=3 CJC=8E-12 CJE=25E-12 TR=100E-9

+ TF=400E-12 ITF=1 VTF=2 XTF=3 RB=10 RC=.3 RE=.2)

.DC Vin 0 5 0.05

.control

run

plot v(3)

set nobreak

print v(3) > Ex5p6.xls

.endc

.end

3

1

2

0

Voltage Transfer Characteristics (Exercise Problem 5.6)

Develop the voltage transfer curve for the circuit below.

The transistor parameters are 𝛽 = 100, 𝑉𝐵𝐸(𝑜𝑛) = 0.7 V, and 𝑉𝐶𝐸(𝑠𝑎𝑡) = 0.2 V. Plot the

voltage transfer characteristics for 0 ≤ 𝑉𝐼 ≤ 9 𝑉.

When 0 ≤ 𝑉𝐼 < 0.7 V, Qn is in cutoff.

𝐼𝐵 = 𝐼𝐶 = 0 A, 𝑉𝑂 = 9 V

𝑉𝐼 > 0.7 V

Transistor Qn turns on. Forward-active mode.

𝐼𝐵 =

𝑉𝐼 −0.7

𝑅𝐵

𝐼𝐶 = 𝛽𝐼𝐵 =

𝛽 𝑉𝐼 −0.7

𝑅𝐵

𝑉𝑂 = 9 − 𝐼𝐶 𝑅𝐶 = 9 −

@ saturation, 0.2 = 9 −

𝑉𝐼 = 5.1 V

𝑉𝐼 ≥ 5.1 V, 𝑉𝑂 = 0.2 V

𝑅𝐶 𝛽 𝑉𝐼 −0.7

𝑅𝐵

(4000)(100) 𝑉𝐼 −0.7

200000

In Conclusion

Electronics 245

Lecture 16

Bipolar Junction Transistors – Chapter 5

5.2.4 - Commonly Used Bipolar Circuits: dc Analysis

COPYRIGHT

Copyright © 2020 Stellenbosch University

All rights reserved

DISCLAIMER

This content is provided without warranty or representation of any kind. The

use of the content is entirely at your own risk and Stellenbosch University (SU)

will have no liability directly or indirectly as a result of this content.

The content must not be assumed to provide complete coverage of the

particular study material. Content may be removed or changed without

notice.

The video is of a recording with very limited post-recording editing. The video

is intended for use only by SU students enrolled in the particular module.

Example 5.7

Calculate the characteristics of a circuit containing an emitter resistor. For the circuit

shown, let 𝑉𝐵𝐸(𝑜𝑛) = 0.7 V and 𝛽 = 75 . Note that the circuit has both positive and

negative power supply voltages.

𝑉𝐵𝐵 = 𝐼𝐵 𝑅𝐵 + 𝑉𝐵𝐸(𝑜𝑛) + 𝐼𝐸 𝑅𝐸 + 𝑉 −

1

Assume forward active mode. We must prove this later.

𝐼𝐸 = 1 + 𝛽 𝐼𝐵

2

Solve equation 1 for 𝐼𝐵 and sub equation 2 in.

𝐼𝐵 =

𝑉𝐵𝐵 − 𝑉𝐵𝐸(𝑜𝑛) − 𝑉 −

𝑅𝐵 + 1+ 𝛽 𝑅𝐵

=

1 − 0.7 − −1.8

(560000+ 76 3000 )

= 2.665 μA

𝐼𝐶 = 𝛽𝐼𝐵 = 75 2.665 μA = 0.2 mA

𝐼𝐸 = 1 + 𝛽 𝐼𝐵 = 76 2.665 μA = 0.203 mA

𝑉𝐶𝐸 = 𝑉 + − 𝐼𝐶 𝑅𝐶 − 𝐼𝐸 𝑅𝐸 − 𝑉 −

𝑉𝐶𝐸 = 1.8 − 0.2 mA 7000 − 0.203 mA 3000 − −1.8 = 1.59 V

Assumption Correct!

Example 5.7 – Load Lines

Calculate the characteristics of a circuit containing an emitter resistor. For the circuit

shown, let 𝑉𝐵𝐸(𝑜𝑛) = 0.7 V and 𝛽 = 75 . Note that the circuit has both positive and

negative power supply voltages.

Same as previous slide – use load lines

𝑉𝐶𝐸 = 𝑉 + − 𝐼𝐶 𝑅𝐶 − 𝐼𝐸 𝑅𝐸 − 𝑉 −

𝐼𝐸 =

𝛽+1

𝛽

𝐼𝐶

𝑉𝐶𝐸 = 𝑉 + − 𝑉 − − 𝐼𝐶 𝑅𝐶 −

𝑉𝐶𝐸 = 1.8 − −1.8

𝛽+1

𝛽

− 𝐼𝐶 𝑅𝐶 +

𝑉𝐶𝐸 = 3.6 − 𝐼𝐶 7000 +

76

75

𝑉𝐶𝐸 = 3.6 − 𝐼𝐶 10040

𝑉𝐶𝐸 = 0 V → 𝐼𝐶 = 0.3586 mA

𝐼𝐶 = 0 A → 𝑉𝐶𝐸 = 3.6 V

Same answer!

𝐼𝐶 𝑅𝐸

𝛽+1

𝛽

3000

𝑅𝐸

Design Example 5.8

Design the common-base circuit such that 𝐼𝐸𝑄 = 0.50 mA and 𝑉𝐸𝐶𝑄 = 4.0 V. Assume

transistor parameters of 𝛽 = 120 and 𝑉𝐸𝐵(𝑜𝑛) = 0.7 V.

KVL around BE loop

𝑉 + = 𝐼𝐸𝑄 𝑅𝐸 + 𝑉𝐸𝐵(𝑜𝑛) + 𝐼𝐵𝑄 𝑅𝐵

+

𝑉 = 𝐼𝐸𝑄 𝑅𝐸 + 𝑉𝐸𝐵(𝑜𝑛) +

𝐼𝐸𝑄

𝛽+1

5 = 0.5 mA 𝑅𝐸 + 0.7 +

𝐼𝐵𝑄 =

𝐼𝐸𝑄

𝛽+1

𝑅𝐵

0.5 mA

121

10000

𝑅𝐸 = 8.52 kΩ

𝐼𝐶𝑄 =

𝛽

𝛽+1

𝐼𝐸𝑄 = 0.496 mA

𝑉 + = 𝐼𝐸𝑄 𝑅𝐸 + 𝑉𝐸𝐶𝑄 + 𝐼𝐶𝑄 𝑅𝐶 + 𝑉 −

5 = 0.5 mA 8.52 kΩ + 4 + 0.496 mA 𝑅𝐶 + −5

𝑅𝐶 = 3.51 kΩ

+ 𝑽𝑬𝑪𝑸 −

+

𝑽𝑬𝑩

−

Design Example 5.9

Objective: Design a pnp bipolar transistor circuit to meet a set of specifications.

Specifications: The circuit configuration to be designed is shown. The quiescent emitter-collector voltage is to be

𝑉𝐸𝐶𝑄 = 2.5 V.