KUMARAGURU COLLEGE OF TECHNOLOGY

COIMBATORE – 641049

Department of Information Technology

LABORATORY RECORD

U18ITI2201L – Digital Logic and Microprocessor Laboratory

Regulation 2018

NAME

:

ROLL NO

:

YEAR / SEM

:

KUMARAGURU COLLEGE OF TECHNOLOGY

COIMBATORE – 641049

DEPARTMENT OF INFORMATION TECHNOLOGY

U18ITI2201L – Digital Logic and Microprocessor Laboratory

Bona-fide Certificate

Roll Number

Certified that this is the bona-fide record of work done by

Mr/Ms______________________________________ of the ________________ semester in

__________________________________________________________

branch

during

the

academic year____________________

Staff in – Charge

Submitted for the University Practical Examination held on ………………………………….

Internal Examiner

Index

S.No

Date

Name of the Experiments

1.

Implementation of logic functions

2.

Adders and Subtractors

3.

Combinational Circuit Design

4.

Sequential Circuit Design

5.

ALP Arithmetic programming

6.

Sorting

7.

Data Movement

8.

Wave form Generation using 8255

9.

Display the given message using 8279

10.

Interfacing analog to digital converter to

8086

Average out of 30

Marks Signature

Page

Obtained

of the

No

(30)

Faculty

Exp No :

Date :

01

Implementation of logic functions

OBJECTIVE

1. To study about logic gates and verify their truth tables.

2. To implement a simple Boolean expression

APPARATUS REQUIRED

SL No.

COMPONENT

SPECIFICATION

QTY

1.

AND GATE

IC 7408

1

2.

OR GATE

IC 7432

1

3.

NOT GATE

IC 7404

1

4.

NAND GATE 2 I/P

IC 7400

1

5.

NOR GATE

IC 7402

1

6.

X-OR GATE

IC 7486

1

7.

NAND GATE 3 I/P

IC 7410

1

8.

IC TRAINER KIT

-

1

9.

PATCH CORD

-

As

Required

THEORY:

Circuit that takes the logical decision and the process are called logic gates. Each

gate has one or more input and only one output.

OR, AND and NOT are basic gates. NAND, NOR and X-OR are known as universal

gates. Basic gates form these gates.

1

AND GATE:

SYMBOL:

PIN DIAGRAM:

OR GATE:

2

AND GATE:

The AND gate performs a logical multiplication commonly known as AND function.

The output is high when both the inputs are high. The output is low level when any one of

the inputs is low.

OR GATE:

The OR gate performs a logical addition commonly known as OR function. The

output is high when any one of the inputs is high. The output is low level when both the

inputs are low.

NOT GATE:

The NOT gate is called an inverter. The output is high when the input is low. The

output is low when the input is high.

NAND GATE:

The NAND gate is a contraction of AND-NOT. The output is high when both inputs

are low and any one of the input is low. The output is low level when both inputs are high.

NOR GATE:

The NOR gate is a contraction of OR-NOT. The output is high when both inputs are

low. The output is low when one or both inputs are high.

X-OR GATE:

The output is high when any one of the inputs is high. The output is low when both

the inputs are low and both the inputs are high.

3

NOT GATE:

SYMBOL:

PIN DIAGRAM:

X-OR GATE :

SYMBOL :

PIN DIAGRAM :

4

2-INPUT NAND GATE:

SYMBOL:

PIN DIAGRAM:

3-INPUT NAND GATE :

5

NOR GATE:

2) Implementation of Boolean Expression:

DeMorgan’s Theorem

A.B = A+B

6

A+B = A.B

PROCEDURE:

(i)

Connections are given as per circuit diagram.

(ii)

Logical inputs are given as per circuit diagram.

(iii)

Observe the output and verify the truth table.

RESULT:

7

Preparation

/10

Observation

/10

Viva

/10

Total

/30

ADDERS

HALF ADDER

TRUTH TABLE:

K-Map for SUM:

SUM = A’B + AB’

A

B

CARRY

SUM

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

K-Map for CARRY:

CARRY = AB

8

Exp No :

Date :

02

Adders and Subtractors

OBJECTIVE

To construct adders, subtractors and verify the truth table using logic gates.

APPARATUS REQUIRED

Sl.No.

COMPONENT

SPECIFICATION

QTY.

1.

AND GATE

IC 7408

1

2.

X-OR GATE

IC 7486

1

3.

NOT GATE

IC 7404

1

4.

OR GATE

IC 7432

1

3.

IC TRAINER KIT

-

1

4.

PATCH CORDS

-

As

Required

THEORY:

HALF ADDER:

A half adder has two inputs for the two bits to be added and two outputs one from

the sum ‘ S’ and other from the carry ‘ c’ into the higher adder position. Above circuit is

called as a carry signal from the addition of the less significant bits sum from the X-OR Gate

the carry out from the AND gate.

9

FULL ADDER

FULL ADDER USING TWO HALF ADDER

TRUTH TABLE:

A

B

C

CARRY

SUM

0

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

1

0

1

0

0

0

1

1

0

1

1

0

1

1

0

1

0

1

1

1

1

1

K-Map for SUM:

K-Map for CARRY:

SUM = A’B’C + A’BC’ + ABC’ + ABC

CARRY = AB + BC + AC

10

FULL ADDER:

A full adder is a combinational circuit that forms the arithmetic sum of input; it

consists of three inputs and two outputs. A full adder is useful to add three bits at a time

but a half adder cannot do so. In full adder sum output will be taken from X-OR Gate, carry

output will be taken from OR Gate.

HALF SUBTRACTOR:

The half subtractor is constructed using X-OR and AND Gate. The half subtractor has

two inputs and two outputs. The outputs are difference and borrow. The difference can be

applied using X-OR Gate, borrow output can be implemented using an AND Gate and an

inverter.

FULL SUBTRACTOR:

The full subtractor is a combination of X-OR, AND, OR, NOT Gates. In a full

subtractor the logic circuit should have three inputs and two outputs. The two half

subtractor put together gives a full subtractor. The first half subtractor will be C and A B.

The output will be difference output of full subtractor. The expression AB assembles the

borrow output of the half subtractor and the second term is the inverted difference output

of first X-OR.

11

SUBTRACTOR

HALF SUBTRACTOR:

TRUTH TABLE:

K-Map for Difference:

K- Map for Borrow:

LOGIC DIAGRAM:

12

FULL SUBTRACTOR:

TRUTH TABLE:

K-Map for Difference:

K- Map for Borrow:

13

LOGIC DIAGRAM:

14

PROCEDURE:

(i)

Connections are given as per circuit diagram.

(ii)

Logical inputs are given as per circuit diagram.

(iii)

Observe the output and verify the truth table.

RESULT:

15

Preparation

/10

Observation

/10

Viva

/10

Total

/30

Encoder & Decoder

Encoder

Truth table

Logical expression & Diagram

A1 = Y3+Y2

A0 = Y3+Y1

16

Exp No :

Date :

03

Combinational Circuit Design

OBJECTIVE

To construct encoder, decoder, multiplexer, demultiplexer, and code converters

and verify the truth table using logic gates.

APPARATUS REQUIRED

Sl.No.

COMPONENT

SPECIFICATION

QTY.

1.

3 I/P AND GATE

IC 7411

2

2.

AND GATE

IC7408

1

3.

OR GATE

IC 7432

1

4.

NOT GATE

IC 7404

1

5.

XOR GATE

IC7486

1

6.

IC TRAINER KIT

-

1

7.

PATCH CORDS

-

THEORY:

ENCODER

An encoder is a combinational logic circuit that generate n output lines from 2n (or less)

inputs. It has the reverse function of the decoder. An encoder accepts digit on its inputs,

such as a decimal or octal digit, and converts it to a coded output, such as a binary or BCD.

Encoder can also be devised to encode various symbol and alphabetic characters. This

process of converting from familiar symbols or numbers to a coded format is called

encoding.

DECODER

A decoder is a combinational logic circuit that takes a binary input, usually in a coded form,

and produces a one-bit output, on one of 2n output lines. The logic state (1 or 0) on any of

the output lines depends on a code appearing on the input lines.

17

Decoder

Truth Table

Y3 = A1+A0,

Y2 = A1+A0’ ,

Y1 = A1’+A0 ,

Logic Diagram

18

Y0 = A1’+A0’

MULTIPLEXER:

Multiplexer means transmitting many information units over a smaller number of channels

or lines. A digital multiplexer is a combinational circuit that selects binary information from

one of many input lines and directs it to a single output line. The selection of an input line is

controlled by a set of selection lines. Normally there are 2n input lines and n selection lines

whose bit combination determine which input is selected. Thus, multiplexer is called as

data selector.

DEMULTIPLEXER:

The function of Demultiplexer contrasts with multiplexer function. It takes

information from one line and distributes it to a given number of output lines. For this

reason, the demultiplexer is also known as a data distributor.

Gray Code

Gray code – also known as Cyclic Code, Reflected Binary Code (RBC), Reflected Binary

(RB) or Grey code – is defined as an ordering of the binary number system such that each

incremental value can only differ by one bit. In gray code, while traversing from one step to

another step only one bit in the code group changes. That is to say that two adjacent code

numbers differ from each other by only one bit.

Gray code is the most popular of the unit distance codes, but it is not suitable for arithmetic

operations. Gray code has some applications in analog to digital converters, as well as being

used for error correction in digital communication. Gray code can be difficult to understand

initially, but becomes much easier to understand when looking at the gray code tables

below.

Binary to Gray Code Converter

The logical circuit which converts the binary code to equivalent gray code is known as

binary to gray code converter. An n-bit gray code can be obtained by reflecting an n-1 bit

code about an axis after 2n-1 rows and putting the MSB (Most Significant Bit) of 0 above the

axis and the MSB of 1 below the axis.

19

Multiplexer & Demultiplexer

Multiplexer

Truth Table

Y=S1′S0′I0+S1′S0I1+S1S0′I2+S1S0I3

Logic Diagram

20

Demultiplexer

Truth Table

Y3=S1S0I,

Y2= S1S0′I,

Y1=S1′S0I,

Logic Diagram

21

Y0=s1′s0′I

Code Converters

Binary to Gray code converter

Truth Table

K – Map

K-map for

– G0

G0 = b0 Ꚛ b1

22

K-map for

– G1

G1 = b1 Ꚛ b2

K-map for

– G2

G2 = b2 Ꚛ b3

K-map for

G1 = b3

23

– G3

Logic Diagram

24

PROCEDURE:

(i)

Connections are given as per circuit diagram.

(ii)

Logical inputs are given as per circuit diagram.

(iii)

Observe the output and verify the truth table.

RESULT:

25

Preparation

/10

Observation

/10

Viva

/10

Total

/30

LOGIC DIAGRAM

Basic flipflop using NAND gates

Truth Table

S

R

Q

0

0

Forbidden

0

1

1

1

0

0

1

1

No Change

Basic flipflop using NOR gates

S

R

Q

0

0

No Change

0

1

0

1

0

1

1

1

Forbidden

R-S flip-flop using NAND gates

26

S

R

Q

0

0

No Change

0

1

0

1

0

1

1

1

Forbidden

Exp No :

Date :

04

Sequential Circuit Design

OBJECTIVE

To construct basic flip-flops R-S , D, J-K,T using gates and verify their truth tables.

To construct counters and shift registers using flip flop IC’s.

APPARATUS REQUIRED

Sl.No.

COMPONENT

SPECIFICATION

QTY.

1.

3 input NAND GATE

IC 7410

1

2.

NOR GATE

IC 7402

1

3.

NAND GATE

IC 7400

1

4.

NOT GATE

IC 7404

1

5.

D FLIP FLOP

IC 7474

2

6.

JK FLIP FLOP

IC 7476

2

7.

IC TRAINER KIT

-

1

8.

PATCH CORDS

-

As Required

THEORY

A flip-flop or latch is a circuit that has two stable states and can be used to store

state information. The circuit can be made to change state by signals applied to one or more

control inputs and will have one or two outputs. It is the basic storage element

in sequential logic. Flip-flops and latches are a fundamental building block of digital

electronics systems used in computers, communications, and many other types of systems.

Flip-flops and latches are used as data storage elements. Such data storage can be

used for storage of state, and such a circuit is described as sequential logic. When used in

a finite-state machine, the output and next state depend not only on its current input, but

also on its current state (and hence, previous inputs). It can also be used for counting of

pulses, and for synchronizing variably-timed input signals to some reference timing signal.

27

J-k flip-flop using NAND gates

28

J

K

Q

0

0

No Change

0

1

0

1

0

1

1

1

Race around

Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edgetriggered); the simple ones are commonly called latches. The word latch is mainly used for

storage elements, while clocked devices are described as flip-flops.A latch is level-sensitive,

whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes

transparent, while a flip flop's output only changes on a single type (positive going or

negative going) of clock edge.

PIN diagram of IC 7474

29

Counters

2-bit asynchronous counter (Ripple Counter)

30

Binary Counters

Normally binary counters are used for counting the number of pulses coming at the input

line in a specified time period.

The binary counters must possess memory since it has to remember its past states.

As the name suggests, it is a circuit which counts. The main purpose of the counter is to

record the number of occurrences of some input.

Counters can be classified into two broad categories according to the way they are clocked:

•

•

Asynchronous (Ripple) Counters – The first flip-flop is clocked by the external

clock pulse, and then each successive flip-flop is clocked by the Q or Q’ output of

the previous flip-flop.

Synchronous Counters – All memory elements are simultaneously triggered by

the same clock.

Classification of counters

Depending on the way in which the counting progresses, the synchronous or asynchronous

counters are classified as follows.

▪

Up counters

▪

Down counters

▪

Up/Down counters

31

2-bit synchronous counter

32

Shift registers

The Shift Register is another type of sequential logic circuit that can be used for the storage

or the transfer of binary data

This sequential device loads the data present on its inputs and then moves or “shifts” it to

its output once every clock cycle, hence the name Shift Register.

A shift register basically consists of several single bit “D-Type Data Latches”, one for each

data bit, either a logic “0” or a “1”, connected together in a serial type daisy-chain

arrangement so that the output from one data latch becomes the input of the next latch and

so on.

Data bits may be fed in or out of a shift register serially, that is one after the other from

either the left or the right direction, or all together at the same time in a parallel

configuration.

The number of individual data latches required to make up a single Shift Register device is

usually determined by the number of bits to be stored with the most common being 8-bits

(one byte) wide constructed from eight individual data latches.

Shift Registers are used for data storage or for the movement of data and are therefore

commonly used inside calculators or computers to store data such as two binary numbers

before they are added together, or to convert the data from either a serial to parallel or

parallel to serial format. The individual data latches that make up a single shift register are

all driven by a common clock ( Clk ) signal making them synchronous devices.

Shift register IC’s are generally provided with a clear or reset connection so that they can be

“SET” or “RESET” as required. Generally, shift registers operate in one of four different

modes with the basic movement of data through a shift register being:

33

Serial-in to Serial-out (SISO) Shift Register

Serial-in to Parallel-out (SIPO) Shift Register

34

▪

Serial-in to Parallel-out (SIPO) - the register is loaded with serial data, one bit at a

time, with the stored data being available at the output in parallel form.

▪

Serial-in to Serial-out (SISO) - the data is shifted serially “IN” and “OUT” of the

register, one bit at a time in either a left or right direction under clock control.

▪

Parallel-in to Serial-out (PISO) - the parallel data is loaded into the register

simultaneously and is shifted out of the register serially one bit at a time under clock

control.

▪

Parallel-in to Parallel-out (PIPO) - the parallel data is loaded simultaneously into

the register, and transferred together to their respective outputs by the same clock

pulse.

Types of Shift Registers

Shift registers are categorized into types majorly by their mode of operation, either

serial or parallel.

There are six (6) basic types of shift registers which are listed below although some of

them can be further divided based on direction of data flow either shift right or shift left.

1. Serial in – Serial out Shift Register (SISO)

2. Serial In – Parallel out shift Register (SIPO)

3. Parallel in – Parallel out Shift Register (PIPO)

4. Parallel in – Serial out Shift Register (PISO)

5. Bidirectional Shift Registers

6. Counters

35

to Serial-out (PISO) Shift Register

Parallel-in to Parallel-out (PIPO) Shift Register

36

PROCEDURE:

(i)

Connections are given as per circuit diagram.

(ii)

Logical inputs are given as per circuit diagram.

(iii)

Observe the output and verify the truth table.

RESULT:

37

Preparation

/10

Observation

/10

Viva

/10

Total

/30

38

8086

MICROPROCESSORS

EXPERIMENTS

39

EXECUTION PROCEDURE FOR 8086 (for registers)

i) Writing an alp program into processor:

Switch On Power Supply

Press A 2times

SG 0 press enter

DA starting address

Press enter

N

Then display shows @ here you have to write 1 Mnemonic

Press enter

N (display displays address Opcode mnemonic)

N

Then display shows @ here you have to write 2nd mnemonic

Press enter

N

N

Then display shows @ up to last mnemonic

Press enter

N

N

40

! Press enter

EX press enter

ii) Execution of program (for registers):

G enter starting address

Press enter

iii) Verify the result (for registers):

Press R

Press E.

EXECUTION PROCEDURE FOR 8086 (for memory locations)

i) Writing an alp program into processor:

Switch On Power Supply

Press A

A

SG 0

Press enter

DA starting address

Press enter

N

Then display shows @ here you have to write 1st mnemonic

Press enter

N (display displays address Opcode mnemonic)

41

N

Then display shows @ here you have to write 2nd mnemonic

Press enter

N

N

Then display shows @ up to last mnemonic

Press enter

N

N

! Press enter

EX press enter

E (exam byte)

Here you have to type SI address, give 1st data, 2nd data, -----, nth data,

Press enter

ii) Execution of program (for memory locations):

G enter starting address

Press enter

42

iii) Verify the result (for memory locations):

E

Then give DI address press, then display shows the result of 1st 8 bit data

For 2nd 8 bit data again press, -------, nth data

43

PRE-REQUISITES

16Bit Microprocessor: 8086

Features of 8086

❖ 8086 is a 16bit processor. It’s ALU, internal registers works with 16bit binary word

❖ 8086 has a 16bit data bus. It can read or write data to a memory/port either 16bits

or 8 bit at a time

❖ 8086 has a 20bit address bus which means, it can address up to 2 20 = 1MB memory

location

❖ Frequency range of 8086 is 6-10 MHz

44

45

PIN DIAGRAM OF 8086

Power supply and frequency signals

Clock signal

It uses 5V DC supply at VCC pin 40, and uses Clock signal is provided through Pin-19. It

ground at VSS pin 1 and 20 for its operation.

provides timing to the processor for operations.

Its frequency is different for different versions,

i.e. 5MHz, 8MHz and 10MHz.

Address/data bus

Address/status bus

AD0-AD15. These are 16 address/data bus.

AD0-AD7 carries low order byte data and

AD8AD15 carries higher order byte data.

During the first clock cycle, it carries 16-bit

address and after that it carries 16-bit data.

S7/BHE

A16-A19/S3-S6. These are the 4 address/status

buses. During the first clock cycle, it carries 4-bit

address and later it carries status signals.

Read ($\overline{RD}$)

BHE stands for Bus High Enable. It is available It is available at pin 32 and is used to read signal

at pin 34 and used to indicate the transfer of for Read operation.

data using data bus D8-D15. This signal is low

during the first clock cycle, thereafter it is

active.

46

Ready

RESET

It is available at pin 32. It is an

acknowledgement signal from I/O devices that

data is transferred. It is an active high signal.

When it is high, it indicates that the device is

ready to transfer data. When it is low, it

indicates wait state.

INTR

It is available at pin 21 and is used to restart the

execution. It causes the processor to immediately

terminate its present activity. This signal is active

high for the first 4 clock cycles to RESET the

microprocessor.

It is available at pin 18. It is an interrupt

request signal, which is sampled during the last

clock cycle of each instruction to determine if

the processor considered this as an interrupt or

not.

It stands for non-maskable interrupt and is

available at pin 17. It is an edge triggered input,

which causes an interrupt request to the

microprocessor.

NMI

$\overline{TEST}$

MN/$\overline{MX}$

This signal is like wait state and is available at pin

23. When this signal is high, then the processor

has to wait for IDLE state, else the execution

continues.

INTA

It stands for Minimum/Maximum and is

available at pin 33. It indicates what mode the

processor is to operate in; when it is high, it

works in the minimum mode and vice-versa.

ALE

It is an interrupt acknowledgement signal and id

available at pin 24. When the microprocessor

receives this signal, it acknowledges the

interrupt.

DEN

It stands for address enable latch and is

available at pin 25. A positive pulse is generated

each time the processor begins any operation.

This signal indicates the availability of a valid

address on the address/data lines.

DT/R

It stands for Data Enable and is available at pin

26. It is used to enable Transreceiver 8286. The

transreceiver is a device used to separate data

from the address/data bus.

It stands for Data Transmit/Receive signal and

is available at pin 27. It decides the direction of

data flow through the transreceiver. When it is

high, data is transmitted out and vice-a-versa.

This signal is used to distinguish between

memory and I/O operations. When it is high, it

indicates I/O operation and when it is low

indicates the memory operation. It is available at

pin 28.

M/IO

47

WR

HLDA

It stands for write signal and is available at pin

29. It is used to write the data into the memory

or the output device depending on the status of

M/IO signal.

HOLD

It stands for Hold Acknowledgement signal and is

available at pin 30. This signal acknowledges the

HOLD signal.

QS1 and QS0

This signal indicates to the processor that These are queue status signals and are available

external devices are requesting to access the at pin 24 and 25. These signals provide the status

address/data buses. It is available at pin 31

of instruction queue. Their conditions are shown

in the following table −

LOCK

QS0 QS1 Status

When this signal is active, it indicates to the

other processors not to ask the CPU to leave the

system bus. It is activated using the LOCK prefix

on any instruction and is available at pin 29.

0

0

No operation

0

1

First byte of opcode from the queue

1

0

Empty the queue

1

1

Subsequent byte from the queue

S0, S1, S2

RQ/GT1 and RQ/GT0

These are the status signals that provide the

status of operation, which is used by the Bus

Controller 8288 to generate memory & I/O

control signals. These are available at pin 26,

27, and 28. Following is the table showing their

status −

These are the Request/Grant signals used by the

other processors requesting the CPU to release

the system bus. When the signal is received by

CPU, then it sends acknowledgment. RQ/GT0 has

a higher priority than RQ/GT1.

S2 S1 S0 Status

0

0

0

Interrupt acknowledgement

0

0

1

I/O Read

0

1

0

I/O Write

0

1

1

Halt

1

0

0

Opcode fetch

1

0

1

Memory read

1

1

0

Memory write

1

1

1

Passive

48

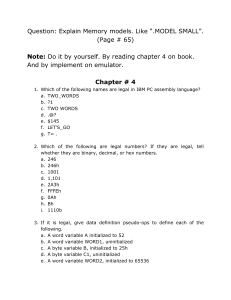

INSTRUCTION SETS OF 8086

•

•

•

•

•

•

•

•

Data Transfer Instructions

Arithmetic Instructions

Bit Manipulation Instructions

String Instructions

Program Execution Transfer Instructions (Branch & Loop Instructions)

Processor Control Instructions

Iteration Control Instructions

Interrupt Instructions

Let us now discuss these instruction sets in detail.

Data Transfer Instructions

These instructions are used to transfer the data from the source operand to the destination

operand. Following are the list of instructions under this group −

Instruction to transfer a word

•

•

•

•

•

•

•

MOV − Used to copy the byte or word from the provided source to the provided

destination.

PPUSH − Used to put a word at the top of the stack.

POP − Used to get a word from the top of the stack to the provided location.

PUSHA − Used to put all the registers into the stack.

POPA − Used to get words from the stack to all registers.

XCHG − Used to exchange the data from two locations.

XLAT − Used to translate a byte in AL using a table in the memory.

Instructions for input and output port transfer

•

•

IN − Used to read a byte or word from the provided port to the accumulator.

OUT − Used to send out a byte or word from the accumulator to the provided port.

Instructions to transfer the address

•

•

•

LEA − Used to load the address of operand into the provided register.

LDS − Used to load DS register and other provided register from the memory

LES − Used to load ES register and other provided register from the memory.

Instructions to transfer flag registers

•

•

•

LAHF − Used to load AH with the low byte of the flag register.

SAHF − Used to store AH register to low byte of the flag register.

PUSHF − Used to copy the flag register at the top of the stack.

49

•

POPF − Used to copy a word at the top of the stack to the flag register.

Arithmetic Instructions

These instructions are used to perform arithmetic operations like addition, subtraction,

multiplication, division, etc.

Following is the list of instructions under this group −

Instructions to perform addition

•

•

•

•

•

ADD − Used to add the provided byte to byte/word to word.

ADC − Used to add with carry.

INC − Used to increment the provided byte/word by 1.

AAA − Used to adjust ASCII after addition.

DAA − Used to adjust the decimal after the addition/subtraction operation.

Instructions to perform subtraction

•

•

•

•

•

•

•

SUB − Used to subtract the byte from byte/word from word.

SBB − Used to perform subtraction with borrow.

DEC − Used to decrement the provided byte/word by 1.

NPG − Used to negate each bit of the provided byte/word and add 1/2’s

complement.

CMP − Used to compare 2 provided byte/word.

AAS − Used to adjust ASCII codes after subtraction.

DAS − Used to adjust decimal after subtraction.

Instruction to perform multiplication

•

•

•

MUL − Used to multiply unsigned byte by byte/word by word.

IMUL − Used to multiply signed byte by byte/word by word.

AAM − Used to adjust ASCII codes after multiplication.

Instructions to perform division

•

•

•

•

•

DIV − Used to divide the unsigned word by byte or unsigned double word by word.

IDIV − Used to divide the signed word by byte or signed double word by word.

AAD − Used to adjust ASCII codes after division.

CBW − Used to fill the upper byte of the word with the copies of sign bit of the lower

byte.

CWD − Used to fill the upper word of the double word with the sign bit of the lower

word.

50

Bit Manipulation Instructions

These instructions are used to perform operations where data bits are involved, i.e.

operations like logical, shift, etc.

Following is the list of instructions under this group −

Instructions to perform logical operation

•

•

•

•

•

NOT − Used to invert each bit of a byte or word.

AND − Used for adding each bit in a byte/word with the corresponding bit in

another byte/word.

OR − Used to multiply each bit in a byte/word with the corresponding bit in another

byte/word.

XOR − Used to perform Exclusive-OR operation over each bit in a byte/word with

the corresponding bit in another byte/word.

TEST − Used to add operands to update flags, without affecting operands.

Instructions to perform shift operations

•

•

•

SHL/SAL − Used to shift bits of a byte/word towards left and put zero(S) in LSBs.

SHR − Used to shift bits of a byte/word towards the right and put zero(S) in MSBs.

SAR − Used to shift bits of a byte/word towards the right and copy the old MSB into

the new MSB.

Instructions to perform rotate operations

•

•

•

•

ROL − Used to rotate bits of byte/word towards the left, i.e. MSB to LSB and to Carry

Flag [CF].

ROR − Used to rotate bits of byte/word towards the right, i.e. LSB to MSB and to

Carry Flag [CF].

RCR − Used to rotate bits of byte/word towards the right, i.e. LSB to CF and CF to

MSB.

RCL − Used to rotate bits of byte/word towards the left, i.e. MSB to CF and CF to LSB.

String Instructions

String is a group of bytes/words and their memory is always allocated in a sequential

order.

Following is the list of instructions under this group −

•

•

REP − Used to repeat the given instruction till CX ≠ 0.

REPE/REPZ − Used to repeat the given instruction until CX = 0 or zero flag ZF = 1.

51

•

•

•

•

•

•

•

REPNE/REPNZ − Used to repeat the given instruction until CX = 0 or zero flag ZF =

1.

MOVS/MOVSB/MOVSW − Used to move the byte/word from one string to another.

COMS/COMPSB/COMPSW − Used to compare two string bytes/words.

INS/INSB/INSW − Used as an input string/byte/word from the I/O port to the

provided memory location.

OUTS/OUTSB/OUTSW − Used as an output string/byte/word from the provided

memory location to the I/O port.

SCAS/SCASB/SCASW − Used to scan a string and compare its byte with a byte in AL

or string word with a word in AX.

LODS/LODSB/LODSW − Used to store the string byte into AL or string word into

AX.

Program Execution Transfer Instructions (Branch and Loop Instructions)

These instructions are used to transfer/branch the instructions during an execution. It

includes the following instructions −

Instructions to transfer the instruction during an execution without any condition −

•

•

•

CALL − Used to call a procedure and save their return address to the stack.

RET − Used to return from the procedure to the main program.

JMP − Used to jump to the provided address to proceed to the next instruction.

Instructions to transfer the instruction during an execution with some conditions −

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

JA/JNBE − Used to jump if above/not below/equal instruction satisfies.

JAE/JNB − Used to jump if above/not below instruction satisfies.

JBE/JNA − Used to jump if below/equal/ not above instruction satisfies.

JC − Used to jump if carry flag CF = 1

JE/JZ − Used to jump if equal/zero flag ZF = 1

JG/JNLE − Used to jump if greater/not less than/equal instruction satisfies.

JGE/JNL − Used to jump if greater than/equal/not less than instruction satisfies.

JL/JNGE − Used to jump if less than/not greater than/equal instruction satisfies.

JLE/JNG − Used to jump if less than/equal/if not greater than instruction satisfies.

JNC − Used to jump if no carry flag (CF = 0)

JNE/JNZ − Used to jump if not equal/zero flag ZF = 0

JNO − Used to jump if no overflow flag OF = 0

JNP/JPO − Used to jump if not parity/parity odd PF = 0

JNS − Used to jump if not sign SF = 0

JO − Used to jump if overflow flag OF = 1

JP/JPE − Used to jump if parity/parity even PF = 1

JS − Used to jump if sign flag SF = 1

52

Processor Control Instructions

These instructions are used to control the processor action by setting/resetting the flag

values.

Following are the instructions under this group −

•

•

•

•

•

•

•

STC − Used to set carry flag CF to 1

CLC − Used to clear/reset carry flag CF to 0

CMC − Used to put complement at the state of carry flag CF.

STD − Used to set the direction flag DF to 1

CLD − Used to clear/reset the direction flag DF to 0

STI − Used to set the interrupt enable flag to 1, i.e., enable INTR input.

CLI − Used to clear the interrupt enable flag to 0, i.e., disable INTR input.

Iteration Control Instructions

These instructions are used to execute the given instructions for number of times.

Following is the list of instructions under this group −

•

•

•

•

LOOP − Used to loop a group of instructions until the condition satisfies, i.e., CX = 0

LOOPE/LOOPZ − Used to loop a group of instructions till it satisfies ZF = 1 & CX = 0

LOOPNE/LOOPNZ − Used to loop a group of instructions till it satisfies ZF = 0 & CX

=0

JCXZ − Used to jump to the provided address if CX = 0

Interrupt Instructions

These instructions are used to call the interrupt during program execution.

•

•

•

INT − Used to interrupt the program during execution and calling service specified.

INTO − Used to interrupt the program during execution if OF = 1

IRET − Used to return from interrupt service to the main program

53

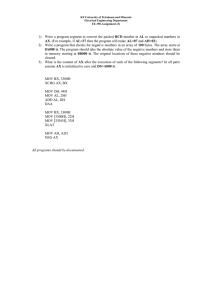

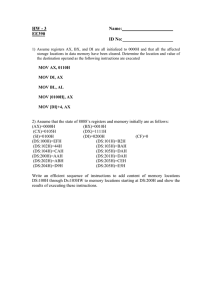

ADDITION

Address

Op-Code

Program

MOV AX,[3000]

Comments

Get the first data in AX reg

MOV BX, [3002]

Get the second data in BX reg

ADD AX,BX

Add the contents of both

the regs AX & BX

MOV [2000],AX

MOV [2002], CX

Store LSBs of sum.

Store MSBs of sum.

Stop the program

INT 3

OUTPUT

SUBTRACTION

Address

Op-Code

Program

Comments

MOV AX,[3000]

Get the first data in AX reg

MOV BX, [3002]

Get the second data in BX reg

SUB AX,BX

Subtract the contents of both

the regs AX & BX

MOV [2000],AX

MOV [2002], CX

INT 3

OUTPUT

54

Store LSBs of difference

Store MSBs of difference.

Stop the program

Exp No :

Date :

05

ALP Arithmetic programming

OBJECTIVE

To write an Assembly Language Program (ALP) for performing the Arithmetic operation of

two-byte numbers and to find factorial of a number.

APPARATUS REQUIRED:

SL.NO

1.

2.

ITEM

Microprocessor kit

SPECIFICATION

8086 kit

Power Supply

+5 V dc

QUANTITY

1

1

ALGORITHM

(i) 16-bit addition

(iii) Multiplication

of

16- bit

numbers

1. Get the multiplier.

2. Get the multiplicand

3. Initialize the product to 0.

4. Product = product + multiplicand

5. Decrement the multiplier by 1

6. If multiplicand is not equal to 0, repeat

from step (4) otherwise store the product.

1. Initialize the MSBs of sum to 0

2. Get the first number.

3. Add the second number to the f i r s t

number.

4. If

there

is

any

carry,

i n c r e m e n t MSBs of sum by 1

5. Store LSBs of sum.

6. Store MSBs of sum.

(ii) 16-bit subtraction

(iv) Division of 16-bit numbers.

1. Initialize the MSBs of difference to 0

2. Get the first number

3. Subtract the second number from

the first number.

4. If there is any borrow, increment

MSBs of difference by 1.

5. Store LSBs of difference

6. Store MSBs of difference.

1.

2.

3.

4.

5.

Get the dividend

Get the divisor

Initialize the quotient to 0.

Dividend = dividend – divisor

If t h e d i v i s o r i s g r e a t e r , s t o r e

the quotient. Go to step 6.

6. If dividend is greater, quotient =

Quotient + 1. Repeat from step (4)

7. Store the dividend value as

remainder

55

MULTIPLICATION

Address

Op-Code

Program

MOV AX,[3000]

MOV BX, [3002]

MUL BX

Comments

Get the first data

Get the second data

Multiply both

MOV [2000],AX

Store the lower order product

MOV [2002], CX

Store the higher order product

INT 3

Stop the program

OUTPUT

DIVISION

Address

Op-Code

Program

MOV AX,[1200]

Get the first data

MOV DX, [1202]

Get the second data

MOV BX, [1204]

Get Divider

DIV BX

Divide AX by BX

MOV [1206],AX

Store the lower order product

MOV AX,DX

Store quotient

MOV [1208],AX

Store the higher order product

INT 3

Stop the program

OUTPUT

56

Comments

FACTORIAL OF A NUMBER

RESULT:

57

Preparation

/10

Observation

/10

Viva

/10

Total

/30

ASCENDING

ADDRESS

OPCODES

START

PROGRAM

MOV AX,#8100

MOV DS,AX

MOV DX,COUNT

DEC DX

GO

MOV CX,DX

LEA SI,SERIES

NXT_BYTE

MOV AL,[SI]

CMP AL,[SI+1]

JB NEXT

XCHG AL,[SI+1]

XCHG AL,[SI]

NEXT

INC SI

LOOP NXT_BYTE

DEC DX

JNZ GO

MOV AH, 4CH

INT 3

OUTPUT:

ASCENDING

MEMORY

INPUT

DATA

OUTPUT

MEMORY

DATA

58

COMMENTS

Exp No :

Date :

06

Sorting

OBJECTIVE

To write an Assembly Language Program (ALP) to sort a given array in ascending

and descending order

APPARATUS REQUIRED

SL.NO

ITEM

SPECIFICATION

QUANTITY

1.

Microprocessor kit

8086 kit

1

2.

Power Supply

+5 V dc

1

ALGORITHM:

(i)

Sorting in ascending order:

a. Load the array counting two registers C1 and C2.

b. Get the first two numbers.

c. Compare the numbers and exchange if necessary so that the two numbers are in

ascending order.

d. Decrement C2.

e. Get the third number from the array and repeat the process until C2 is 0.

f. Decrement C1and repeat the process until C1 is 0.

(ii)

Sorting in descending order:

1. Load the array count in two registers C1 and C2.

2. Get the first two numbers.

3. Compare the numbers and exchange if necessary so that the two numbers are in

descending order.

4. Decrement C2.

5. Get the third number from the array and repeat the process until C2 is 0.

Decrement C1and repeat the process until C1 is 0.

59

DESCENDING

ADDRESS

OPCODES

LOOP 1

PROGRAM

MOV CX,#0008

COMMENTS

MOV AH,#00

MOV BX,#8100

LOOP 2

MOV AL,[BX]

INC BX

CMP AL,[BX]

JNC LOOP 3

JE LOOP 3

MOV DL,[BX]

DEC BX

MOV [BX],AL

MOV AH,01

LOOP 3

LOOP LOOP 2

CMP AH,00

JNE LOOP 1

INT 3

OUTPUT:

ASCENDING

MEMORY

INPUT

DATA

OUTPUT

MEMORY

DATA

60

RESULT:

61

Preparation

/10

Observation

/10

Viva

/10

Total

/30

PROGRAM:

Address

Op-Codes

Program

Comments

MOV SI, [8200]

MOV DI,[8300]

MOV CX,005

Rep

MOVSB

INT 3

OUTPUT

MEMORY ADDRESS

DATA-I

DATA-II

INPUT

OUTPUT

62

DATA III

Exp No :

Date :

07

Data Movement

OBJECTIVE

Write an ALP to Move a data block without overlap using 8086.

APPARATUS REQUIRED

SL.NO

1.

2.

ITEM

Microprocessor kit

SPECIFICATION

8086 kit

Power Supply

+5 V dc

QUANTITY

1

1

ALGORITHM

1. Initialize the memory location to the data pointer.

2. Increment B register.

3. Increment accumulator by1andadjust it to decimal every time.

4. Compare the given decimal number with accumulator value.

5. When both match, the equivalent hexadecimal value is in B register.

Store the resultant in memory location

RESULT:

63

Preparation

/10

Observation

/10

Viva

/10

Total

/30

PROGRAM TO GENERATE SQUARE WAVE

A0:

MOV AL,80

MOV DX,0FFC6

OUT DX

MOV DX,0FFC2

MOV AL,00

OUT DX

CALL DELAY 1

MOV AL,0FF

OUT DX

CALL DELAY2

JMP A0

DELAY 1:

MOV CX,0020

LOOP DELAY 1

RET

DELAY 2:

MOV CX,0020

LOOP DELAY 2

RET

OUT DX

64

Exp No :

Date :

08

Wave form generation

OBJECTIVE

Write an ALP to generate square wave form using 8255 PPI

APPARATUS REQUIRED

SL.NO

ITEM

1.

Microprocessor kit

2.

SPECIFICATION

QUANTITY

8086 kit

2

Power Supply

+5 V dc, 12V

1

3.

FRC Connector

-

1

4.

A/D, D/A interface module

-

1

5

CRO

-

1

6

Power mate connector

-

1

RESULT:

65

Preparation

/10

Observation

/10

Viva

/10

Total

/30

PROGRAM

3002

3000

3000

LE:

L1:

RPT:

L2:

L3:

CTRL

DAT

TBL:

DB

MOV

MOV

OUT

MOV

OUT

MOV

OUT

MOV

LOOP

MOV

OUT

MOV

MOV

MOV

OUT

MOV

MOV

OUT

MOV

LOOP

INC

DEC

JNZ

MOV

LOOP

INT

EQU 3002H

EQU 3000H

DB 3FH,06H,5BH,4FH

66H,6DH,7DH,07H

AL, 09H

DX, CTRL

DX, AL

AL, 31H

DX, AL

AL, D0H

DX, AL

CX, 0FFFFH

L1

AL, 01H

DX, AL

AH, 08

BX, OFFSET TBL

AL, 90H

DX, AL

AL,[BX]

DX, DAT

DX, AL

CX, 0FFFFH

L2

BX

AH

RPT

CX, 0FFFFH

L3

3

66

;control word

;data word

//LE 8 bit char. display

//clock dividing factor

//clear display

//wait till display is cleared

//control word for 8 chars

//left entry mode. 8 no. of chars

//will be displayed

//char displayed is stored

//control word for writing to

//display auto increment

// delay

Exp No :

Date :

09

Display the given message using 8279

OBJECTIVE

Write an ALP program to display the numeric numbers using 8086.

APPARATUS REQUIRED

SL.NO

ITEM

SPECIFICATION

QUANTITY

1.

Microprocessor kit

8086 kit

1

2.

Power Supply

+5 V dc

1

3.

Keyboard

-

1

RESULT:

67

Preparation

/10

Observation

/10

Viva

/10

Total

/30

A/D CONVERTER

D1:

MOV AL,90

MOV DX,0FFC6

OUT DX

MOV AL,07

MOV DX,FFC4

OUT DX

MOV AL,0F

MOV DX,0FFC6

OUT DX

MOV CX,3FFF

LOOP D1

D2:

MOV AL,0E

MOV DX,0FFC6

OUT DX

MOV AL,0C

MOV DX,0FFC6

OUT DX

MOV DX,0FFC0

IN DX

D3:

AND AL,80

CMP AL,80

JNZ D2

MOV AL,0D

MOV DX,0FFC6

OUT DX

MOV DX,0FFC0

IN DX

MOV DX,0FFC2

OUT DX

JMP D3

68

Exp No :

Date :

10

Interfacing analog to digital converter to 8086

OBJECTIVE

To write a program for conversion of analog data to digital output.

APPARATUS REQUIRED

SL.NO

ITEM

1.

Microprocessor kit

2.

SPECIFICATION

QUANTITY

8086 kit

2

Power Supply

+5 V dc, 12V

1

3.

FRC Connector

-

1

4.

A/D, D/A interface module

-

1

5

CRO

-

1

6

Power mate connector

-

1

69

70

PROCEDURE

❖ Connect the 26 core FRC connector to the 8086 trainer at connector no CN4 and the

interface module.

❖ Connect the power mate connector to the interface module and the other side of the

connector to the power supply. The connections to the power supply are given

below.

Connections: (power supply)

Black & Red: Gnd.

Blue & Green: +5V

❖ 5- Way power mate is wired to the motor. This power mate is to be inserted into the

male socket provided on the interface. Care should be taken such that, below given

code for the particular colored wire coincides with the code on the interface.

A- GREEN

C- RED & WHITE

B- GREEN & WHITE

D- RED

VDD - BLACK & WHITE.

❖ After the completion of the program and connections enter the program as given in

the listing below.

G0< STARTING ADDRESS< ENTER (on the key board of trainer).

RESULT:

71

Preparation

/10

Observation

/10

Viva

/10

Total

/30