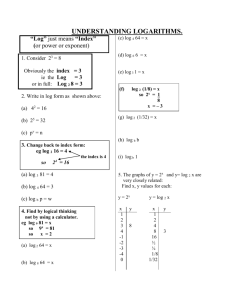

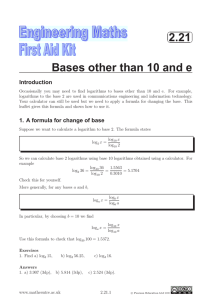

BJT AND FET FREQUENCY RESPONSES LOGARITHMS a = bx log a = x log b x = log a log b x = logb a • Logarithms taken to the base 10 are common logarithm. • Logarithms taken to the base e are a natural logarithms. Common Logarithms Natural Logarithms x = log10 a y = loge a LOGARITHMS • Properties • log10 1 = 0 • log10 a = log10 a – log10 b b • log10 1 = – log10 b b • log10 ab = log10 a + log10 b LOGARITHMS 1.) 𝑙𝑜𝑔𝑥 = 𝑙𝑜𝑔1 − 𝑙𝑜𝑔2 solution: [ 𝑙𝑜𝑔1 − 𝑙𝑜𝑔2 ]𝑙𝑜𝑔−1 Answer: X = 0.5 2.) 4000 𝑙𝑜𝑔10 250 Solution: [𝑙𝑜𝑔4000 − 𝑙𝑜𝑔250 ]𝑙𝑜𝑔−1 Answer: 16 3.) 𝑙𝑜𝑔2 𝑙𝑜𝑔3 = 𝑙𝑜𝑔3 2 Answer: 0.631 4.) 𝑙𝑜𝑔3 + 𝑙𝑜𝑔10 𝑙𝑜𝑔−1 Answer: 30 5.) 𝑙𝑜𝑔(0.6×30) Solution: [ 𝑙𝑜𝑔0.6 + 𝑙𝑜𝑔30 ]𝑙𝑜𝑔−1 Answer: 18 Ex. 1 Using the calculator, determine the logarithm of the following numbers. (a) log10 64. (b) loge 64. (c) log10 1600. (d) log10 8000. Ex. 2 Using the calculator, determine the logarithm of the following numbers to the base indicated. (a) log10 106. (b) loge e3. (c) log10 102. (d) loge e1. Answers: #1 (a)1.806 (b)4.159 (c)3.204 (d)3.903 Answers: #2 (a)2.03 (b)3 (c) 2 (d) 1 Ex. Express as a logarithm equation 1) 2) Answers: 1) 0.0373095 2) 2.20572 DECIBELS • The relationship of logarithm to power and audio levels • The term bel (B) was derived from the surname of Alexander Graham Bell GdB = 10 log10 P2 P1 GdBv = 20 log10 V2 V1 GdBm = 10 log10 P2 1 mW GdBi = 20 log10 I2 I1 GdB = log10 P2 P1 DECIBELS GdBT = GdB1 + GdB2 + GdBn G = G1 + G2 + … + Gn Examples: 1. Find the magnitude gain corresponding to the decibel gain of 100. Solution: GdB = 10 log10 P2 P1 100 = 10 log10 x x = log -1 10 x = 10000000000 DECIBELS 2. The input power to a device is 10 kW at a voltage of 1 kV. The output power is 500 W, while the output impedance is 20 Ω. Find the power gain in dB. Find the voltage gain in dB. Solution: GdB = 10 log10 P2 P1 = 10 log10 10 kW 500 W GdB = – 13.01 dB DECIBELS Solution: P = V2 R V2 = PR = [(500 W)(20 Ω)]1/2 V2 = 100 V GdBv = 20 log10 V2 V1 = 20 log 100 V 1 kV GdBv = – 20 dB DECIBELS 3. An amplifier rated at 40 W output is connected to a 10 Ω speaker. Calculate the input power required for full power output if the power gain is 25 dB. Calculate the input voltage for rated output if the amplifier voltage gain is 40 dB. Solution: GdB = 10 log10 P2 P1 25 = 10 log 40 W P1 2.5 = log 40 W P1 P1 = 40 W log -1 2.5 P1 = 126 mW DECIBELS Solution: P = V2 R V2 = PR = [(40 W)(20 Ω)]1/2 V2 = 20 V GdBv = 20 log10 V2 V1 40 dB= 20 log 20 V V1 2 = log 20 V V1 V1 = 20 V log -1 2 V1 = 200 mV Low Frequency Response – BJT Amplifier Xs = Rs + Ri , reactance Low Frequency Response – BJT Amplifier Vi = Vs Zi Rs + Zi Zi = Ri Xc = Rs + Zi ⦁ Effect of Cs on low frequency response fLS = 1 = 1 T 2𝛑CsXc fLS = 1 2𝛑(Rs + Zi) Cs Low Frequency Response – BJT Amplifier • Getting ac equivalent Zi Ri = R1//R2//βre Vi = Vs Zi Zi + Rs – jXcs Low Frequency Response – BJT Amplifier ⦁ Effect of Cc on low frequency response fLC = 1 2𝛑(RL + Ro) Cc Low Frequency Analysis • Can be established for each capacitive element and the frequency at which the output voltage drops to 0.707 of its maximum value. RC combination that will define a low cutoff frequency Low Frequency Analysis Vo = R Vi R + Xc Vo = R Vi (R2 + Xc2) ½ ; Xc = R Vo = R Vi (R2 + R2) ½ Vo = R Vi R(2) ½ Vo = 0.707 Vi Bode Plot • – 3dB drop in gain from the midband level when f = f1. An RC network will determine the low-frequency cut-off frequency for a BJT transistor Bode Plot Av = Vo Vi Vo = R Vi R – jXc Vo = 1 Vi 1 – jXc R Vo = 1 Vi 1 – 1 j2𝛑fC R Vo = 1 Vi 1 – jf1 ;f = f1 f Vo = 1 Vi 1 – j Vo = 1 V1 (1) 2 + (– 1) 2 Vo = 1 Vi (2) ½ Av = 0.707 Bode Plot Av = 20 log Vo Vi = 20 log 1 (1) 2 + (f1/f) 2 = 20 log [(1) 2 + (f1/f) 2 ] – ½ = – 10 log [(1) 2 + (f1/f) 2 ] – ½ = – 10 log (f1/f) 2 Av = – 20 log f1 f Bode Plot At f = f1 = 1; – 20 log 1 = 0 f = f1/2 = 2; – 20 log 2 = – 6 f = f1/4 = 4; – 20 log 4 = – 12 f = f1/10 = 10; – 20 log 10 = – 20 Bode Plot Junction Field Effect Transistor (JFET) Junction Field Effect Transistor (JFET) • A type of FET that operates with a reversed – biased control current in a channel. junction to Forward current transconductance (gm) ⦁ change in drain current (ΔID) for a given change in gate to source voltage (ΔVGS) with the drain to source voltage constant gm = ΔID ΔVGS Junction Field Effect Transistor (JFET) Forward Transfer Admittance ( gm0 or yfs) gm = gm0 1 – VGS VGS(OFF) gm0 = 2 IDSS |VGS(OFF)| ID = IDSS 1 – VGS VGS(OFF) 2 Depletion MOSFET (D – MOSFET) • The drain & source are diffused into the substrate material & then connected by a narrow channel adjacent to the insulated gate. n – channel p – channel JFET schematic symbols. A representation of the basic structure of the two types of JFET FET Amplifier • Common source amplifier. VDD FET Amplifier VGS Vi RG AC EQUIVALENT RD//RL FET Amplifier FET equivalent Circuit Av = Vo Vi = Vds Vgs = IdRd Id gm Av = gmRd FET Amplifier Av = gm (Rd //r’ds) Including drain to source resistance Effect of Source Resistance on Gain Av = gmRd 1 + gmRs Av = Vo Vi = Vds Vgs + IdRs = IdRd Id + IdRs gm = IdRd Id 1 + Rs gm = Rd gmRs + 1 gm Effect of Source Resistance on Gain Examples: 1. The JFET has a gm=4mS w/ external ac drain resistance of 1.5K Ω , is the ideal voltage gain? Solution: Av = gmRd = (4 mS)(1.5 kΩ) Av = 6 Effect of Source Resistance on Gain 2. A FET equivalent circuit is shown. Determine the voltage gain when the output is taken across Rd. Neglect r’ds. Rd = 1.5 kΩ gm = 4 mS Solution: Av = gmRd 1 + gmRs = (4 mS)(1.5 kΩ) 1 + (4 mS)(560 Ω) Av = 1.85 Bypassed Source Resistance Zi = RG Zo = RD Av = gm (Rd//RL) For unbypassed: Av = gm (Rd//RL) 1 + gmRs JFET Self – Bias Configuration JFET Self – Bias Configuration Redrawn rd = 1 yos Zi = RG Zo = rd //Rd JFET Self – Bias Configuration Example: 1. The fixed bias configuration has an operating point defined by VGSQ = – 2 V and IDQ = 5.625 mA with IDSS = 10mA & VP= – 8 V, The network should be redrawn with an applied signal Vi. The Value of yos is provided as 40µS. Calculate: a. gm d. Zo b. rd e. Av c. Zi f. Av if rd is ignored JFET Self – Bias Configuration 20 V 2 kΩ Vi 1 MΩ 2V IDSS = 10 mA Vp = – 8 V JFET Self – Bias Configuration Solution: a. gm0 = 2 IDSS |VGS(OFF)| = 2 (10 mA) 8V gm0 = 2.5 mS gm = gm0 1 – VGS VGS(OFF) = (2.5 mS) 1 – (– 2) –8 gm = 1.875 mS JFET Self – Bias Configuration Solution: b. rd = 1 yos = 1 40 µS rd = 25 kΩ c. Zi = RG Zi = 1 MΩ d. Zo = rd //Rd = 25 kΩ//2 kΩ Zo = 1.85 kΩ JFET Self – Bias Configuration Solution: e. Av = gm (Rd//rd) = (1.88 mS) (1.85 kΩ) Av = 3.48 f. Av = gmRd = (1.88 mS)(2 kΩ) Av = 3.76