SR Flip Flop Fundamentals: NOR Gate, Clocked, Waveforms

advertisement

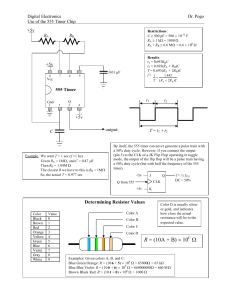

SR Flip Flop Fundamentals: Slide 2 NOR Gate SR Flip Flop. Slide 3 SR Flip Flop. Slide 4 SR Flip Flop with a positive edge clock: Slide 5 SR Flip Flop with a negative edge clock: Slide 6 Flip Flop waveform diagrams: NOR Gate SR Flip Flop : The cross-coupled NOR gates creates an SR Flip Flop. Flip Flops are the basic elements used in computer memory. The S input is called Set. The R input is called Reset. R 01 01 00 1 10 0 11 0 01 0 S 11 0 00 1 00 1 Q Q Q settles at logic 0 Q changes Both outputs from 1 to 0. Q changes settle to 0. 1. Called from 0 the to This breaks the reset ! Calledmode the Set definition. This mode! condition is not allowed S R Output 0 0 No Change Q stays at 0 0 1 Reset: Q changes to 0 Set: Q changes to 1 1 0 1 1 Ambiguous : Not allowed! Output Q and Q are by definition always opposite to each other. If Q=1 then Q =0. Behaviour Table: Logic gates are defined by Truth Tables. Flip Flops are defined by behaviour tables. Two different names for tables that do essentially the same job. To generate the behaviour table you must assume an initial condition at output Q. This is necessary because the outputs are wired to the inputs. This creates a feedback path that can only be analyzed when a starting point is assumed. Start Nextwith S,R = S,R1,1 0,1 1,0 = :0,0 The : The analysis analysis procedure procedure works works as follows: as follows: 1-Place 1-Placethe theinitial initialconditions conditionsatatoutput outputQQon onthe thediagram. diagram.Assume AssumeQQ=0. =1. =0. 2-Place 2-Placethe theinput inputconditions conditionsatatSSand andR.R. 3-Analyze 3-Analyzethe thetop topNOR NORgate gateand andrecord recordQ. Q. 4-Analyze 4-Analyzethe thebottom bottomNOR NORgate gateand andrecord recordQ. Q. 5-Repeat 5-Repeatsteps steps33and and44until untilQQand andQQsettle. settle. Slide #2 Cross-coupled NOR gates create an SR Flip Flop. It is easy to remember the operation of an SR flip flop using only the symbol without repeatedly analyzing the cross coupled NOR gate system. 10 0 S Q 00 1 R Q 10 0 1 Assume Output Output Q reset does reset SETs Q SETs not starts : :QQ : =1. change :Q=1. at Q=0. =0. 0. 01 1 0 Symbol The S input is called SET the R input is called reset. They are both active high. Active high means that S =1 sets the flip flop (S =0 does not set). R =1 resets the flip flop (R =0 does not reset). SET means set output Q to “1”. RESET means reset output Q to “0”. When S =0 and R =0 then Q does not change. Q holds its logic level (1 or 0). It is equivalent to not issuing either the set or the reset command. : :Hold S=1 Hold : Set R=1 Mode Mode Mode : :: : reset Mode : When S =1 and R =1 then Q is ambiguous. Both Q and Q outputs go to the same logic level which breaks the definition of a flip flop. You can think of it this way … S =1 says SET and R =1 says reset. The flip flop does not know whether the output should be Q =1 or Q =0. S=R=1 should never be used! There is a second variety of SR flip flop that uses an active low S and R inputs. The internal system is cross coupled NAND gates. Active low means that S =0 sets the flip flop (S =1 does not set). R =0 resets the flip flop (R =1 does not reset). 0 1 S Q 1 0 1 R Q S=0 ::reset Set Mode R=0 : HOLD Mode Mode:: : Slide #3 1 Output 0 Assume Q does SETs Qnot starts : Qchange =1. at 0. 0 1 When S =1 and R =1 then Q does not change. Q holds its logic level (1 or 0). It is equivalent to not issuing either the set or the reset command. When S =0 and R =0 then Q is ambiguous. The flip flop does not know whether the output should be Q =1 or Q =0. S=R=0 should never be used! SR Flip Flop with a Positive Edge Triggered Clock Input : A Positive EDGE triggered flip flop has a new input called clock. The clock requires a transition from 0 to 1 in order that S and R controls output Q. Holding a constant logic 1 or a constant logic 0 at the clock input does not allow SR to change output Q. An edge triggered clock is identified with “>Clk” on the symbol. 1 0 S Q >Clk R Q 0 Assume 1 Output SETs Q starts : Q =1. at 0. 1 0 A transition from 0 to 1 at “>Clk” is required in order for the flip flop to respond to S and R. This is called a” Positive Edge”. Watch the animation to see how you would set the flip flop. Holding “>Clk” at logic 1 will not result in S and R controlling Q. Only the 0 to 1 transition at “>Clk“ causes the output Q to change. SR Flip Flop with edge triggered clock S=1 : Set Mode : Inside the SR Flip Flop with Positive Edge Triggered Clock: The clock signal is applied to the input. 1/0 S >Clk 1 1/0 R 0 2 1/0 0 S Q 3 1/0 0 R Q The NOT gate delays the signal because it has a propagation delay. Propagation delay is the reaction time of the inverter. Let’s use 3 to 10 nanoSec. 3 to 10 nanoSec delay. During the 3 to 10 nanoSec interval, AND gate #1 outputs a 1. AND gates #2 and #3 transfer the logic levels to internal SR and Q responds. Slide #4 After the 3 to 10 nanoSec interval AND gate #1 outputs a 0. AND gates #2 and #3 transfer the logic 0 to internal SR and Q holds(S=R=0 is Hold mode). To re-clock the flip flop you need another positive edge. Clock must return to 0 and re-change back to 1. SR Flip Flop with a Negative Edge Triggered Clock Input : A negative edge triggered flip flop requires a transition from 1 to 0 at at the clock input in order for the flip flop to respond to S and R. This is called a” Negative Edge”. It is the opposite of a positive edge triggered flip flop. An edge triggered clock is identified with “o|>Clk” on the symbol. 1 0 S Q >Clk R Q 0 Assume 1 Output SETs Q starts : Q =1. at 0. 1 0 Watch the animation to see how you would set the flip flop. Holding “o|>Clk” at logic 0 will not result in S and R controlling Q. Only the 1 to 0 transition at “o|>Clk“ causes the output Q to change. SR Flip Flop with edge triggered clock S=1 : Set Mode : Here is a summary of the flip flop devices S R Q Q S R Q S Q >Clk R Q Non-Clocked SR S and R control the response at Q continuously. Slide #5 Q S Q >Clk R Q Edge Triggered S and R control the response at Q only when Clk is making a transition. On the edge of the clock signal. Note Pack 5 : Flip Flop Waveform Diagrams : To draw waveforms for flip flops you need to begin with an initial condition at Q, mark the area where the clock input is asserted and then draw the output response. Let’s use an initial condition of Q =0. The initial condition Q =0 is marked as a dot on the output waveform diagram. Set The flip flop has a negative edge triggered clock. The clock is asserted when Clk makes a transition from 1 to 0. The asserted zone is marked off in yellow. Reset Clock Analyze the waveform and draw Q. S Q >Clk R Q Untilthis On thenegative clock changes edge S=1 S=R=0: fromand 1 to No R=0: 0Change it SET is NOT Mode. Mode. asserted. Thus Q sets holdstoat1.0.No Noanalysis analysisisisrequired requireduntil untilthe next next negative edge. Slide #6