Analog to RF Design: Circuits, Constraints, and Techniques

advertisement

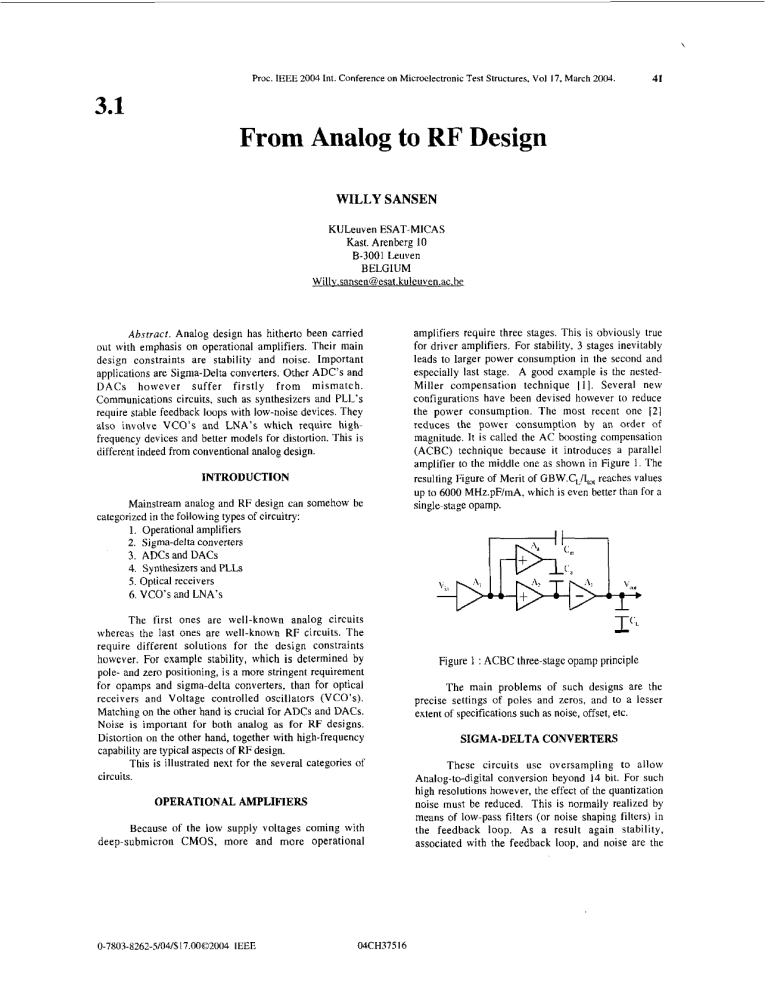

\ Proc. IEEE 2004 Int. Conference an MicroelectronicTest Structures, Vol 17, March 2004. 41 3.1 From Analog to RF Design WILLY SANSEN KULeuven ESAT-MICAS Kast. Arenberg 10 B-3001 Leuven BELGIUM Willv.sansen@esat.kuleuven.ac.he Absrracr. Analog design has hitherto been carried out with emphasis on operational amplifiers. Their main design constraints are stability and noise. Important applications are Sigma-Delta converters. Other ADC’s and DACs however suffer firstly f r o m mismatch. Communications circuits, such as synthesizers and PLL’s require stable feedback loops with low-noise devices. They also involve VCO’s and LNA’s which require highfrequency devices and better models for distortion. This is different indeed from conventional analog design. INTRODUCTION Mainstream analog and RF design can somehow he categorized in the following types of circuitry: 1. Operational amplifiers 2. Sigma-delta converters 3. ADCs and DACs 4. Synthesizers and PLLs 5. Optical receivers 6. VCO’s and LNA’s The first ones are well-known analog circuits whereas the last ones are well-known RF circuits. The require different solutions for the design constraints however. For example stability, which is determined by pole- and zero positioning, is a more stringent requirement for opamps and sigma-delta converters, than for optical receivers and Voltage controlled oscillators (VCO’s). Matching on the other hand is crucial for ADCs and DACs. Noise is important for both analog as for RF designs. Distortion on the other hand, together with high-frequency capability are typical aspects of RF design. This is illustrated next for the several categories of circuits. OPERATIONAL AMPLIFIERS Because of the low supply voltages coming with deep-submicron CMOS, more and more operational 0-7803-8262-5/04/$17.0002004 IEEE 04CH37516 amplifiers require three stages. This is obviously true for driver amplifiers. For stability, 3 stages inevitably leads to larger power consumption in the second and especially last stage. A good example is the nestedMiller Compensation technique II ] . Several new configurations have been devised however to reduce the power consumption. The most recent one 121 reduces the power consumption by an order of magnitude. It is called the AC boosting compensation (ACBC) technique because it introduces a parallel amplifier to the middle one as shown in Figure I . The resulting Figure of Merit of GBW.CL/I,,,, reaches values up to 6000 MHz.pF/mA, which is even better than for a single-stage opamp. Figure 1 : ACBC three-stage opamp principle The main problems of such designs are the precise settings of poles and zeros, and LO a lesser extent of specifications such as noise, offset, etc. SIGMA-DELTA CONVERTERS These circuits use oversampling to allow Analog-to-digital conversion beyond 14 bit. For such high resolutions however, the effect of the quantization noise must be reduced. This is normally realized by means of low-pass filters (or noise shaping filters) in the feedback loop. As a result again stability, associated with the feedback loop, and noise are the 42 main design constraints. For IOW power consumption the oversampling ratio must be minimized, requiring higherorder low-pass filters, which may impair the stability. Therefore single-loop filters better be avoided leading to 21-1 and 2-2 mash configurations. Another problem of these sampled-data filters is that for supply voltages below 1.8 V , it is no more possible to use pass transistors as switches. Rather than to use voltage boosters which stress the thin gate oxides, the operational amplifier itself can take up the switching function [3] giving rise to very low power converters. As a conclusion it can be stated that noise reduction is the major problem in high-resolution sigma-delta converters. Because of the high-order feedback loop, stability can be a problem as well. result stability and noise are the main constraints in such design, similarly as for sigma-delta converters. For example to reach sufficiently low phase noise such as < -100 dBc/Hz at 100 kHz distance, a third-order low-pass filter is required giving rise to a 4 I h order PLL. This feedback loop can only be made stable provided a zero is introduced which doesn’t give additional noise [5]. Such filter is sketched in Figure 2 together with its Bode diagram. ADC’s AND DAC’S Both ADC’s and DAC’s suffer from a lack of matching. For example charge redistribution DAC’s rely on the matching of a hank of capacitances, which can easily reach matching to 0.02 %. This results in resolutions of 5000 or about 12 hit. Current steering DAC’s on the other hand rely on matching of current sources, for which 10 bits is more common. The resolution can be predicted quite accurately provided the matching parameters Ag and A,, are known. They are about Ag = 2 %pm A,, = 1 mVpm per nm f, (= U50) (1) Which is about 2.6 mVpm for a 0.13 pm CMOS technology, or 7 mVpm for a 0.35 pm CMOS technology. In this latter technology a lGS/s 10 bit DAC has been reported [4]. Matching is also the main limitation for most ADC’s. For example in charge redistribution ADC’s hut also in flash ADC’s and pipeline ADC’s matching establishes the limitations. It thus comes as no surprise that the minimum power required to carry out an Analog-todigital conversion for a specific signal frequency is proportional to the dynamic range required. This minimum is two orders of magnitude higher when mismatch is taken into account than when thermal noise is taken into account. As a result mismatch is the real limit for the design of high performance ADC’s and DAC’s. PLL’S AND SYNTHESIZERS PLL based receivers and synthesizers require high spectral purity not mix up the adjacent channels. As a result the phase noise or jitter must be minimized. This requires a PLL with a higher-order low-pass filter to minimize the noise. but with sufficient phase-margin for stability. As a Figure 2 : (a) 3-order low-pass filter to reduce noise; (h) the required Bode diagram for stability. The synthesis of this zero in a noiseless way is essential to reach the low phase noise required. A PLL with a fractional divider is the core of any multi-channel synthesizer. To avoid spurious signals in the high-frequency output. a sigma-delta converter is required to drive the divider as shown in 43 Figure 3 161. Again a high-order low-pass filter must reduce the noise as much as possible. Again stability and noise have to be traded off. Divider fTrat ' = vsa! 2rr: (2) in which vssc = IO' cm/s is the saturation velocity. It is clear that for a channel length of 90 nm,an fT can be expected beyond 100 GHz, which will push CMOS even further towards RF applications ! Transimpedance amplifiers greatly benefit from such high fT values, slowly replacing most bipolar transimpedance amplifiers by CMOS ones. A direct comparison shows that both the highest frequency performance and the lowest noise can be achieved by means of the voltage input amplifier, not the current input one. VCO'S AND LNA'S TRANSIMPEDANCE AMPLIFIERS Optical receivers require transimpedance amplifiers to convert the weak photodiode currents into voltages with logic levels. Voltage amplifiers can be used or current amplifiers. Both however have to reach as high frequencies as possible and with minimum noise. High performance is obviously reached for minimum channel lengths. Below 0.35 pm channel length the maximum fT of MOSTs is already dominated by velocity saturation as shown in Figure.4. Frequency fT is for a conventional model; fT,,, with velocity saturation and f , is for a current mirror (B=I). The best known RF circuits are Voltage controlled oscillators (VCO's) and Low-noise amplifiers (LNA's). Both require the highest frequency devices possible and low noise. Moreover the LNA requires at the same time low distortion. VCO's are normally symmetrical (Figure 5 ) . The frequency U& is set by the inductor with the diode capacitances. Tuning is thus possible by means of voltage V,. The two cross-coupled transistors provide a negative resistance which must compensate the loss resistance RL of the inductors. The minimum current consumption is thus given by g, = RL (CD %I2 (3) Since this resistance also determines the phase noise, it is clear that it is vital to be able to realize spiral inductors with as little series resistance as possible. 100 I (GHr) 10 1 1 1 L(mlcron) IO 'OUT ~~~ 'OUT Figure 4. Maximum fr values of MOSTs versus channel length Frequency fTsa,is given by Figure 5: High-frequency VCO 44 Bonding wires have been used hut also micromachined inductors. Nowadays mainly aluminum inductors are used with careful optimization of the line width, the spacing, etc. As a result low phase noise (less than -100 dBc/Hz at 100 kHz) are readily obtained, even with tuning ranges of up to 30 90. LNA’s are the first amplifiers of receivers. They have to be able to amplify high-frequency small signals with low noise but they must be able to handle large - input . signals with little crossmodulation distortion. They have to be carefully optimized, despite the fact that only a few transistors are used (Figure 6). Moreover the ESD protection must be part of the design [7]. This greatly complicates the impedance matching and the noise matching at the input. vss Figure 6: LNA for receiver Normally low distortion is reached by the choice of a large value of (VGs-VT). However because of the onset of velocity saturation, a point of zero third-order intermodulation distortion can be found, just above the threshold voltage. This capability will certainly more exploited in the future, when velocity saturation sets in even for lower V,, values. CONCLUSION RF circuits differentiate form conventional analog circuits in the sense that they require more attention for high frequency performance and for distortion. Requirements such as low-noise and matching continue to play an important role. Moreover feedback loops of any kind such as i n operational amplifiers, sigma-delta converters and PLL’s must obviously always be made stable. REFERENCES J. Huijsing, ..” Low-voltage operational amplifiers with rail-to-rail input and output ranges”, Journal Solid-State Circuits, Dec. 1985, 1 1 4 4 1 150. X. Peng, .., AC Boosting compensation schema for low-power multistage amplifiers, Journal Solid-State Circuits, 2004 E. Peluso, ..,” A 900 mV low-power DeltaSigma AID converter with 77 dB dynamic range ”, Journal Solid-State Circuits, Dec. 1998, 1887-1897 and wkap.nl. A. Van den Bosch, ... “A IO-hit I-Gsample/s Nyquist Current-steering CMOS D/A Converter“ Journal Solid-State Circuits March 2001, 315-324 and wkap.nl. J. Craninckx, ... “A fully integrated CMOS DCS- 1800 frequency synthesizer”, Journal Solid-State Circuits , Dec.1998, 2054-2065 and wkap.nl 6, B. De Muer, “A CMOS Monolithic DeltaSigma controlled fractional-N Frequency Synthesizer for DCS-1800”, Journal Solid-State Circuits, July 2002,835-844 and wkap.nl. 7. P. Leroux, ... “A 0.8 dB NF ESD protected 9 mW CMOS LNA operating at 1.23 Ghz”, Journal Solid-State Circuits, June 2002, 760765. 1