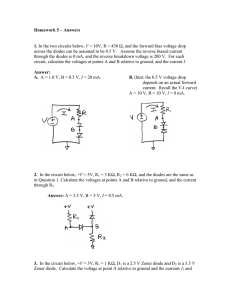

ELEC - 01211 Electronic Devices and Circuits Objective: The objective of this course is to teach the principle, operation and characteristics of various electronic devices and their applications in electronic circuits. CHAPTER 1: Semiconductor Diodes CHAPTER 2: Diode Applications CHAPTER 3: Bipolar Junction Transistors(BJTs) CHAPTER 4: DC Biasing – BJTs CHAPTER 5: BJT AC Analysis CHAPTER 6: Field-Effect Transistors(FETs) CHAPTER 7: FET Biasing CHAPTER 8: FET Amplifiers 1 ELEC - 02211 ELECTRONIC DEVICES AND CIRCUITS CHAPTER # 1 SEMICONDUCTOR DIODES Prof. Dr. Muhammad Amjad University College of Engineering and Technology The Islamia University of Bahawalpur, Pakistan CHAPTER OUTLINE 1) 2) 3) 4) 5) 6) 7) 8) 9) 10) 11) 12) 13) 14) 15) 16) Introduction Semiconductor Materials: Ge, Si, and GaAs Covalent Bonding and Intrinsic Materials Energy level Extrinsic Materials: n-Type and p-Type Materials Semiconductor Diode Ideal versus practical Resistance levels Diode Equivalent Circuits Transition and Diffusion Capacitance Reverse Recovery Time Diode Specification Sheets Semiconductor Diode Notation Diode Testing Zener Diodes Light-Emitting Diodes 3 ATOMIC STRUCTURE Valence shell (4 valence electrons) Valence shell (4 valence electrons) Valence electron shells + + Valence electron Nucleus orbiting electrons Germanium 32 orbiting electrons (Tetravalent) orbiting electrons Silicon 14 orbiting electrons (Tetravalent) 4 ATOMIC STRUCTURE Valence shell (3 valence electrons) Valence electron shells Valence shell (5 valence electrons) shells + Nucleus + orbiting electrons Gallium 31 orbiting electrons (Trivalent) Valence electron Nucleus orbiting electrons Arsenic 33 orbiting electrons (Pentavalent) 5 COVALENT BONDING Covalent bonding of Si crystal This Covalent bonding of GaAs crystal bonding of atoms, strengthened by the sharing 6 of electrons, is called covalent bonding. TABLE: INTRINSIC CARRIERS The term intrinsic is applied to any semiconductor material that has been carefully refined to reduce the number of impurities to a very low level. The electrons in a material due only to external causes (light energy in the form of photons and thermal energy in the form of heat from surrounding medium) are referred to as intrinsic carriers. Semiconductor GaAs Intrinsic carriers/cm3 1.7 X 106 Si 1.5 X 1010 Ge 2.5 X 1013 RELATIVE MOBILITY mn Relative mobility is the ability of free carriers to move throughout the material. Semiconductor mn (cm2/V.s) Si 1500 Ge 3900 GaAs 8500 8 TEMPERATURE COEFFICIENTS Semiconductors have Negative Temperature Coefficient Conductors have Positive Temperature Coefficient 9 ENERGY LEVELS 10 FIGURE 1-6A ENERGY LEVELS: DISCRETE LEVELS IN ISOLATED ATOMIC STRUCTURES. ENERGY LEVELS ENERGY LEVELS: CONDUCTION AND VALENCE BANDS OF AN INSULATOR; SEMICONDUCTOR; AND CONDUCTOR. 11 ENERGY LEVELS Between two bands there is an energy gap that the electron in the valence band must overcome to become free carrier. The difference in energy gap requirements reveals the sensitivity of each type of semiconductor to changes in temperature. It has negative and positive effects. Photo detectors sensitive to light and security systems sensitive to heat would be an excellent area of application for Ge devices. For transistor networks stability is high priority, the sensitivity to temperature or light can have adverse effects. 12 Energy gap reveals which element is useful for the construction of Light Emitting Diodes (LEDs). EXTRINSIC MATERIALS A semiconductor material that has been subjected to the doping process is called an extrinsic material. Type of extrinsic materials n-type p-type 13 DOPANT Group VA (n-type) – usually antimony (Sb), arsenic (As), phosphorus (P) Group IIIA (p-type) – usually Boron (B), Gallium (Ga) and Indium (In) 14 n-TYPE MATERIAL Diffused impurities with five valence electron are called donor atoms. 15 ANTIMONY IMPURITY IN N-TYPE MATERIAL. Effect of donor impurities on the energy band structure 16 p-TYPE MATERIAL Diffused impurities with three valence electron are called acceptor atoms. BORON IMPURITY IN P-TYPE MATERIAL. 17 ELECTRON VERSUS HOLE FLOW The valence electron acquires sufficient kinetic energy to break its covalent bond and fills the void created by hole. When the electron move to fill the hole therefore a transfer of holes to the left and electrons to the right. This flow is known as conventional flow. 18 MAJORITY AND MINORITY CARRIERS n-type material, the electron is called majority carrier and hole the minority carrier. p-type material, the hole is called majority carrier and electron the minority carrier. 19 NO APPLIED BIAS (V = 0V) This region of uncovered positive and negative ions is called the depletion region due to the “depletion” of free carriers in this region. P-N JUNCTION WITH NO EXTERNAL BIAS. 20 REVERSE BIAS CONDITION (VD < 0V) External voltage is applied across the p-n junction in the opposite polarity of the p- and n-type materials. The current that exist under reverse-bias condition is called reverse saturation current (IS). REVERSE-BIASED P-N JUNCTION. The reverse voltage causes the depletion region to widen. The electrons in the n-type material are attracted toward the positive terminal of the voltage source. The holes in the p-type material are attracted toward the negative terminal of the voltage source. 21 FORWARD-BIAS CONDITION (VD > 0V) External voltage is applied across the p-n junction in the same polarity as the p- and n-type materials. The forward voltage causes the depletion region to narrow. The electrons and holes are pushed toward the p-n junction. The electrons and holes have sufficient energy to cross the p-n junction. 22 FORWARD-BIASED P-N JUNCTION. NO APPLIED BIAS (V = 0V) REVERSE BIAS CONDITION (VD < 0V) FORWARD BIAS CONDITION (VD > 0V) 23 http://www.st-andrews.ac.uk/~www_pa/Scots_Guide/info/comp/passive/diode/diode.htm http://www.ee.byu.edu/cleanroom/pn_animation.phtml SHOCKLEY’S EQUATION I D I S (e VD nVT 1) IS = Reverse saturation current VD = Applied forward bias voltage across the diode n = An ideality factor, which is a function of the operating condition and Physical construction (n = 1 will be assumed throughout the book) VT = Thermal voltage (an electrostatic voltage across the PN junction) VT kT q k = Boltzmann’s constant = 1.38×10-23 J/K T = Absolute temp. in kelvins = 273 + temp in 0C q = Magnitude of electronic charge = 1.6×10-19 C 24 EXAMPLE 1.1 A. AT TEMP OF 27 0C, DETERMINE THE THERMAL VOLTAGE VT. B. REPEAT FOR 100 0C. VT kT q a. VT = 26 mV b. VT =32.17 mV 25 SHOCKLEY’S EQUATION I D I S (e ID ISe VD nVT VD nVT ID ISe I D I S 1) IS VD nVT (VD positive) (VD negative) I D I S (e 1) 0mA 0 (VD zero) 26 SILICON SEMICONDUCTOR DIODE CHARACTERISTICS Deviation: Internal body resistance External contact resistance of diode Generation of carriers in depletion region Surface leakage currents 27 PLOT OF e x 28 ZENER REGION Zener Potential Zener Breakdown (0 to -5V) Avalanche Breakdown (-5 to above) Zener Diode PIV or PRV The reverse bias potential that results in the dramatic change in characteristics is called the Zener potential. The max reverse-bias potential that can be applied before entering the Zener region is called the peak inverse voltage PIV or PRV. 29 COMPARISON OF Si, Ge AND GaAs SEMICONDUCTOR DIODES Knee Voltages VK Ge 0.3V Si 0.7V GaAs 1.2V 30 TEMPERATURE EFFECTS In the forward-bias region the characteristic of a silicon diode shift to the left at a rate of 2.5 mV per centigrade degree increase in temperature. In the reverse-bias region the reverse saturation current of a silicon diode doubles for every 100C rise in temperature. 31 VARIATION IN DIODE CHARACTERISTICS WITH TEMPERATURE CHANGE 32 The Current Commercial use of Ge, Si and GaAs Ge: Used in some high speed applications (due to high mobility) and applications that use its sensitivity to light and heat such as photo detectors and security systems. Si: Semiconductor used most frequently for the full range of electronic devices. Advantage of available at low cost and relatively low reverse saturation current, good temperature characteristics and excellent breakdown voltages. GaAs: Its high speed characteristics are in more demand every day, with the all features that Si material 33 have. IDEAL VERSUS PRACTICAL 34 IDEAL VERSUS PRACTICAL FIGURE 1.22: Ideal versus actual semiconductor characteristics 35 RESISTANCE LEVELS As the operating point of a diode moves from one region to another the resistance of the diode will also change due to the non-linear shape of the characteristic curve. i. DC or Static Resistance ii. AC or Dynamic Resistance iii. Average AC Resistance 36 DC or Static Resistance The application of a dc voltage to a circuit containing a semiconductor diode will result in an operating point on the characteristic curve that will not change with time. The resistance of the diode at the operating point can be found simply by finding the corresponding levels of VD and ID. RD VD ID Higher the current through a diode, the lower is the dc resistance level. 37 DETERMINING THE DC RESISTANCE OF A DIODE AT A PARTICULAR OPERATING POINT. EXAMPLE 1.2. DETERMINE THE DC RESISTANCE LEVEL FOR THE DIODE a. b. c. ID = 2mA(low level) ID = 20mA(high level) VD = -10V(reverse-biased) RD VD ID a. RD = 250 Ω b. RD = 40 Ω c. RD = 10 MΩ 38 AC or Dynamic Resistance The varying input will move the instantaneous operating point up and down a region of the characteristics and thus defines a specific change in current and voltage. With no applied varying signal, the point of operation would be the Q-point appearing. Vd rd I d The lower Q-point of operation (smaller current or lower voltage), the higher is the resistance. 39 DEFINING THE DYNAMIC OR AC RESISTANCE. AC or Dynamic Resistance rd Vd I d 40 DETERMINING THE AC RESISTANCE AT A Q-POINT. EXAMPLE 1.3. a. Determine the ac resistance at ID=2mA b. Determine the ac resistance at ID=25mA c. Compare the results of part (a) and (b) to the dc resistances at each current level. a. ∆Id = 4mA - 0mA = 4mA ∆Vd= 0.76V - 0.65V = 0.11V rd = 27.5 Ω b. ∆Id = 30mA - 20mA = 10mA ∆Vd = 0.8V - 0.78V = 0.02V rd = 2 Ω c. RD = VD / ID = 0.7V/2mA = 350 Ω RD = VD / ID = 0.79V/25mA = 31.62 Ω rd Vd I d 41 AC or Dynamic Resistance The derivative of a function at a point is equal to the slope of the tangent line drawn at that point. 42 AC or Dynamic Resistance VT kT 26 mV q n 1 The dynamic resistance can be found simply by substituting the quiescent value of the diode current into the equation. Where rB is the (body resistance + contact resistance) Now in example 1.3, rD = 26mV/ID = 26mV/25mA = 1.04 Ω As rD = 2 Ω The difference of 1Ω could be treated as contribution of rB. 43 Average AC Resistance If the input signal is sufficiently large to produce a broad swing, the resistance associated with the device for this region is called the average ac resistance. The resistance determined by a straight line drawn between the two intersections established by the max and min values of the input voltage. ∆Id = 17mA - 2mA=15mA ∆Vd=0.725V-0.65V=0.075V rav = 5 Ω 44 DETERMINING THE AVERAGE AC RESISTANCE BETWEEN INDICATED LIMITS. SUMMARY RESISTANCE LEVELS 45 DIODE EQUIVALENT CIRCUITS An equivalent circuit is a combination of elements properly chosen to best represent the actual terminal characteristics of a device or system in a particular operating region. Once the equivalent circuit is defined, the device symbol can be removed from a schematic and the equivalent circuit inserted in its place without severely affecting the actual behavior of the system. i. Piecewise-Linear Equivalent Circuit ii. Simplified Equivalent Circuit iii. Ideal Equivalent Circuit 46 Piecewise-Linear Equivalent Circuit An equivalent circuit for a diode to approximate the characteristics of the device by straight-line segment, is called a piecewise-linear equivalent circuit. 47 Simplified Equivalent Circuit The resistance rav is sufficiently small to be ignored in comparison to the other elements of the network. SIMPLIFIED EQUIVALENT CIRCUIT FOR THE SILICON SEMICONDUCTOR DIODE. 48 Ideal Equivalent Circuit If 0.7 V level can be ignored in comparison to the applied voltage level. IDEAL DIODE AND ITS CHARACTERISTICS. 49 SUMMARY TABLE DIODE EQUIVALENT CIRCUITS 50 TRANSITION AND DIFFUSION CAPACITANCE Every electronic device is frequency sensitive. 1 XC Z R jX X L 2fL 2fC In reverse-bias region we have transition (CT) or depletion region capacitance In forward-bias region we have diffusion (CD) or storage capacitance A C d Capacitance 51 TRANSITION AND DIFFUSION CAPACITANCE TRANSITION AND DIFFUSION CAPACITANCE VERSUS APPLIED BIAS FOR A SILICON DIODE. 52 TRANSITION AND DIFFUSION CAPACITANCE The fact that the capacitance is dependent on the applied reversebias potential has application in a number of electronic systems. In fact, varactor diode operation is wholly dependent on this phenomenon. This capacitance, called the transition (CT), barriers, or depletion region capacitance, is determined by where C(0) is the capacitance under no-bias conditions and VR is the applied reverse bias potential. The power n is 1⁄2 or 1⁄3 depending on the manufacturing process for the diode. Although the effect described above will also be present in the forward-bias region, it is overshadowed by a capacitance effect 53 directly dependent on the rate at which charge is injected into the regions just outside the depletion region. TRANSITION AND DIFFUSION CAPACITANCE The result is that increased levels of current will result in increased levels of diffusion capacitance (CD) as demonstrated by the following equation: where τT is the minority carrier lifetime - the time it take for a minority carrier such as a hole to recombine with an electron in the n-type material. 54 REVERSE RECOVERY TIME t r r t s tt DEFINING THE REVERSE RECOVERY TIME. Reverse Recovery time = trr Storage time = ts 55 Transition time = tt DIODE SPECIFICATION SHEETS Data about a diode is presented uniformly for many different diodes. This makes cross-matching of diodes for replacement or to make design easier. 1. Forward Voltage (VF) at a specified current and temperature 2. Maximum forward current (IF) at a specified temperature 3. Reverse saturation current (IR) at a specified voltage and temperature 4. Reverse voltage rating, [PIV or PRV or V(BR), where BR comes from the term “breakdown” (at a specified temp)] 5. Maximum power dissipation at a specified temperature 6. Capacitance levels 7. Reverse recovery time, trr 8. Operating temperature range 56 SEMICONDUCTOR DIODE NOTATION The anode is abbreviated A The cathode is abbreviated K 57 Various Types of Junction Diode 58 DIODE TESTING The condition of a semiconductor diode can be determined using Following methods: A digital display meter (DDM) with a diode checking function The ohmmeter section of a multimeter Curve tracer 59 Diode Checking Function of DDM The meter has an internal constant current source (about 2mA) that will define voltage level as indicated in Fig. An OL indication with the hookup of Fig. reveals an open (defective) diode. If the leads are reversed, an OL indication should result due to open circuit. Hence, an OL indication in both directions is an indication of an open or defective diode. 60 DIODE TESTING Ohmmeter Testing Relatively low resistance in forward bias using the connections as shown in Fig. For the reverse bias, the reading should be quite high, requiring a high resistance scale on the meter. A high resistance in both directions obviously indicates an open (defective-device) condition. A low resistance in both directions will indicate a shorted device. 61 CHECKING A DIODE WITH AN OHMMETER. DIODE TESTING Curve Tracer It can display the characteristics of many devices including the semiconductor diode. 62 DIODE TESTING Curve Tracer 63 CURVE TRACER RESPONSE TO IN4007 SILICON DIODE. ZENER DIODES 64 ZENER DIODES Location of Zener Region can be controlled by varying the doping levels. Zener diodes are available with zener potentials 1.8V to 200V with power rating from 1/4W to 50W. It is nice to assume that Zener diode is ideal with straight vertical line at Zener potential. 65 ZENER DIODES 66 Zener diode characteristics with the equivalent model for each region Electrical characteristics for a 10-V, 500-mW Zener diode IZT = Current defined by 1/4th power level. It is the current that will define the dynamic resistance ZZT and appears in the general equation for the power rating of device. PZ max 4 I ZTVZ PZ max 4(12.5mA)(10V ) 500mW 67 Electrical characteristics for a 10-V, 500-mW Zener diode 68 ZENER DIODES The Zener potential of a Zener diode is very sensitive to the temperature of operation. The temperature coefficient can be used to find the change in Zener potential due to a change in temperature. Where T1 is the new temperature level T0 is room temperature in an enclosed cabinet (250C) Tc is the temperature coefficient VZ is the nominal Zener potential at 25 0C 69 Example 1.5 Analyze the 10V diode, if the temperature is increased to 1000C. 70 ZENER DIODES ZENER TERMINAL IDENTIFICATION AND SYMBOLS. 71 LIGHT-EMITTING DIODES In Si and Ge diode the greater percentage of the energy converted during recombination at the junction is dissipated in the form of heat within the structure, and the emitted light is insignificant. Diode constructed of GaAs emit light in the infrared (invisible) zone during the recombination process at the p-n junction. These include optical coupling, in home entertainment centers, where the infrared light of the remote control is the controlling element. 72 LIGHT-EMITTING DIODES The frequency spectrum for infrared light extends from about 100 THz (T=1012) to 400 THz, with the visible light spectrum extending from about 400 to 750 THz. c = 3×108 m/s (the speed of light in a vacuum) f = Frequency in hertz λ = Wavelength in meters 73 LIGHT-EMITTING DIODES 74 LIGHT-EMITTING DIODES The response of the average human eye as provided in Fig. extends from about 350 nm to 800 nm with a peak near 550 nm. 75 Standard response curve of human eye, showing the eye’s response to light energy peaks at green and falls off for blue and red. HEWLETT-PACKARD SUBMINIATURE HIGH-EFFICIENCY RED SOLID-STATE LAMP: RELATIVE INTENSITY VERSUS WAVELENGTH (COURTESY HEWLETT-PACKARD CORPORATION.) 76 LIGHT-EMITTING DIODES 77 LIGHT-EMITTING DIODES If we substitute the energy gap level of 1.43 eV for GaAs into the equation, we obtain the following wavelength: The wavelength of 869 nm places GaAs in the wavelength zone typically used in infrared devices. 78 which is well beyond the visible range. HEWLETT-PACKARD SUBMINIATURE HIGH-EFFICIENCY RED SOLID-STATE LAMP: FORWARD CURRENT VERSUS FORWARD VOLTAGE (COURTESY HEWLETT-PACKARD CORPORATION.) 79 HEWLETT-PACKARD SUBMINIATURE HIGH-EFFICIENCY RED SOLID-STATE LAMP: RELATIVE LUMINOUS INTENSITY VERSUS FORWARD CURRENT (COURTESY HEWLETT-PACKARD CORPORATION.) A normalized plot is one where the variable of interest is plotted with 80 a specific level defined as the reference value with a magnitude of one. HEWLETT-PACKARD SUBMINIATURE HIGH-EFFICIENCY RED SOLID-STATE LAMP: RELATIVE EFFICIENCY VERSUS PEAK CURRENT (COURTESY HEWLETT-PACKARD CORPORATION.) 81 HEWLETT-PACKARD SUBMINIATURE HIGH-EFFICIENCY RED SOLID-STATE LAMP: RELATIVE LUMINOUS INTENSITY VERSUS ANGULAR DISPLACEMENT (COURTESY HEWLETT-PACKARD CORPORATION.) 82 LIGHT-EMITTING DIODES Reverse Breakdown Voltage: 3-5V (Occasionally 10V) Protective approach required For many years the available colors were green, yellow, orange and red permitting the use of average values of VF = 2V and IF = 20mA for obtaining the approximate operating level. Introduction of blue in early 90s and white in late 90s has changed these parameters. White: VF = 4V and IF = 20mA Blue : VF = 5V and IF = 20mA 83 SEVEN SEGMENT DISPLAY 84 ELEC - 01211 ELECTRONIC DEVICES AND CIRCUITS CHAPTER # 2 DIODE APPLICATIONS Dr. Muhammad Amjad Department of Electronic Engineering The Islamia University of Bahawalpur, Pakistan Chapter Outline 2 1) Introduction 2) Load-Line Analysis 3) Series Diode Configurations 4) Parallel and Series-Parallel Configurations 5) AND/OR Gates 6) Sinusoidal Inputs; Half-Wave Rectification 7) Full-Wave Rectification 8) Clippers 9) Clampers 10)Networks with a dc and ac Source 11)Zener Diodes 12)Voltage-Multiplier Circuits Diode Application-Introduction Once the basic behavior of a device is understood, its function and response in an infinite variety of configuration can be examined. The analysis of the electronic circuit can be followed in one of the two paths; a) Using the actual characteristic. b) Applying an approximate model for the device. 3 LOAD-LINE ANALYSIS The diode characteristics are placed on the same set of axes as a straight line defined by the parameters of the network. The straight line is called the load line because its intersection on the vertical axis is defined by the applied load R. Where the load line and the characteristic curve intersect is the Q-point, which specifies a particular ID and VD for a given circuit. 4 Series diode configuration: (a) circuit (b) characteristics Diode in DC Series Circuit: Forward Bias KVL : E VD VR 0 E VD I D R VD If we set VD = 0V, ID E R VD 0V If we set ID = 0A, VD E I D 0 A 5 LOAD-LINE ANALYSIS The point of intersection between the two is the point of operation for this circuit. 6 DRAWING THE LOAD LINE AND FINDING THE POINT OF OPERATION. Example 2.1 For the series diode configuration, determine a. VDQ and IDQ b. VR 7 Example 2.1 E 10 ID 20mA R VD 0V 0.5k VD E I D 0 A 10V I DQ 18.5mA VDQ 0.78V VR I R R I D Q R (18.5m)(0.5k ) 9.25V 8 Example 2.2 Now using the approximation equivalent model for the silicon semiconductor diode. I DQ 18.5mA VDQ 0.7V 9 Example 2.3 Using the ideal model. I DQ 20mA VDQ 0V 10 Series Diode Configurations The forward resistance of the diode is usually so small compared to the other series elements of the network that it can be ignored. In general, a diode is in the “on” state if the current established by the applied source is such that its direction matches that of the arrow in the diode symbol, and VD ≥ 0.7V for silicon, VD ≥ 0.3V for germanium, and VD ≥ 1.2V for gallium arsenide. 11 SERIES DIODE CONFIGURATIONS 12 SERIES DIODE CONFIGURATION. Determining the state of the diode VD VK VR E VK ID IR VR R SUBSTITUTING THE EQUIVALENT MODEL FOR THE “ON” DIODE 13 REVERSING THE DIODE Determining the state of the diode. VR I R R I D R (0) R 0V 14 SUBSTITUTING THE EQUIVALENT MODEL FOR THE “OFF” DIODE. Example 2.4 For the series diode configuration, determine VD, VR, and ID. VD 0.7V VR E VD 8 0.7 7.3V VR 7 . 3 ID IR 3.32mA R 2 .2 k 15 Example 2.5 Same data as example 2.4, with the diode reverse. VR I R R VR (0) R 0V E VD VR 0 VD E VR E 0 8V ID IR 0A 16 Source notation An open circuit can have any voltage across its terminals, but the current is always 0-A. A short circuit has a 0-V drop across its terminals, but the current is limited only by the surrounding network. 17 Example 2.6 For the series diode configuration, determine VD, VR, and ID. 18 Example 2.6 ID 0A VR I R R I D R (0)1.2 K 0V VD E 0.5V 19 Example 2.7 Determine V0 and ID for the series circuit. V0 E VK 1 VK 2 12 0.7 1.8 9.5V VR V0 9.5 ID IR 13.97 mA R R 680 20 Example 2.8 Determine ID, VD2 and V0. 21 Example 2.8 It is clear from the circuit ID 0A Applying Kirchhoff’s voltage law in clockwise direction E VD1 VD2 V0 0 VD2 E VD1 V0 20V 0 0 20V V0 0V 22 Example 2.9 Determine I, V1, V2 and V0 for the series dc configuration. V1 IR1 (2.07 m)(4.7 k ) 9.73V E1 V1 VD V2 E2 0 V2 IR2 (2.07 m)(2.2k ) 4.55V E1 IR1 VD IR2 E2 0 E1 E2 VD 10 5 0.7 14.3 I R1 R2 4 .7 k 2 .2 k 6 .9 k I 2.07 mA 23 Example 2.9 E2 V2 V0 0 V0 V2 E2 4.55 5 0.45V 24 PARALLEL AND SERIES-PARALLEL CONFIGURATION Example 2.10 Determine V0, I1, ID1, and ID2 for the parallel diode configuration. V0 0.7V 25 Example 2.10 VR E VD 10 0.7 I1 28.18mA R R 0.33K I D1 I D 2 I1 28.18mA 14.09mA 2 2 26 Example 2.11 There are two LEDs that can be used as a polarity detector. Apply a positive voltage and a green light results. Negative supplies results in a red light. Find the resistor “R” to ensure a current of 20mA through the “on” diode for the configuration as in Fig. Both diodes have a reverse breakdown voltage of 3V and an average turn-on voltage 2V. 27 Example 2.11 E VLED 8 2 I 20mA R R 6V R 300 20mA 28 Example 2.11 29 Example 2.11 30 Example 2.12 Determine the voltage V0 for the network. V0 12 0.7 11.3V 31 Example 2.13 Determine the currents I1, I2 and ID2 for the network. VK 2 0 .7 I1 0.212mA R1 3.3K 32 Example 2.13 V2 E VK 1 VK 2 0 V2 E VK 1 VK 2 20 0.7 0.7 18.6V V2 18.6 I2 3.32mA R2 5.6 K 33 Example 2.13 I D 2 I1 I 2 I D 2 I 2 I1 3.32mA 0.0212mA 3.11mA 34 AND/OR GATES 35 POSITIVE LOGIC OR GATE. Example 2.14 Determine V0 for the network. 36 Example 2.14 V0 E VD 10 0.7 9.3V E VD 10 0.7 I 9.3mA R 1K 37 Example 2.15 (Positive logic AND gate) Determine the output level for the positive logic AND gate. 38 POSITIVE LOGIC AND GATE. Example 2.15 (Positive logic AND gate) E VK 10 0.7 I 9.3mA R 1K 39 SINUSOIDAL INPUTS; HALF-WAVE RECTIFICATION 40 HALF-WAVE RECTIFIER. HALF-WAVE RECTIFICATION CONDUCTION REGION (0T/2). 41 NON-CONDUCTION REGION (T/2T). HALF-WAVE RECTIFICATION 42 HALF-WAVE RECTIFIED SIGNAL. HALF-WAVE RECTIFICATION Vdc 0.318Vm Vdc 0.318(Vm VK ) 43 Example 2.16 a. Sketch the output and determine the dc level of the output for the network. b. Repeat part (a) if the ideal is replaced by a silicon diode. c. Repeat (a) and (b) if Vm is increased to 200 V. 44 Example 2.16 Vdc 0.318Vm 0.318(20) 6.36V Vdc 0.318(Vm 0.7) 0.318(19.3V ) 6.14V Vdc 0.318Vm 0.318(200) 63.6V Vdc 0.318(Vm VK ) 0.318(200 0.7) (0.318)(199.3) 63.38V 45 EFFECT OF VK. PIV(PRV) PIVrating Vm half-wave rectifier 46 DETERMINING THE REQUIRED PIV RATING FOR THE HALF-WAVE RECTIFIER. FULL-WAVE RECTIFICATION (Bridge Network) FULL-WAVE BRIDGE RECTIFIER. 47 FULL-WAVE RECTIFICATION (Bridge Network) 48 NETWORK FOR THE PERIOD 0T /2 OF THE INPUT VOLTAGE VI. FULL-WAVE RECTIFICATION (Bridge Network) CONDUCTION PATH FOR THE POSITIVE REGION OF VI. 49 CONDUCTION PATH FOR THE NEGATIVE REGION OF VI. FULL-WAVE RECTIFICATION (Bridge Network) Vdc 2(0.318Vm) 0.636Vm Full-wave INPUT AND OUTPUT WAVEFORMS FOR A FULL-WAVE RECTIFIER. 50 FULL-WAVE RECTIFICATION (Bridge Network) Vi VK V0 VK 0 V0 Vi 2VK Vdc 0.636(Vm 2VK ) V0 max Vm 2VK 51 FULL-WAVE RECTIFICATION (Bridge Network) PIV Vm Full-wave rectifier 52 DETERMINING THE REQUIRED PIV FOR THE BRIDGE CONFIGURATION. Centre-Tapped Transformer CENTER-TAPPED TRANSFORMER FULL-WAVE RECTIFIER. 53 Centre-Tapped Transformer NETWORK CONDITIONS FOR THE POSITIVE REGION OF VI. 54 NETWORK CONDITIONS FOR THE NEGATIVE REGION OF VI. Centre-Tapped Transformer PIV Vsec ondary VR Vm Vm 2Vm PIV 2Vm CT transformer, full-wave rectifier 55 DETERMINING THE PIV LEVEL FOR THE DIODES OF THE CT TRANSFORMER FULL-WAVE RECTIFIER. Summary of Rectifier Circuits Rectifier Ideal VDC Realistic VDC Half Wave Rectifier VDC = 0.318(Vm) VDC = 0.318(Vm)– 0.7 FW Bridge Rectifier VDC = 0.636(Vm) VDC = 0.636(Vm) – 2(0.7) FW Center-Tapped Transformer Rectifier VDC = 0.636(Vm) VDC = 0.636(Vm) – 0.7 Vm = peak of the AC voltage. In the center tapped transformer rectifier circuit, the peak AC voltage is the transformer secondary voltage to the tap. 56 Example 2.17 Determine the output waveform for the network and calculate the output dc level and the required PIV of each diode. 57 Example 2.17 58 Vdc 0.636Vm 0.636(5) 3.18V CLIPPERS Clippers are networks that employ diodes to “clip” away a portion of an input signal without distorting the remaining part of the applied waveform. 59 SERIES CLIPPER. CLIPPERS SERIES CLIPPER WITH A DC SUPPLY. 1. Take careful note of where the output voltage is defined. 2. Try to develop an overall sense of the response by simply noting the “pressure” established by each supply and the effect it will have on the conventional current through the diode. 60 3. Determine the applied voltage (transition voltage) that will result in a change of state for the diode from the “off” to the “on” state. CLIPPERS The transition voltage can be found as, vi V 0 vi V For the “On” region, v0 vi V For the “Off” region, v0 0V 61 CLIPPERS 4. It is often helpful to draw the output wave form directly below the applied voltage using the same scales for the horizontal axis and the vertical axis. v0 peak Vm V DETERMINING THE TRANSITION LEVEL FOR THE CIRCUIT. 62 EXAMPLE 2.18 Determine the output wave from for the sinusoidal input. 63 Example 2.18 Step 1: The output is directly across the resistor R. Step 2: We can safely assume the diode is in the “on” state for the entire range of positive voltages for Vi. Once the supply goes negative, it would have to exceed the dc supply voltage 5V before it could turn the diode off. Step 3: The transition model is substituted and we find the transition from one state to the other will occur when v 5V 0V i vi 5V Step 4: For voltage less than -5V the diode is in the open-circuit state and the output is 0V, as shown in sketch of v0. For conditions when the diode is on and the diode current is 64 established the output voltage will be the following v0 vi 5V Example 2.18 65 DETERMINING THE TRANSITION LEVEL FOR THE CLIPPER SKETCHING THE OUTPUT VOLTAGE WAVEFORM Example 2.19 Find the output voltage for the network examined in Example 2.18 if the applied signal is the square wave as shown in Figure. APPLIED SIGNAL FOR EXAMPLE 2.19. VO AT VI = +20V 66 Example 2.19 VO AT VI = -10V. 67 SKETCHING VO FOR EXAMPLE 2.19. Parallel Clippers RESPONSE TO A PARALLEL CLIPPER. 68 Example 2.20 Determine vo for the network of Figure. 69 Example 2.20 70 SKETCHING VO FOR EXAMPLE 2.20. Example 2.21 Repeat Example 2.20 using a silicon diode with VK = 0.7V. 71 DETERMINING THE TRANSITION LEVEL FOR THE NETWORK. Example 2.21 KVL : vi VK V 0 vi V VK vi 3.3V DETERMINING VO FOR THE DIODE IN THE “ON” STATE. 72 SERIES CLIPPERS 73 PARALLEL CLIPPERS 74 CLAMPERS A clamper is a network constructed of diode, a resistor and a capacitor that shifts a waveform to a different dc level. The chosen resistor and capacitor must be such that time constant determined by τ = RC is sufficiently large to ensure that voltage across the capacitor does not discharge during the interval diode is 75 not conducting. CLAMPERS Step 1: Start the analysis by examining the response of the portion of the input signal that will forward bias the diode. Step 2: During the period that the diode is in the “on” state, assume that the capacitor will charge up instantaneously to a voltage level determined by the surrounding network. Step 3: Assuming that during the period when the diode is in the “off” state the capacitor holds on to its established voltage level. Step 4: Throughout the analysis maintain a continual awareness of the location and defined polarity for v0 to ensure that the proper levels are obtained. 76 Step 5: Check that the total swing of the output matches that of the input. CLAMPERS v0 0 V V v0 0 v0 2V 77 CLAMPERS 78 SKETCHING VO FOR THE NETWORK Example 2.22 Determine the v0 for the network. APPLIED SIGNAL AND NETWORK Time Constant Time required to change by 63% after a sudden rise or fall in V & I. f 1000 Hz T 1ms RC (100k)(1F ) 0.01s 10ms The total discharge time is therefore 5 5(10ms ) 50ms 79 Example 2.22 vo 5V 20V Vc 5V 0 Vc 25V 10V 25V v0 0 vo 35V 80 Example 2.23 :REPEAT EXAMPLE 2.22 USING A PRACTICAL SI DIODE 5V 0.7V v0 0 vo 4.3V 20V Vc 0.7V 5V 0 10V 24.3V V0 0 vo 34.3V Vc 24.3V 81 Clamping Networks 82 CLAMPING CIRCUITS WITH IDEAL DIODES (5Τ = 5RC >>T/2) Clamping Networks CLAMPING NETWORK WITH A SINUSOIDAL INPUT. 83 Networks With a DC and AC Source This section will expand the analysis to include both an ac and a dc source in the same configuration. In Fig. the simplest of two-source networks has been constructed. For such a system it is especially important that the Superposition Theorem can be applied. The response of any network with both an ac and a dc source can be found by finding the response to each source independently and then combining the results. 84 Networks With a DC and AC Source DC Source The network is redrawn as shown in Fig. for the dc source. Note that the ac source was removed by simply replacing it with a short-circuit equivalent to the condition vs = 0V. Using the approximate equivalent circuit for the diode, the output voltage and current is 85 Networks With a DC and AC Source AC Source The dc source is replaced by a short-circuit equivalent, as shown in Fig. The diode will be replaced by the ac resistance. The current in the equation being the quiescent or dc value. For this case, 86 Networks With a DC and AC Source Replacing the diode by this resistance will result in circuit of Fig. For the peak value of the applied voltage, the peak values of vR and vD will be, Combining the results of the dc and ac analysis will result in the 87 waveforms of Fig. for vR and vD. Networks With a DC and AC Source vR 9.3V vRpeak 1.99V vD 0.7V vDpeak 10mV 0.01V 88 Networks With a DC and AC Source For comparison purposes the same system will now be analyzed using the actual characteristics and a load-line analysis. In Fig. the dc load line has been drawn. The resulting dc current is now slightly less due to a voltage drop across the diode that is slightly more than the approximate value of 0.7 V. In this case, however, quiescent value of dc current is ≈4.6 mA so the new ac resistance is rD 5.99 I D 4.65mA which is very close to calculated value. It is now clear that change in diode voltage for this region is very small, resulting in minimum impact on output voltage. In general, the diode had a strong impact on the dc level of the 89 output voltage but very little impact on the ac swing of the output. Networks With a DC and AC Source VD E I ID D 0 A 10V E 10 5mA R VD 0V 2k 90 Zener Diodes 91 ZENER DIODE EQUIVALENTS FOR THE (A) “ON” AND (B) “OFF” STATES. Zener Diodes Approximate equivalent circuit for the Zener diode in the three possible states. 92 Example 2.24: Use to establish reference voltage levels Determine the reference voltages provided by the network, which uses a white LED to indicate that the power is on. What is the level of current through the LED and the power delivered by the supply? How does the power absorbed by the LED compare to that of the 6-V Zener diode? V01 VZ 2 VK 3.3 0.7 4V V02 V01 VZ 1 4 6 10V 93 Example 2.24 Current through resister, I R I LED VR 40 V02 VLED 40 10 4 26 20mA R 1 .3 K 1 .3 K 1 .3 K Power delivered by the supply, PS EI S EI R (40)(20m) 800mW Power absorbed by the LED, PLED VLED I LED ( 4)(20m) 80mW Power absorbed by the 6-V Zener diode, PZ VZ I Z (6)(20m) 120mW 94 REGULATOR A regulator is a combination of elements designed to ensure that the output voltage of a supply remains fairly constant. 95 Example 2.25 The network is design to limit the voltage to 20V during the positive portion of the applied voltage and to 0V for a negative excursion of the applied voltage. Check its operation and plot the waveform of the voltage across the system for the applied signal. Assume the system has a very high input resistance so it will not affect the behavior of the network. 96 Zener Diodes 97 Zener Diodes The use of the Zener diode as regulator and for analysis point of view there are three conditions. 1. Vi and RL Fixed 2. Fixed Vi, Variable RL 3. Fixed RL, Variable Vi 98 BASIC ZENER REGULATOR. 1 - Vi and RL Fixed Determine the state of the Zener diode by removing it from the network and calculating the voltage across the resulting open circuit. RLVi V VL R RL If V ≥ Vz, the Zener diode is on and the appropriate equivalent model can be substituted. If V < Vz, the diode is off, and the open-circuit equivalence is substituted. 99 DETERMINING THE STATE OF THE ZENER DIODE. 1 - Vi and RL Fixed Substitute the appropriate equivalent circuit and solve for the desired unknowns. VL VZ The zener diode current must be determined by an application of Kirchhoff’s current law, IR IZ IL VL IL RL IR IZ IR VR Vi VL R R IL Power dissipated by the Zener diode is, PZ VZ I Z When the Zener diode is turned on i.e., the voltage across the Zener 100 diode is VZ volts, it will then “lock in” at this level and never reach the higher level. Example 2.26 a) b) Determine VL, VR, IZ, and PZ Repeat (a) with RL = 3kΩ 101 ZENER DIODE REGULATOR Example 2.26 RLVi (1.2k)(16) V VL 8.73V R RL 1.2k 1k VR Vi VL 16 8.73 7.27V IZ 0A PZ VZ I Z 0W 102 DETERMINING VL FOR THE REGULATOR. Example 2.26 V VL RLVi (3k)(16) 12V R RL 3k 1k VL VZ 10V VR Vi VL 16 10 6V VL 10V IL 3.33mA RL 3k IR VR 6V 6mA R 1k I Z I R I L 6mA 3.33mA 2.67 mA PZ VZ I Z (10V )(2.67 mA) 26.7 mW 103 2 - Fixed Vi Variable RL We have Solving for RL, The max IL, RLVi V VL R RL RLmin I Lmax RVZ Vi VZ VZ VZ RL RLmin Since R is constant, so once diode is ON VR and IR will be constant. VR IR VR Vi VZ R Zener current IZ IR IL RLmax VZ I Lmin I Lmin I R I ZM 104 max. load resistance Example 2.27 a) For the network, determine the range of RL and IL that will result in VRL being maintained at 10V. b) Determine the maximum wattage rating of the diode. 105 VOLTAGE REGULATOR. Example 2.27 RLmin RVZ (1k)(10V ) 250 Vi VZ 50 10 VR Vi VZ 50 10 40V VR 40V IR 40mA R 1k I Lmin I R I ZM 40mA 32mA 8mA RLmax VZ 10V 1.25k I Lmin 8mA Pmax VZ I ZM (10V )(32mA) 320mW 106 3 - FIXED RL, VARIABLE VI Voltage Vi must be sufficiently large to turn the Zener diode on. The minimum turn-on voltage Vi = Vimin is determined by The maximum value of Vi is limited by the maximum Zener current IZM. Since IZM = IR - IL, Since IL is fixed at VZ/RL and IZM is the maximum value of IZ, the 107 maximum Vi is defined by, Example 2.28 Determine the range of values of Vi that will maintain the zener diode in the “on” state. Vimin ( RL R )VZ (1.2k 220) 23.67V RL 1.2k VL VZ 20V IL 16.67 mA RL RL 1.2k I Rmax I ZM I L 60mA 16.67 mA 76.67 mA Vimax I Rmax R VZ (76.67 mA)(220) 20V 36.87V 108 Example 2.28 VL VERSUS VI FOR THE REGULATOR. 109 Voltage-Multiplier Circuits Voltage Doubler 110 HALF-WAVE VOLTAGE DOUBLER. Voltage Doubler VC1 Vm Vm VC1 VC2 0 Vm Vm VC2 0 VC2 2Vm DOUBLE OPERATION, SHOWING EACH HALF-CYCLE OF OPERATION: (A) POSITIVE HALF-CYCLE; (B) NEGATIVE HALF CYCLE. 111 Voltage Doubler 112 FULL-WAVE VOLTAGE DOUBLER. Voltage Doubler 113 ALTERNATE HALF-CYCLES OF OPERATION FOR FULL-WAVE VOLTAGE DOUBLER. Voltage Tripler and Quadrupler VOLTAGE TRIPLER AND QUADRUPLER. 114 ELEC - 01211 Electronic Devices and Circuits Chapter # 3 Bipolar Junction Transistors (BJT) Dr. Muhammad Amjad Department of Electronic Engineering The Islamia University of Bahawalpur, Pakistan Outline 1. Introduction 2. Transistor Construction 3. Transistor Operation 4. Common-Base Configuration 5. Transistor Amplifying Action 6. Common-Emitter Configuration 7. Common-Collector Configuration 8. Limits of Operation 9. Transistor Specification Sheet 10. Transistor Testing 11. Transistor Casing and Terminal Identification Bipolar Junction Transistor (BJT) Transistor was invented in 1947 at the Bell Telephone Laboratories by John Bardeen and Walter Brattain under the direction of William Shockley Transistors v/s Vacuum Tubes Transistor Vacuum Tube Inexpensive Expensive Excellent Reliability Very Unreliable Very Small Large and Bulky Stable Temperatures Get Hot Quickly Very Fast Slow Found in Large Numbers Found in small numbers Cannot carry very high voltage Can carry high voltage (Main factor responsible for the survival of vacuum tubes in some appliances) Transistor Construction A bipolar junction transistor (BJT) is a three - terminal device constructed of doped semiconductor material BJT is used in amplifying or switching applications, in discrete circuits and in IC design, both in analog and digital domain Bipolar Junction Transistors are so named because their operation involves injection of both electrons and holes into oppositely polarized materials. Transistor Construction There are two types of transistors: • pnp • npn pnp The terminals are labeled: • E - Emitter • B - Base • C - Collector npn Types of transistors: (a) pnp; (b) npn. Transistor Operation Depending upon the bias condition (forward or reverse) of each of the two junctions (emitter-base and collector-base), different modes of operation of the BJT are obtained Mode Active Saturation Cutoff Emitter-Base Junction Forward Forward Reverse Collector-Base Junction Reverse Forward Reverse Active mode – transistor operating as an amplifier Cutoff and Saturation mode – switching applications, e.g. in logic circuits Transistor Operation Forward-biased junction of a pnp transistor. Transistor Operation Reverse-biased junction of a pnp transistor. Transistor Operation Majority and minority carrier flow of a pnp transistor. Transistor Operation With the external sources, VEE and VCC, connected as shown below: The emitter-base junction is forward biased The base-collector junction is reverse biased Current in a Transistor Emitter current is the sum of the collector and base currents: Ι Ι Ι Ε B C The collector current is comprised of two currents: IC IC I CO majority minority Common-Base Configuration The base is common to both input (emitter–base) and output (collector–base) of the transistor. Notation and symbols used with the common-base configuration: (a) pnp transistor; (b) npn transistor. Common-Base Configuration Input Characteristics This curve shows the relationship between input current (IE) to input voltage (VBE) for various levels of output voltage (VCB). Input or driving point characteristics for a common-base silicon transistor amplifier. Common-Base Configuration Output Characteristics This graph demonstrates the output current (IC) to an output voltage (VCB) for various levels of input current (IE). Output or collector characteristics for a common-base transistor amplifier. Common-Base Configuration Reverse saturation current. Common-Base Configuration Developing the equivalent model to be employed for the base-to-emitter region of an amplifier in the dc mode. Alpha (α) In the dc mode the level of IC and IE due to the majority carriers are related by a quantity called ALPHA (α). dc IC IC I CO majority minority IC IE I C I E I CBO I C ac I E VCB constant The ac alpha is formally called the “common-base, short circuit, amplification factor”. Ideally: α = 1 In reality: α is between 0.90 and 0.998 Biasing Establishing the proper biasing management for a common-base pnp transistor in the active region. Transistor Amplifying Action Ii Vi 200m 10mA Ri 20 ac 1( I c I e ) I L I i 10mA VL I L R (10m)(5k ) 50V Av VL 50 250 Vi 200m Basic voltage amplification action of the common-base configuration. Transistor Amplifying Action The basic amplifying action was produced by transferring a current “I” from a low-to a high-resistance circuit. transfer + resistor = transistor Common-Emitter Configuration The emitter is common to both input (base-emitter) and output (collectoremitter). The input is on the base and the output is on the collector. Input or base-emitter configuration Notation and symbols used with the common-emitter configuration: npn transistor Common-Emitter Configuration Output or collector-emitter configuration Notation and symbols used with the common-emitter configuration: pnp transistor. Common-Emitter Configuration Output characteristics Input characteristics Characteristics of a silicon transistor in the common-emitter configuration: (a) collector characteristics; (b) base characteristics. Common-Emitter Configuration I E IC I B IC I C majority I CO & I C αI E minority I C αI E I CBO I C α I C I B I CBO I B I CBO IC 1 1 When IB = 0 A, there is some minority current flowing called ICEO IC IC I CBO I CBO 250I CBO 1 0.996 0.004 I CEO I CBO 1 I B 0 μA Common-Emitter Configuration Circuit conditions related to ICEO Piecewise-linear equivalent for the Transistor characteristics. Beta (β) represents the current amplification factor of a transistor and ranges 50 to 400. dc IC IB In the dc mode is sometimes referred to as hFE, the term FE is derived from Forward Current amplification and common-Emitter configuration, respectively. I C ac I B VCE constant The formal name for βac is forward-current, common-emitter, amplification factor(hfe). Beta (β) dc ac ac I C 2.7 mA 108 IB 25A I C I B VCE constant I C 2 I C1 3.2m 2.2m 1mA 100 I B 2 I B1 30 20 10A Determining βac and βdc from the collector characteristics. Beta (β) ac I C 9mA 7 mA 2mA 200 I B 45A 35A 10A dc IC 8mA 200 I B 40A Characteristics in which βac is the same everywhere and βac = βdc. Beta (β) IE IC IC IB IC 1 I C I B I C I B I B I C (1 ) I B IC I E IC I B IC 1 1 1 1 I CEO I CBO 1 1 1 1 I CEO ( 1) I CBO I CEO I CBO Biasing The proper biasing of a common-emitter amplifier can be determined in a manner similar to that introduced for the commonbase configuration for the npn transistor. Determining the proper biasing arrangement for a common-emitter npn transistor configuration. Common-Collector Configuration Notation and symbols used with the common-collector configuration: (a) pnp transistor; (b) npn transistor. Common-Collector Configuration Common-collector configuration used for impedance-matching purposes. Limits of Operation For common-emitter characteristics, the maximum dissipation level is defined by: PC max VCE I C The transistor operates in the active region between saturation and cutoff. IC and VCE must be in and their product must fall in following range: Cut-off region I I I CEO Saturation region C C max VCE sat VCE VCE max VCE I C PC max Limits of Operation PC max VCE I C VCE (50mA) 300mW VCE 300mW 6V 50mA PC max VCE I C (20V ) I C 300mW IC 300mW 15mA 20V PC max VCE I C VCE (25mA) 300mW VCE 300mW 12V 25mA Defining the linear (undistorted) region of operation for a transistor. Power dissipation Common - base: PCmax VCBI C Common - emitter: PCmax VCE I C Common - collector: PCmax VCE I E Transistor Specification Sheet Transistor Specification Sheet Transistor Specification Sheet Transistor Testing (Curve Tracer) Curve tracer response to 2N3904 npn transistor. Transistor Testing (Curve Tracer) ac 9 200 div 180 10 div ac I C 2 I C1 8.2m 6.4m 1.8mA 180 I B 2 I B1 40 30 10A Determining βac for the transistor characteristics at IC = 7 mA and VCE = 5V. Transistor Testing (Transistor Testers) Transistor tester. (Courtesy Computronics Technology, Inc.) Transistor Testing (Ohmmeter) Checking the forward-biased base-toemitter junction of an npn transistor. Checking the reverse-biased base-tocollector junction of an npn transistor. Various types of transistors: (a) Courtesy General Electric Company; (b) and (c) Courtesy of Motorola Inc.; (c) Courtesy International Rectifier Corporation. Transistor terminal identification. Internal construction of a Fairchild transistor in a TO-92 package. (Courtesy Fairchild Camera and Instrument Corporation.) Type Q2T2905 Texas Instruments quad pnp silicon transistors: (a) appearance; (b) pin connections. (Courtesy Texas Instruments Incorporated.) ELEC - 01211 Electronic Devices and Circuits DC Biasing - BJTs Department of Electronic Engineering The Islamia University of Bahawalpur, Pakistan Outline 1. 2. 3. 4. 5. Introduction Operating Point Fixed Bias Configuration Emitter Bias Configuration Voltage Divider Bias Configuration 6. Collector Feedback Configuration 7. Emitter Follower Configuration 8. Common Base Configuration 9. Miscellaneous Bias Configurations 10. Summary Table 11. 12. 13. 14. 15. Design Operations Current Mirror Circuits Current Source Circuits pnp Transistors Transistor Switching Networks Introduction BJTs amplifier requires a knowledge of both the DC analysis (large signal) and AC analysis (small signal). BJT need to operate in active region to be used as amplifier. The cutoff and saturation region used as a switches. For the BJTs to be biased in its linear or active operating region the following must be true: a) BE junction forward biased, 0.6V or 0.7V b) BC junction reverse biased For transistor amplifiers the resulting DC current and voltage establish an operating point that define the region that can be employed for amplification process. Introduction Important basic relationships for a transistor: VBE=0.7V IE=(β+1)IB≈IC IC = βIB Operating Point Operating point quiescent point or Q-point The biasing circuit can be designed to set the device operation at any of these points or others within the active region. The BJT device could be biased to operate outside the max limits, but the result of such operation would be shortening of the lifetime of the device or destruction of the device. The chosen Q-point often depends on the intended use of the circuit. Operating Point The DC input establishes an operating or quiescent point called the Q-point. Various operating points within the limits of operation of a transistor IC(mA) PCmax IB=60 uA ICmax 18 IB=50 uA 15 IB=40 uA 12 Saturation B 9 IB=30 uA IB=20 uA 6 D 3 C IB=10 uA IB=0 uA A VCEsat VCE(V) 10 20 Cutoff 30 40 VCEmax Biasing and three states of operation • Active or Linear Region Operation Base–Emitter junction is forward biased Base–Collector junction is reverse biased • Cutoff Region Operation Base–Emitter junction is reverse biased Base–Collector junction is reverse biased • Saturation Region Operation Base–Emitter junction is forward biased Base–Collector junction is forward biased DC biasing circuits • Fixed Bias Configuration • Emitter Bias Configuration • Voltage Divider Bias Configuration • Collector Feedback Configuration • Emitter Follower Configuration • Common Base Configuration Fixed-Bias Circuit Replace the capacitors with an open-circuit equivalent because the reactance of a capacitor for dc is ∞Ω The dc supply Vcc can be separated into two supplies Fixed bias circuit DC equivalent Forward Bias of Base-Emitter From Kirchhoff’s voltage law: +VCC – IBRB – VBE = 0 Solving for the base current: IB VCC VBE RB Collector-Emitter Loop The magnitude of the IC is related directly to IB through IC=βIB Apply KVL in the clockwise direction around the indicated close loop results: VCE+ICRC-VCC=0 VCE = VCC-ICRC Recall that : VCE = VC - VE In this case, VE = 0V, so VCE=VC VBE=VB-VE Then VE=0V, VBE=VB Collector–emitter loop Example 4.1 Determine the following for the fixed-bias configuration, a. IBQ and ICQ b. VCEQ c. VB and VC d. VBC Example 4.1 a ) I BQ VCC VBE RB 12 0.7 47.08A 240k I CQ I BQ 5047.08 2.34 mA b) VCEQ VCC - I C R C 12 - 2.34m2.2k 6.83V c) VBE VB 0.7 V VCE VCEQ VC 6.83 V d )VBC VB VC 0.7 6.83 6.13V - ve sign indicates that BC - junction is reverse biased. Transistor Saturation Transistor Saturation When the transistor is operating in the saturation region it is conducting at maximum current flow through the transistor. VCE 0 V V 0V R CE 0 CE I I C C sat V 12 I CC 5.45mA Csat R 2.2 k C Load-Line Analysis The characteristics of the BJT are superimposed on a plot of the network equation defined by the same axis parameters. VCE V I R CC C C Load-line analysis: (a) the network; (b) the device characteristics Load-Line Analysis VCE V I R CC C C VCE V ( 0) R CC C 0 V I R CC C C VCE V CC V I CC C R C The Q-point is the particular operating point: • where the value of RB sets the value of IB • where IB and the load line intersect • that sets the values of VCE and IC Load-Line Analysis Fixed-bias load line. Load-Line Analysis Case 1: • Level IB changed by varying the value of RB. • Q-point moves up and down Movement of the Q-point with increasing level of IB. Load-Line Analysis Case 2: • VCC fixed and RC change the load line will shift as shown in Fig. • IB fixed, the Q-point will move as shown in the same figure. Effect of an increasing level of on the load line and Q-point. Load-Line Analysis Case 3: • RC fixed and VCC varied, the load line shifts as shown in Fig. Effect of lower values of on VCC the load line and Q-point. Example 4.3 Given the load line and the defined Q-point, determine the required values of VCC, RC, and RB for a fixed-bias configuration. Step 1 : V V 20 V at I 0 mA CE CC C V I CC at V 0V. C CE R C R C V I 20 2 k 10m CC C Step 2 : I B R B V CC -V BE R V V CC I 20 0.7 25 772 k B B BE Emitter Bias Configuration Adding a resistor (RE) to the emitter circuit stabilizes the bias circuit. BJT bias circuit with emitter resistor. Base-Emitter Loop From Kirchhoff’s voltage law : VCC - I B R B - VBE - I E R E 0 Since IE = ( + 1)IB: VCC - I B R B - VBE - ( 1)IB R E 0 Solving for IB: IB Base-emitter loop; equivalent circuit. VCC - VBE R B ( 1)R E Collector-Emitter Loop From Kirchhoff’s voltage law : I E R E VCE I C R C VCC 0 Since IE IC: VCE VCC – I C (R C R E ) Also: VE I E R E VC VCE VE VCC - I C R C VB VBE VE VCC – I B R B Collector-emitter loop. Example 4.4 For the emitter bias network, determine a. IB b. IC c. VCE d. VC e. VE f. VB g. VBC a) I B VCC - VBE 20 0.7 40.1A RB 1RE 430k 50 11k b) I C I B 5040.1 2.01mA c) VCE VCC - I C R C R E 20 2.01m 2k 1k 20 6.03 13.97V d )VC VCC I C RC 20 2.01m 2k 20 4.02 15.98V e)VE VC VCE 15.98 13.97 2.01V OR VE I E RE I C RE 2.01m 1k 2.01V f )VB VBE VE 0.7 2.01 2.71V g )VBC VB VC 2.71 15.98 13.27V (reverse biased as required) Example 4.4 Improved Bias Stability Adding RE to the emitter improves the stability of a transistor. Stability refers to a bias circuit in which the currents and voltages will remain fairly constant for a wide range of temperatures and transistor Beta () values. Data from example (fixed-bias configuration) IB(A) IC(mA) VCE(V) 50 47.08 2.34 6.83 100 47.08 4.71 1.64 Data from example (emitter-bias configuration) IB(A) IC(mA) VCE(V) 50 40.1 2.01 13.97 100 36.3 3.63 9.11 Saturation Level ICsat: V I (R R ) 0 CC Csat C E V CC I Csat R R C E Determining Icsat for the emitter bias circuit. Load line analysis VCE=VCC – IC(RC+RE) Step 1: Choose IC=0 mA. Substitute into (1), we get VCE=VCC (2) located at X axis Step 2: Choose VCE=0V, substitute into (1) gives VCC IC RC RE VCE 0V (3) located at Y axis Step 3: Joining two points defined by (2) + (3), we get straight line that can be drawn as in Fig. Voltage-Divider Bias Configuration This is a very stable bias circuit. The currents and voltages are almost independent of variations in . Voltage-Divider Bias Configuration Two kind of analysis for Voltage Divider Bias: Exact Analysis Approximate Analysis Voltage-Divider Bias Configuration Exact Analysis Thevenin Equivalent circuit is applied for VCC, Ground, R1 and R2 at base terminal VB The Circuit at base terminal becomes: Voltage-Divider Bias Configuration Exact Analysis Voltage-Divider Bias R V E V 2 CC TH R R R 2 1 2 ETH I B RTH VBE I E RE 0 Subtitute I E β 1I B gives IB ETH VBE RTH 1RE I E RE VCE I C RC VCC 0 VCE=VCC – IC(RC+RE) Example 4.7 Solution RT H R1 R2 39k 3.9k 3.55 k 39k 3.9k R2VCC 3.9k 22 ET H 2V R1 R2 39k 3.9k ETH VBE IB RTH 1RE 2 0.7 6.05A 3.55k 140 11.5k I C I B 1406.05 0.85mA VCE VCC I C RC RE 22 0.85m10k 1.5k 12.22V Approximate Analysis Where IB << I1 and I2 then I1 I2 : VB R 2 VCC R1 R 2 Where RE ≥ 10R2: IC I E VE RE VE VB VBE From Kirchhoff’s voltage law: VCE VCC - I C R C - I E R E IE IC VCE V CC -IC (R C R E ) Ri R2 I1 I 2 Ri 1RE Example 4.8 Example 4.8 Step1 : RE 10R2 1401.5k 103.9k 210k 39k satisfied! VCEQ VCC I C RC RE 22 0.867m10k 1.5k 12.03V Step 2 : VB R2VCC 3.9k 22 2V R1 R2 39k 3.9k VE VB VBE 2 0.7 1.3V I CQ VE 1 .3 IE 0.867mA RE 1. 5k ICQ(mA) VCEQ(V) Exact Analysis 0.85 12.22 Approximate Analysis 0.87 12.03 ICQ and VCEQ are certainly close. Example 4.9 Repeat the analysis example 4.7, if 70. RTH 3.55 k ETH 2V IB ETH VBE RTH 1RE 2 0.7 11.81A 3.55k 70 11.5k I C I B 7011.81 0.83mA VCE VCC I C RC RE 22 0.83m10k 1.5k 12.46V Voltage-Divider Bias Configuration ICQ(mA) VCEQ(V) 140 0.85 12.22 70 0.83 12.46 Conclusion: Even though is drastically half, the level of ICQ and VCEQ are essentially same. Example 4.11 Determine the levels of ICQ and VCEQ for the voltage-divider configuration using the exact and approximate analysis. Compare the solution. Solution: Exact Analysis RT H R1 R2 82k 22k 17.35 k 82k 22k R2VCC 22k 18 ET H 3.81V R1 R2 82k 22k I BQ ETH VBE 3.81 0.7 39.6 A RTH 1RE 17.35k 50 11.2k I CQ I B 5039.6 1.98mA VCEQ VCC I C RC RE 18 1.98m5.6k 1.2k 4.54V Solution (continued) Approximate Analysis RE 10R2 501.2k 1022k 60k 220k (not satisfied) R2VCC 22k 18 VB ETH 3.81V R1 R2 82k 22k VE VB VBE 3.81 0.7 3.11V VE 3.11 I CQ I E 2.59mA R E 1 .2 k VCEQ VCC I C RC RE 18 2.59m5.6k 1.2k 3.88V Solution (continued) ICQ(mA) %difference VCEQ(V) %difference Exact Analysis Approximate Analysis 1.98 4.54 23.5% 2.59 17% 3.88 Transistor Saturation The saturation level for Voltage-Divider bias is the same as for Emitter-Bias configuration due to the existence of RC and RE . Load –Line Analysis The load line therefore have the same appearance with: VCC IC RC RE VCE VCC VCE 0V IC 0mA located at y - axis located at x - axis Collector Feedback Configuration Another way to improve the stability of a bias circuit is to add a feedback path from collector to base. In this bias circuit the Q-point is only slightly dependent on the transistor beta, . DC bias circuit with voltage feedback. Base-Emitter Loop Applying Kirchoff’s voltage law: VCC – ICRC – IBRB – VBE –IERE = 0 Note: IC = IC + IB -- but usually IB << IC so IC IC Knowing IC = IB and IE IC then: VCC – IB RC – IBRB – VBE –IBRE = 0 Simplifying and solving for IB: IB VCC VBE R B (R C R E ) Collector-Emitter Loop Applying Kirchoff’s voltage law: IERE + VCE + ICRC – VCC = 0 Since IC IC and IC = IB: IC(RC + RE) + VCE – VCC =0 Solving for VCE: VCE VCC I C ( RC RE ) Collector Feedback Configuration Transistor Saturation Level I C sat I Cmax VCC RC RE Load Line Analysis It is the same analysis as for the voltage divider bias and the emitter-biased circuits. Cutoff Saturation VCE VCC V CC I C R R C E I C 0mA VCE 0V Example 4.12 VCC VBE IB R B (R C R E ) 10 0.7 250k 90( 4.7 k 1.2k ) 9 .3 IB 250k 531k I B 11.91A IB I C I B (90)(11.91 ) 1.07mA VCE VCC I C ( RC RE ) 10 1.07m( 4.7 k 1.2k ) 10 6.31 3.69V Example 4.13 Repeat example 4.12 using beta of 135. 135 Design Operations Runknown VR IR Example 4.21 Given the device characteristics in Fig., determine VCC, RB and RC for the fixed-bias configuration. Characteristics with load-line; Fixed Bias circuit. Example 4.22 Given that ICQ = 2mA and VCEQ = 10V, determine R1 and RC for the network. Example 4.23 The emitter-bias configuration of Fig. has the following specifications: ICQ = 1/2ICsat, ICsat = 8mA, VC = 18V, and β = 110. Determine RC, RE and RB. Design of a Bias Circuit with an Emitter Feedback Resistor RE – to provide dc bias stabilization so that the change of collector current due to leakage currents in the transistor and the transistor beta would not cause a large shift in the operating point. The RE cannot be unreasonably large because the voltage across it limits the range of swing of the voltage from collector to emitter. VE – typically 1/4 - 1/10 from supply voltage Example 4.24 Determine the resistor values, for the indicated operating point and supply voltage. Design of a Current-Gain-Stabilized (BetaIndependent) Circuit Example 4.25 Example 4.25 Multiple BJT Networks Multiple BJT Networks Darlington Configuration Darlington Configuration Cascode Configuration Cascode Configuration Feedback Pair Feedback Pair Current Mirror Circuits Used primarily in integrated circuits The output current is the reflection or mirror of a current developed on one side of the circuit The circuit is particularly suited to IC manufacture because the circuit requires that the transistors used have identical BE voltage drops and values of beta Results best achieved when transistors are formed at the same time in IC manufacture Current Mirror Circuits Current Mirror Circuits The current IX set by transistor Q1 and resistor RX is mirrored in the current I through transistor Q2 IB IE I E 1 The collector current of each transistor is then, IC I E Finally the current IX through resistor RX is, I X IE 2I E 2 IE IE In summary, the constant current provided at the collector of Q2 mirrors that of Q1. Because VCC VBE IX RX Example 4.26 Calculate the mirrored current I in the circuit of Fig 4.66. Example 4.27 Calculate the current I through each of the transistor Q2 and Q3 in the circuit of Fig 4.67. Current Source Circuits Ideal Voltage Source R 0 Ideal Current Source R Bipolar Transistor - Constant Current Source Assuming that the base input impedance is much larger than R1 or R2, we have VB R1 (VEE ) R1 R2 VBE VB VE VE VB 0.7 VE (VEE ) IE IC RE Example 4.28 Calculate the constant current I in the circuit of Fig 4.72. Transistor/Zener Constant Current Source Replacing resistor R2 with a Zener diode, as shown in Fig, provides an improved constant current source. The zener diode results in a constant current calculated using the BE KVL equation. The value of I can be calculated using VZ VBE I E RE 0 I E RE VZ VBE VZ VBE I IE RE The constant current depends upon the Zener diode voltage which remains quite constant. Example 4.29 Calculate the constant current I in the circuit of Fig 4.74. pnp Transistors pnp Transistors pnp transistor in an emitter-stabilized configuration. Example 4.30 Example 4.30 Transistor Switching Networks Transistor Switching Networks Transistor Switching Networks When Vi = 5V, the transistor will be on and design must ensure that network is saturated by a level of IB greater than associated with the IB curve appearing near Saturation level. I C sat VCC RC The level of IB in the active region just before saturation can be approximated by: I Bmax I C sat dc For the saturation level we must therefore ensure following condition is satisfied: IB I C sat βdc Transistor Switching Networks For the network, when Vi = 5V, the resulting level of IB is, IB Vi 0.7 5V-0.7V 63μA RB 68k and I Csat VCC 6.1mA RC Testing, I B 63A I Csat dc 6.1mA 48.8A 125 Certainly, any level of IB greater than 60μA will pass through a Q-point on the load line that is very close to the vertical axis. For Vi = 0V, IB = 0μA and IC = ICEO = 0mA, the voltage drop across RC is, VRC I C RC 0V Resulting in VC = +5V Transistor Switching Networks The transistor can also be used as a switch using the same extremities of the load line. At saturation, the current IC is quite high and the voltage VCE very low. The resulting resistance level between terminals is Rsat VCEsat I Csat Using a typical average value of VCEsat such as 0.15V gives Rsat VCEsat I Csat 0.15V 24.6 6.1mA which is very low and can be considered 0Ω when placed in series with resistors in kΩ range For Vi = 0V, the cutoff condition results in a resistance level of magnitude: Rcutoff VCC 5V I CEO 0mA Rcutoff VCC 5V 500k I CEO 10A Resulting in the open circuit equivalence Transistor Switching Networks Saturation conditions and the resulting terminal resistance. Cutoff conditions and the resulting terminal resistance. Example 4.31 Example 4.31 Switching Time Transistor switching times: ton t r t d toff t s t f td delay time tr rise time ts storage time tf fall time Where ton total time for the transistor to switch from “off” to “on” Where toff total time for the transistor to switch from “on” to “off” ELEC - 012211 Electronic Devices and Circuits BJT AC Analysis Department of Electronic Engineering The Islamia University of Bahawalpur, Pakistan Outline 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. Introduction Application in the AC Domain BJT Transistor Modeling The re Transistor Model Common-Emitter Fixed-Bias Configuration Voltage-Divider Bias Common-Emitter Emitter-Bias Configuration Emitter-Follower Configuration Common-Base Configuration Collector Feedback Configuration Collector DC Feedback Configuration Effect of RL and RS Determining the Current Gain Summary Tables 15. 16. 17. 18. 19. 20. Two-Port Systems Approach Cascaded Systems Darlington Connection Feedback Pair The Hybrid Equivalent Model Approximate Hybrid Equivalent Circuit 21. Complete Hybrid Equivalent Circuit 22. Hybrid π Model 5.1 Introduction There are three methods for small-signal ac analysis of the transistor network: The re model The Hybrid equivalent model The hybrid π model 5.2 Amplification in the AC Domain Conservation of energy dictates that over time the total output power, P0 of a system cannot be greater than its input power, Pi and the efficiency cannot be greater than 1. Efficiency, η = P0/Pi The output sinusoidal signal is greater than the input signal, i.e. the output power is greater than input ac power. How the ac power output can be greater than its power input? An ac power output greater than the input ac power is only due to dc power. Conversion efficiency, η = P0(ac)/Pi(dc) Where P0(ac) is the ac power to the load Pi(dc) is the dc power supplied 5.2 Amplification in the AC Domain The role of dc supply can best be described by first considering the simple dc network of Figure. Let us now insert a control mechanism which can result a substantial oscillation in the output circuit. Steady current established by a dc supply. Effect of a control element on the steady-state flow of the electrical system 5.2 Amplification in the AC Domain For this example, iac(p-p)>>ic(p-p) Peak to peak value of the output current far exceeds that of the control current. In general, proper amplification design requires that the dc and ac components be sensitive to each other’s requirements and limitations. The superposition theorem is applicable for the analysis and design of the dc and ac components of a BJT network, permitting the separation of the analysis of the dc and ac responses of the system. 5.3 BJT Transistor Modeling A model is a combination of circuit elements, properly chosen, that best approximates the actual behavior of a semiconductor device under specific operating conditions. Transistor circuit examination in this introductory discussion. 5.3 BJT Transistor Modeling By removal of the dc supply and insertion of the short-circuit equivalent for the capacitors. 5.3 BJT Transistor Modeling 5.3 BJT Transistor Modeling 5.3 BJT Transistor Modeling The AC equivalent of a network is obtained by: 1. Setting all DC sources to zero & replacing them by a shortcircuit equivalent. 2. Replacing all capacitors by a short-circuit equivalent. 3. Removing all elements bypassed by short-circuit equivalent. 4. Redrawing the network. 11 5.3 BJT Transistor Modeling Vi Zi Ii Vo Av Vi Vo Zo Io Io Ai Ii 5.4 The re Transistor Model Common Emitter Configuration Starting with the input side, we find the applied voltage Vi is equal to the voltage Vbe with the input current being the base current Ib. 5.4 The re Transistor Model If we redraw the collector characteristics to have a constant β (another approximation), the entire characteristics at the output section can be replaced by a controlled source whose magnitude is beta times the base current. 5.4 The re Transistor Model The equivalent model can be improved by first replacing the diode by its equivalent resistance. 26mV rD ID 26mV re IE 5.4 The re Transistor Model The collector output current is still linked to the input current by β. 5.4 The re Transistor Model It is desirable to have large output impedances to avoid loading down the next stage of a design. If the slope of the curves is extended until they reach the horizontal axis, they will all intersect at a voltage called the Early voltage. This intersection was first discovered by James M. Early in 1952. As base current increases the slope of line increases, resulting in an increase in output impedance with increase in base and collector current. For a particular collector and base current, the output impedance can be found using the equation: 5.4 The re Transistor Model Typically, the Early voltage is sufficiently large compared with the applied collector-to-emitter voltage to permit the following approximation. Clearly, since VA is a fixed voltage, the larger the collector current, the less the output impedance. For situations where the Early voltage is not available the output impedance can be found from the characteristics at any base or collector current using the following equation: 5.4 The re Transistor Model The equivalent circuit of Figure will be used throughout the analysis to follow for the Common Emitter Configuration. Typical values of β run from 50 to 200 with values of βre running from few hundred to max. of 6kΩ to 7kΩ. The output resistance is typically in the range of 40kΩ to 50kΩ. 5.4 The re Transistor Model Common Base Configuration The collector current is related to the emitter current by α. The direction of collector current in the output circuit is now opposite to that of the defined output current. 5.4 The re Transistor Model Common base configurations have very low input impedance because it is essentially re typical values extend from few ohms to perhaps 50Ω. The output impedance ro will typically extend into the MΩ range. The output current is opposite to the defined Io direction, so there is no phase shift between the input and output voltages. 5.4 The re Transistor Model Common Collector Configuration The model defined for the Common Emitter Configuration is normally applied rather than defining a model for the Common Collector Configuration. 5.5 Common Emitter Fixed-Bias Configuration Removal of the effects of VCC, C1 and C2. 5.5 Common Emitter Fixed-Bias Configuration Substituting the re model into network. 5.5 Common Emitter Fixed-Bias Configuration Zi Z i RB || re Zi re R B 10 re Zo Z o RC||rO Zo RC ro 10 Rc The total resistance of two parallel resistors is always less than the smallest and very close to the smallest if one is much larger than the other. 5.5 Common Emitter Fixed-Bias Configuration Gain Calculations AV Av VO Vi VO βI b(RC|| ro ) Vi I b βre βI b(RC|| ro ) Av I b βre Vo (RC||ro ) Av Vi re RC Av re ro 10RC if ro Ω or ro 10RC 5.5 Common Emitter Fixed-Bias Configuration Phase Relation The phase shift is due to the fact that βIb establishes a current through RC that will result in a voltage across RC opposite to that defined by Vo. Demonstrating the 1800 phase shift between input and output waveforms. Example 5.1 Example 5.1 5.6 Voltage-Divider Bias Configuration 5.6 Voltage-Divider Bias Configuration Impedance Calculations Input Impedance: R R1||R2 R1 R2 R1 R2 Z i R || re Output Impedance: Z o RC||ro Z o RC ro 10RC 5.6 Voltage-Divider Bias Configuration Voltage Gain: Vo ( I b )(R C|| ro ) Ib Vi βre V Vo β i (RC|| ro ) βre Vo RC||ro Av Vi re Vo RC Av Vi re ro 10RC 5.6 Voltage-Divider Bias Configuration Phase Relationship: The negative sign reveals a 180° phase shift between Vo and Vi. Example 5.2 For the network in Fig. Determine a. re b. Zi c. Z0 (r0 = ∞Ω) d. AV (r0 = ∞Ω) e. The parameters of parts (b) through (d) if r0 = 50 kΩ and compare results. Example 5.2 5.7 CE Emitter-Bias Configuration Un-bypassed Substituting the re equivalent circuit into the ac equivalent network. 5.7 CE Emitter-Bias Configuration Input Impedance: Vi I b re I e RE Vi I b re ( 1) I b RE Zb Vi re ( 1)RE Ib Z b β ( re RE ) Z b RE RE re Z i RB||Zb Output Impedance: With Vi set to zero, Ib = 0, and βIb can be replaced by an open-circuit equivalent. The result is Z o RC 5.7 CE Emitter-Bias Configuration AV Ib Vi Zb Vo I o RC βI b RC Vi β Z RC b Vo βRC Av Vi Zb Av RC re RE R Av C RE Phase Relationship Zb β(re RE ) Zb βRE The negative sign reveals a 180° phase shift between Vo and Vi. 5.7 CE Emitter-Bias Configuration Effect of ro Each equation can be derived through application of KVL, KCL, Source Conversions, Thevenin’s Theorem and so on. Zi ( 1) RC / ro Z b re RE 1 ( RC RE ) / ro Z i RB||Zb Zo Z o RC AV ( ro re ) ro re 1 RE V AV o Vi RC Zb re RC 1 r r o o R 1 C ro 5.7 CE Emitter-Bias Configuration Effect of ro Zi ( 1) RC / ro Z b re RE 1 ( R R ) / r C E o ( 1) RE Z b re 1 ( R R ) / r C E o Rc Z b re ( 1) RE ro 10( RC RE ) OR Z b (re RE ) r 10( R o C Z i RB||Zb RE ) ro ( 1) 5.7 CE Emitter-Bias Configuration Zo Z o RC ( ro re ) ro r e 1 RE if ro re Z o RC β ro 1 βre 1 RE Z o RC 1 ro 1 r 1 e β RE Z o RC 51ro for β 100, re 100Ω and R E 1kΩ 1 1 r 1 e β RE 1 1 1 10 100 1000 1 1 51 0.02 Z o RC any level of ro 5.7 CE Emitter-Bias Configuration AV Vo AV Vi RC RC Zb re RC 1 r ro o R 1 C ro re 1 ro AV Vo Vi Zb 1 Vo βRC Av Vi Zb RC ro RC ro ro 10RC Vo RC Av Vi re RE RC Av RE Zb β(re RE ) Zb βRE 5.7 CE Emitter-Bias Configuration Bypassed AV Zi Zo Z i RB || re Z o RC||rO Zi re R B 10 re Zo Rc ro 10 Rc Vo (RC||ro ) Av Vi re RC Av re ro 10RC Example 5.3 For the network in Figure, without CE (unbypassed), determine a) re b) Zi c) Zo d) AV Example 5.3 Example 5.4 Repeat the analysis with CE in place. 5.7 CE Emitter-Bias Configuration Another variation of an emitter-bias configuration is shown in Figure. An emitter-bias configuration with a portion of the emitter-bias resistance bypassed in the ac domain. For the dc analysis, the emitter resistance is RE1+RE2 For the ac analysis RE in the equations above is simply RE1 with RE2 bypassed by CE. 5.8 Emitter-Follower Configuration Vo follows the magnitude of Vi with in phase relationship accounts for terminology emitter-follower. It is used for impedance matching purpose as it presents high impedance at input and low impedance at output. Emitter-follower configuration. Substituting the re equivalent circuit into the ac equivalent network. 5.8 Emitter-Follower Configuration Zi Z i RB||Zb Z b βre (β 1 )RE Z b β(re RE ) Z b βRE RE re 5.8 Emitter-Follower Configuration Zo Ib Vi Zb Vi I e (β 1 )I b (β 1 ) Zb subtitute for Z b gives Ie (β 1 )Vi βre (β 1 )RE Ie Vi βre R E (β 1 ) βr βre and e re (β 1) β Vi Ie re RE but (β 1 ) β 5.8 Emitter-Follower Configuration If we construct the network defined by equation, the configuration results: Ie AV Vi re RE Z o RE||re Z o re RE r e REVi Vo RE re Vo RE Av Vi RE re Vo Av 1 Vi R E re , RE re RE Phase Relation: A Emitter Follower configuration has no phase shift between input and output. 5.8 Emitter-Follower Configuration Effect of ro Zi Z i RB||Zb 5.8 Emitter-Follower Configuration Zo AV Example 5.7 For the emitter follower network of Fig., determine: a. re b. Zi c. Zo d. AV e. Repeat parts (b) through (d) with ro = 25kΩ and compare results. Example 5.7 Example 5.7 In general, therefore, even though the condition ro ≥ 10RE is not satisfied, the results for Zo and AV are the same, with Zi only slightly less. 5.8 Emitter-Follower Configuration Emitter-follower configuration with a voltage-divider biasing arrangement. Earlier Eqs. Changes only by replacing RB by R = ׳R1‖R2 Emitter-follower configuration with a collector resistor RC. Zi and Zo are unaffected by RC The only effect of RC is to determine the Q-point of operation. 5.9 Common-Base Configuration It has relatively low input and high output impedance. 5.9 Common-Base Configuration Impedance Calculations Zi Zo Z i RE||re Z o RC 5.9 Common-Base Configuration Gain Calculations AV Vo I o RC ( I C ) RC αI e RC Vi Ie re Vi Vo α RC re Vo αRC RC Av Vi re re Ai Assuming RE >> re yields, Ie Ii I o αI e αI i I o I i Ai 1 Ii Ii 5.9 Common-Base Configuration Phase Relation AV is positive shows that Vo and Vi are in phase. Vo Effect of ro ro is typically in the MΩ range and sufficiently larger than the parallel resistance RC to permit the approximation ro||RC=RC. Example 5.8 Example 5.8 5.10 Collector Feedback Configuration The collector feedback configuration employs a feedback path from collector to base to increase the stability of the system. However, connecting resistor in this way rather than base to dc supply has a significant effect on the level of difficulty when analyzing the network. 5.10 Collector Feedback Configuration Zi 5.10 Collector Feedback Configuration Zi 5.10 Collector Feedback Configuration Zi 5.10 Collector Feedback Configuration Zo If Vi is set to zero as required to define Zo, the effect of βre is removed and RF appears in parallel with RC. 5.10 Collector Feedback Configuration AV 5.10 Collector Feedback Configuration AV Phase Relation 1800 phase shift between Vo and Vi. 5.10 Collector Feedback Configuration Effect of ro Zi A complete analysis without applying approximations results in 5.10 Collector Feedback Configuration Zi 5.10 Collector Feedback Configuration Zo Including ro in parallel with RC results in 5.10 Collector Feedback Configuration AV Example 5.9 For the network in Fig, determine a. re b. Zi c. Zo d. AV e. Repeat parts (b) through (d) with ro = 20kΩ & compare results. Example 5.9 Example 5.9 5.10 Collector Feedback Configuration with Emitter Resistor RE Zi Zo AV Collector feedback configuration with an emitter resistor RE. 5.11 Collector DC Feedback Configuration The network has a dc feedback resistor for increased stability. The capacitor C3 will shift portions of the feedback resistance to the input and output sections of the network in the ac domain. 5.11 Collector DC Feedback Configuration Input Impedance: Output Impedance: Z i RF1||re Z o RC||RF2||ro If ro ≥ 10Rc Z o RC||RF2 5.11 Collector DC Feedback Configuration Voltage Gain: R' ro||RF2||RC Vo βI b R' Vi Ib βre Vi Vo β R' βre Vo ro||RF2||RC R' Av Vi re re For ro 10RC , Vo RF2||RC Av Vi re Phase Relation: 1800 phase shift between input and output voltages. Example 5.10 For the network in Figure, determine a. re b. Zi c. Zo d. AV e. Vo if Vi = 2mV Example 5.10 For the network in Figure, determine a. re b. Zi c. Zo d. AV e. Vo if Vi = 2mV Example 5.10 5.12 Effect of RL and RS The effect of applying a load to the output terminal and the effect of using a source with an internal resistance will be investigated. No-Load voltage gain Voltage gain with Load RL Additional effect of source resistance on voltage gain 5.12 Effect of RL and RS For the same configuration 𝐴𝑣𝑁𝐿 > 𝐴𝑣𝐿 > 𝐴𝑣𝑠 5.12 Effect of RL and RS For a particular design, the larger the level of RL, the greater is the level of ac gain. In other words, larger the load resistance, closer it is to open circuit approximation. For a particular amplifier, the smaller the internal resistance of the source, the greater is the overall gain. In other words, closer the source resistance is to short circuit approximation, the greater is the gain because effect of Rs essentially be eliminated. 5.12 Effect of RL and RS There are two possible approaches for network analysis involving effects of RS and RL. o Insert the re equivalent model and perform the analysis as demonstrated earlier. o Define two port equivalent model and then analyze. In this section first approach will be used and the 2nd will be used in next section. The detailed analysis of each configuration will not be presented as for re model. However, the analysis would be ample to investigate any amplifier with a load or source resistance. 5.12 Effect of RL and RS Fixed Bias Configuration Av 5.12 Effect of RL and RS Fixed Bias Configuration Zi Zo Overall Gain The factor other than 𝐴𝑣𝐿 is always less than one which supports the fact that signal 𝐴𝑣𝑠 is always less than 𝐴𝑣𝐿 . Example 5.11 Example 5.1 Example 5.1 5.12 Effect of RL and RS Voltage Divider Bias Configuration Voltage-divider bias configuration with RS and RL. Substituting the re equivalent circuit into the ac equivalent network. 5.12 Effect of RL and RS Voltage Divider Bias Configuration Overall Gain Av Zi Zo Voltage divider bias configuration with RS and RL. 5.12 Effect of RL and RS Emitter-follower Configuration Emitter-follower configuration with RS and RL. Substituting the re equivalent circuit into the ac equivalent network. 5.12 Effect of RL and RS Emitter-follower Configuration Av Vo RE Av Vi RE re Zi Zo Vi Ie re RE Z o RE||re Z o re RE r e REVi Vo RE re 5.13 Determining the Current Gain For each transistor configuration, the current gain can be determined directly from the voltage gain, the defined load, the input impedance. AiL I o Vo RL V Z o. i Ii Vi Z i Vi RL AvL . Zi RL 5.13 Determining the Current Gain Voltage Divider Bias Example 5.2 For the network in Fig. Determine a. re b. Zi c. Z0 (r0 = ∞Ω) d. AV (r0 = ∞Ω) e. The parameters of parts (b) through (d) if r0 = 50 kΩ and compare results. Example 5.2 5.13 Determining the Current Gain Common Base Configuration 5.13 Determining the Current Gain Ai Assuming RE >> re yields, Ie Ii I o αI e αI i I o I i Ai 1 Ii Ii 5.14 Summary Tables Table 5.1 Unloaded BJT Amplifiers 5.14 Summary Tables Table 5.1 Unloaded BJT Amplifiers 5.15 Two-Port System Approach It is often necessary to work with the terminal characteristics of a device rather then the individual components of the system. The designer is handed a packaged product with a list of data regarding its characteristics but has no access to the internal construction. The result will be an understanding of how each parameter of the packaged system relates to the actual amplifier or network. The system of Fig. is called a two-port system because there are two sets of terminals - one at the input and the other at the output. The data surrounding a packaged system is the no-load data, because the load has not been applied. 5.15 Two-Port System Approach For the two-port system, the polarity of the voltages and the direction of the currents are as defined. For amplifiers, the parameters of importance have been sketched within the boundaries of the two-port system. The input and output resistance of a packaged amplifier are normally provided along with the no-load gain. For the no-load situation the output voltage is, 5.15 Two-Port System Approach The output resistance is defined by Vi = 0V. Due to this, quantity 𝐴𝑣𝑁𝐿 𝑉𝑖 is zero volts and can be replaced by a short-circuit equivalent. The result is Finally, the input impedance Zi simply relates the applied voltage to the resulting input current and For the no-load situation, the current gain is undefined because the load current is zero. There is, however, a no-load voltage gain equal to 𝐴𝑣𝑁𝐿 . 5.15 Two-Port System Approach The effect of applying a load to a two-port system will result in the configuration of Fig. Ideally, all the parameters of the model are unaffected by changing loads and levels of source resistance. However, for some transistor configurations the applied load can affect the input resistance, whereas for others the output resistance can be affected by the source resistance. In all cases, however, by simple definition, the no-load gain is unaffected by the application of any load. 5.15 Two-Port System Approach Applying the voltage-divider rule to the output circuit results in RL Vo AvNLVi RL Ro AvL Vo RL AvNL Vi RL Ro Because the ratio RL/(RL + Ro) is always less than 1, we have further evidence that the loaded voltage gain of an amplifier is always less than the no-load level. The current gain is then determined by I o Vo RL Vo Ri AiL . Ii Vi Ri Vi RL Ri AvL . RL 5.15 Two-Port System Approach In Figure, a source with an internal resistance has been applied to the basic two port system. The parameters Zi and 𝐴𝑣𝑁𝐿 of a two-port system are unaffected by the internal resistance of the applied source. The fraction of applied signal reaching the input terminals of the amplifier is determined by VDR. 5.15 Two-Port System Approach Considering the effects of both RS and RL on the gain of an amplifier. At the input side, we find and at the output side, Vo RL AvL Av NL Vi RL Ro 5.15 Two-Port System Approach For the total gain 𝐴𝑣𝑆 following mathematical steps can be performed, Vo Vo Vi AvS . VS Vi VS And substituting the equations results in, Vo Ri RL AvS . . AvNL VS RL Ro Ri RS Or, using Is = Vs/(Rs+Ri), Rs Ri AiS AvSL . RL The same current gain can be determined using, AiL AvL . Ri RL However, Is = Ii, so above two equations generate the same results. Example 5.12 Determine 𝐴𝑣𝐿 and 𝐴𝑣𝑆 for the network of Example 5.11 and compare solutions. Example 5.1 showed that 𝐴𝑣𝑁𝐿 = -280.11, Zi = 1.07kΩ and Zo= 3kΩ. In Example 5.11, RL = 4.7kΩ and RS = 0.3kΩ. AvL RL Av NL RL Ro 4 .7 k ( 280.11) 4.7 k 3k 170.98 AvS Both results are same as found in Example 5.11. Ri RL . AvNL Ri Rs RL Ro 1.07k 4.7k . (280.11) 1.07 k 0.3k 4.7k 3k (0.781)(0.610)( 280.11) 133.45 Example 5.13 Given the packaged (no-entry-possible) amplifier. a) Determine the gain 𝐴𝑣𝐿 and compare it to the no-load value with RL = 1.2kΩ. b) Repeat part (a) with RL = 5.6kΩ and compare solution. c) Determine 𝐴𝑣𝑆𝐿 with RL = 1.2kΩ. d) Find the current gain Ai = Io/Ii = Io/Is with RL = 5.6kΩ. Part (a) RL AvL AvNL RL Ro 1.2k (480) 1.2k 2k (0.375)(480) 180 Which is a dramatic drop from the no-load value. Example 5.13 Part (b) RL AvL AvNL RL Ro 5.6k .( 480) (0.737)(480) 5.6k 2k 353.76 Part (c) Ri RL AvS . AvNL Ri Rs RL Ro Which clearly reveals that the larger the load resistor, the better is the gain. 4k 1.2k . (480) 4k 0.2k 1.2k 2k (0.952)(0.375)(480) 171.36 Which is fairly close to the loaded gain 𝐴𝑣𝐿 because the input impedance is considerably more than the source resistance and there is much less voltage drop across Rs as compared to Ri. Example 5.13 Part (d) Ri AiL AvL . RL 4k (353.76) 5.6k (353.76)(0.714) 252.6 Rs Ri AiS AvS . RL Ri RL AvS . AvNL Ri Rs RL Ro 0.2k 4k (336.78) 5.6k (336.78)(0.75) 4k 5.6k . .(480) 4k 0.2k 5.6k 2k (0.952)(0.737)(480) 252.6 336.78 5.15 Two-Port System Approach The two reduction factors of Eq. form a product that has to be carefully considered in any design procedure. Vo Ri RL AvS . . AvNL VS RL Ro Ri RS It is not sufficient to ensure that RS is relatively small if the effect of the magnitude of RL is ignored. AvSL (0.9)(0.2) Av NL 0.18 AvNL AvSL (0.9)(0.9) Av NL 0.81Av NL AvSL (0.9)(0.7) Av NL 0.63AvNL In general, for good overall gain the effects of RS and RL must be evaluated individually and as a product. 5.16 Cascaded Systems Two-port systems approach is particularly useful for the cascaded systems. The total gain of the system is then determined by the product of the individual gains as follows: AvT Av1 Av2 Av3 The total current gain is given by AiT AvT Z i1 RL Example 5.14 The two stage system of Fig. employs a transistor EF configuration prior to a CB configuration to ensure that the maximum percentage of the applied signal appears at the input terminals of the CB amplifier: a) The loaded gain for each stage. b) The total gain for the system, 𝐴𝑣𝑇 and 𝐴𝑣𝑆 . c) The total current gain for the system. d) The total gain for the system if emitter follower configuration were removed. Example 5.14 Example 5.14 The gain is about 25 times greater with the EF Configuration to draw the signal to the amplifier stages. Output impedance of first stage should relatively close to the input impedance of 2nd stage, otherwise the signal would loss again due to voltage divider action. 5.16 Cascaded Systems RC Coupled BJT Amplifiers One popular connection of amplifier stages is the RC-coupled variety as shown in Example. The name is derived from the Coupling Capacitor CC and the fact that the load on the first stage is an RC combination. The coupling capacitor isolates the two stages from a dc viewpoint but acts as a short-circuit equivalent for the ac response. The input impedance of the second stage acts as a load on the first stage, permitting the same approach to the analysis as described in previous two sections. Example 5.15 a) Calculate the no load voltage gain and output voltage of RC coupled transistor amplifiers as shown in Figure. b) Calculate the overall gain if a 4.7kΩ load is applied to the second stage and compare to the results of part (a). c) Calculate the input impedance of the first stage and the output impedance of the second stage. Example 5.15 Example 5.15 5.16 Cascaded Systems Cascode Connection The cascode configuration has two types. In each case, the collector of the leading transistor is connected to the Emitter of the following transistor. One arrangement is shown in Figure on next slide. The second arrangement is discussed in Example 5.16. 5.16 Cascaded Systems The arrangements provide a relatively high input impedance with low voltage gain for the first stage to ensure input Miller capacitance is at a minimum. X CM 1 1 CM i (1 Av )C f Zi Ri X CM X CM Ri Following CB stage provides an excellent high frequency response. 9.10 Miller Effect Capacitance For inverting amplifiers (having negative value of Av), the input and output capacitance is increased by a capacitance level sensitive to the inter-electrode capacitance between the input and output terminals of the device and gain of the amplifier. This “feedback” capacitance is defined by Cf. 9.10 Miller Effect Capacitance X CM 1 X C M Ri Zi Ri X C M Zi Ri X C M X C M Ri 1 1 CM i (1 Av )C f Example 5.16 Calculate the no load voltage gain of the cascode configuration. The loading on Q1 is the input impedance of Q2 in the CB configuration as shown by re. The result is replacement of RC in basic noload equation for the gain of CB configuration. Example 5.16 The CE stage provides a higher input impedance than can be expected from the CB stage. With Av of about 1 for the first stage, the Miller-effect input capacitance is kept quite low to support a good high frequency response. X CM 1 1 CM i (1 Av )C f A large Av of 265 was provided by CB stage to give the overall design a good input impedance level with desirable gain levels. 5.17 Darlington Connection A very popular connection of two bipolar junction transistors for operation as one “super-beta” transistor is called the Darlington Connection. The main feature is that the composite transistor acts as a single unit with a current gain that is the product of the current gains of the individual transistors. If the connection is made using two separate transistors it will provide a current gain of D 1 2 5.17 Darlington Connection Darlington amplifier used in emitter-follower configuration is shown. The primary impact of using the Darlington configuration is an input impedance much larger than that obtained with a single-transistor network. The current gain is also larger, but the voltage gain for a singletransistor or Darlington configuration remains slightly less than one. DC Bias The base current is determined using a modified version of Eq. 4.44. There are now two base-to-emitter voltage drops to include and the beta of a single transistor is replaced by the Darlington combination. 5.17 Darlington Connection Example 5.17 Calculate the dc bias voltages and currents in the circuit of figure. 5.17 Darlington Connection AC Input Impedance The ac input impedance can be determined using the ac equivalent network of Figure. 5.17 Darlington Connection AC Input Impedance 5.17 Darlington Connection AC Current Gain 5.17 Darlington Connection AC Current Gain 5.17 Darlington Connection AC Voltage Gain 5.17 Darlington Connection AC Output Impedance The output current has been redefined to match standard nomenclature and properly defined Zo. 5.17 Darlington Connection 5.17 Darlington Connection 5.17 Darlington Connection 5.17 Darlington Connection Voltage Divider Amplifier DC Bias Now investigate the effect of the Darlington configuration in a basic amplifier configuration There is a collector resistor RC, and emitter terminal of the Darlington circuit is connected to ground for ac conditions. 5.17 Darlington Connection 5.17 Darlington Connection AC Input Impedance The resistors R1 and R2 are in parallel with the input impedance to the Darlington pair, assuming the second transistor found by assuming the second transistor acts like an RE load on the first. 5.17 Darlington Connection AC Current Gain 5.17 Darlington Connection AC Current Gain 5.17 Darlington Connection AC Voltage Gain The input voltage is the same across R1 and R2 and at the base of the first transistor as shown in Fig. 5.17 Darlington Connection AC Output Impedance Because the output impedance in RC is parallel with the collector to emitter terminals of the transistor, we can look back on similar situations and find that the output impedance is defined by where ro2 is the output resistance of the transistor Q2. 5.17 Darlington Connection Note the significant drop in current gain due to R1 and R2. 5.17 Darlington Connection Packaged Darlington Amplifier Because the Darlington connection is so popular, a number of manufacturers provide packaged units such as shown in Fig. Typically, the two BJTs are constructed on a single chip rather than separate BJT units. Only one set of collector, base, and emitter terminals is provided for each configuration. These, are the base of the transistor Q1, the collector of Q1 and Q2, and the emitter of Q2. 5.17 Darlington Connection Some of the ratings for an MPSA28 Fairchild Semiconductor Darlington amplifier are provided. 5.18 Feedback Pair Two transistor circuit operates like the Darlington circuit. Uses a pnp transistor driving an npn transistor, the two devices acting effectively much like one pnp transistor. Feedback pair provides a very high current gain (product of transistor current gains) like Darlington circuit. It may appear that it would have a high voltage gain because the output is taken off the collector with a resistor RC in place. However, the pnp–npn combination results in terminal characteristics very similar to that of the emitter–follower configuration. A typical application uses a Darlington connection and a Feedback pair connection to provide complementary transistor operation (Chapter 12). 5.18 Feedback Pair Quasi-Complementary Push-Pull Amplifier A Darlington pair and a feedback pair combination perform the pushpull operation. This increases the output power capability. 5.18 Feedback Pair Example 5.18 Calculate the bias currents and voltages for the circuit given below to provide Vo at one half the supply voltage (9V). 5.18 Feedback Pair AC Operation 5.18 Feedback Pair Zi 5.18 Feedback Pair Zi 5.18 Feedback Pair Ai 5.18 Feedback Pair Ai 5.18 Feedback Pair Av re1 2 RC 2 RC Av 2 RC Av 1 5.18 Feedback Pair Zo 5.18 Feedback Pair Zi 𝑍𝑖 = 𝑅𝐵 ∥ 𝑍𝑖′ 𝑍𝑖 = 2MΩ ∥ 1.89MΩ 𝑍𝑖 = 0.97MΩ 5.18 Feedback Pair Ai Av Zo Introduction There are three methods for small-signal ac analysis of the transistor network: The re model Hybrid equivalent model The hybrid π model 5.19 - The Hybrid Equivalent Model 5.20 - Approximate Hybrid Equivalent Circuit 5.21 - Complete Hybrid Equivalent Circuit 5.22 - Hybrid π Model 5.19 Hybrid Equivalent Model There is a mix of usage depending on the level and direction of investigation. The re model has the advantage that the parameters are defined by the actual operating conditions. The parameters of hybrid equivalent circuit are defined in general terms for any operating conditions. The hybrid parameters may not reflect the actual operating conditions but simply provide an indication of the level of each parameter to expect no matter what conditions actually exist. The re model suffers from the fact that parameters such as the feedback elements are not available, whereas hybrid parameters provide the entire set on the specification sheet. 5.19 Hybrid Equivalent Model In most cases, if re model is employed, the investigator will simply examine the specification sheet to have some idea of what additional elements might be. This section will show how one can go from one model to the other and how the parameters are related. The hybrid parameters: hie, hre, hfe, hoe are developed and used to model the transistor. These parameters can be found in a specification sheet for a transistor. 5.19 Hybrid Equivalent Model The description of the hybrid equivalent model will begin with the general two-port system of Fig. The following set of equations is only one of a number of ways in which the four variables of Fig. can be related. Vi h11 I i h12Vo I o h21I i h22Vo The parameters relating the four variables are called h-parameters, from the word “hybrid”. The term hybrid is chosen because the mixture of variables (V and I) in each equation results in a “hybrid” set of units of measurement for the h-parameters. 5.19 Hybrid Equivalent Model Vi h11 I i h12Vo h11 h12 Vi Vo Vi Ii Vo 0V unitless I i 0 A h11 Short-circuit input-impedance parameter hi h12 Open-circuit reverse transfer voltage ratio parameter hr I o h21I i h22Vo h21 Io Ii h22 unitless Vo 0V Io Vo Siemens I i 0 A h21 Short-circuit forward transfer current ratio parameter hf h22 Open-circuit output admittance parameter ho 5.19 Hybrid Equivalent Model Complete Hybrid Equivalent Circuit Vi h11 I i h12Vo I o h21I i h22Vo h11 input resistance hi h12 reverse transfer voltage ratio (Vi/Vo) hr h21 forward transfer current ratio (Io/Ii) hf h22 output conductance ho The resistance is reciprocal of conductance 1/h22. 5.19 Hybrid Equivalent Model Common emitter hybrid equivalent circuit The h-parameters will change with each configuration. To distinguish which parameter has been used or which is available, a second subscript has been added to the h-parameters. 5.19 Hybrid Equivalent Model Common base hybrid equivalent circuit The fact that both a Thevenin and a Norton circuit appear in the circuit, was further for calling the resultant circuit a hybrid equivalent circuit. 5.19 Hybrid Equivalent Model Simplified Hybrid Equivalent Model For CE and CB configurations, the magnitude of hr and ho is often such that the results obtained for parameters Zi, Zo, Av, and Ai are only slightly effected if hr and ho are not included. Because hr is a small quantity, its removal is approximated by: hr 0 therefore hrVo 0 Resulting in a short circuit equivalent for the feedback element. The resistance defined by 1/ho is often large enough to be ignored in comparison to a parallel load, permitting its replacement by an opencircuit equivalent for the CE and CB models. ho (high resistance on the output) The model can be simplified based on these approximations. 5.19 Hybrid Equivalent Model ho hrVo 0 5.19 Hybrid Equivalent Model Common-Emitter hybrid vs. re Model hie = re hfe = Common-Base hybrid vs. re Model hib re h fb 1 Minus sign accounts for fact that current source of standard hybrid equivalent circuit is pointing downward rather than actual direction in re model. Example 5.19 Given IE = 3.2mA, hfe = 150, hoe = 25µS, hob = 0.5 µS, determine a. The common-emitter hybrid equivalent circuit. b. The common-base re model. 5.20 Approximate Hybrid Equivalent Circuit Approximate CE Hybrid Equivalent Circuit The CE h-parameters and components of the re model are related by: hie = re hfe = hoe = 1/ro 5.20 Approximate Hybrid Equivalent Circuit Approximate CB Hybrid Equivalent Circuit The CB h-parameters and components of the re model are related by: hib = re hfb = - hob = 1/ro Fixed-Bias Configuration Zi Av Zo h fe ( RC 1 hoe ) Vo Av Vi hie Fixed-Bias Configuration Ai I o h fe I i Ai h fe Ii Ii Example 5.20 For the network of Figure, determine a. Zi b. Zo c. Av d. Ai Voltage-Divider Configuration Zi Zo Av Ai Unbypassed Emitter-Bias Configuration Zi Zo Av Ai Summary Tables (Unloaded BJT Amplifiers) Summary Tables (Unloaded BJT Amplifiers) Emitter-Follower Configuration Zi Zo Emitter-Follower Configuration Av Ai Ai h fe RB RB Z b The CE h-parameters and components of the re model are related by: hie = re hfe = hob = 1/ro Common-Base Configuration Zi Zo Av Ai Example 5.21 For the network of Figure, determine a. Zi b. Zo c. Av d. Ai 5.21 Complete Hybrid Equivalent Model 5.21 Complete Hybrid Equivalent Model Current gain, Ai=Io/Ii 5.21 Complete Hybrid Equivalent Model Voltage Gain, Av=Vo/Vi 5.21 Complete Hybrid Equivalent Model Input Impedance, Zi=Vi/Ii 5.21 Complete Hybrid Equivalent Model 5.21 Complete Hybrid Equivalent Model Output Impedance, Zo=Vo/Io 5.21 Complete Hybrid Equivalent Model Example 5.22 For the network of Figure, determine the following parameters using the complete hybrid equivalent model and compare to the results obtained using the approximate model. Example 5.22 Example 5.22 ETh VS RTh RS 1k Example 5.22 Part (a), Zi and 𝒁′𝒊 Example 5.22 Part (b), Av Example 5.22 Part (c), Ai Example 5.22 Part (d), Zo and 𝒁′𝒐 1 V Zo o I o hoe [h fe hre (hie RS )] Z o RC Z o 4.7 k 86.66k 4.46k Example 5.23 For the CB amplifier of Figure, determine the following parameters using the complete hybrid equivalent model and compare to the results obtained using the approximate model. a. Zi b. Ai c. Av d. Zo Example 5.23 Example 5.23 RTh 3k 1k 0.75k Example 5.23 Example 5.23 Part (a), Zi Example 5.23 Part (b), Ai Example 5.23 Part (c), Av Example 5.23 Part (d), Zo 5.22 Hybrid π Model The hybrid p model is most useful for analysis of high-frequency transistor applications. All the capacitors that appear are stray parasitic capacitors between the various junctions of the device At low to mid frequencies the stray capacitive effects can be ignored due to very high reactance levels associated with them. Giacoletto (or hybrid π) high-frequency transistor small-signal ac equivalent circuit. 5.22 Hybrid π Model The resistance rb includes the base contact, base bulk and base spreading resistance levels. The first is due to the actual connection to the base. The second includes the resistance from the external terminal to the active region of the transistor. And, the last is the actual resistance within the active base region. The resistance rb is usually so small it can be replaced by a shortcircuit equivalent. The resistance rπ is simply βre as introduced for the CE re model. The symbol π has been used to agree with the hybrid π model. The resistance ru is a very large resistance which provides a feedback path from output to input circuits in the equivalent model. The subscript u refers to the union it provides between collector and base terminals. 5.22 Hybrid π Model The resistance ru is usually so large it can be ignored for most applications. The result is an equivalent network similar to the re model. Following relationships are used to extract the parameter values from the data typically provided: The hybrid π model will not appear in the small signal analysis but it is primarily used to investigate high frequency effects. Electronic Devices and Circuit Field-Effect Transistors (FETs) Department of Electronic Engineering The Islamia University of Bahawalpur, Pakistan Chapter Outline 1) Introduction 2) Construction and Characteristics of JFETs 3) Transfer Characteristics 4) Specification Sheets (JFETs) 5) Instrumentation 6) Important Relationships 7) Depletion-Type MOSFET 8) Enhancement-Type MOSFET 9) MOSFET Handling 10) VMOS 11) CMOS 12) MESFETs 13) Summary Table 6.1 Introduction The Field - Effect Transistor (FET) is a three terminal device used for a variety of applications that match, to a large extent, those of the BJT described in Chapters 3 through 5. Although, there are important differences between the two types of devices, there are also many similarities, which will be pointed out in the discussions to follow. Just as there are npn and pnp bipolar transistors, there are n-channel and p-channel field-effect transistors. BJT transistor is a bipolar device – the prefix bi indicates that the conduction level is a function of two charge carriers, electrons and holes. The FET is a unipolar device depending solely on either electron (nchannel) or hole (p-channel) conduction. 6.1 Introduction The BJT transistor is a current-controlled device whereas the JFET transistor is a voltage-controlled device. In other words, the current IC is a direct function of the level of IB in the case of BJT. For the FET the current ID will be a function of voltage VGS applied to the input circuit. In each case the current of the output circuit is controlled by a parameter of the input circuit – in one case a current level and in the other an applied voltage. 6.1 Introduction The term field effect in the name deserves some explanation. We are familiar with the ability of a permanent magnet to draw metal filings to itself without the need for actual contact. The magnetic field of the permanent magnet envelopes the filings and attracts them to the magnet because the magnetic flux lines act so as to be as short as possible. For the FET an electric field is established by the charges present, which controls the conduction path of the output circuit without the need for direct contact between the controlling and controlled quantities. 6.1 Introduction One of the most important characteristics of the FET is its high input impedance as compared to BJT. It is 1MΩ to several hundred MΩ, which far exceeds the typical input resistance levels of BJT transistor configurations – a very important characteristic in the design of linear AC amplifiers. BJT transistor has a much higher sensitivity to changes in the applied signal. In other words, the variation in output current is typically a great deal more for BJTs than for FETs for the same change in applied voltage. For this reason: Typical AC voltage gains for BJT amplifiers are a great deal more than for FETs. FETs are more temperature stable than BJTs. FETs are usually smaller than BJTs, making them particularly useful in integrated-circuit (IC) chips. 6.1 Introduction Types of FETs JFET ~ Junction Field-Effect Transistor n-Channel JFET p-Channel JFET MOSFET ~ Metal-Oxide Field-Effect Transistor D-MOSFET ~ Depletion MOSFET E-MOSFET ~ Enhancement MOSFET MESFET ~ Metal Semiconductor Field-Effect Transistor 6.1 Introduction The MOSFET transistor has become one of the most important devices used in the design and construction of integrated circuits. Its thermal stability and other general characteristics make it extremely popular in computer circuit design. The MESFET is a more recent development and takes full advantage of the high-speed characteristics of GaAs as the base semiconductor material. Although, currently the more expensive option, the cost issue is often outweighed by the need for higher speeds in RF and computer designs. 6.2 Construction and Characteristics of JFETs JFET Construction There are three terminals: Drain (D) Source (S) Gate (G) Drain (D) and Source (S) are connected to n-channel Gate (G) is connected to the two p-type materials How JFET works? 6.2 Construction and Characteristics of JFETs The source of water pressure can be likened to the applied voltage from drain to source, which establishes a flow of water (electrons) from the spigot (source). The “gate” through an applied signal (potential), controls the flow of water (charge) to the “drain”. Water analogy for the JFET control mechanism 6.2 Construction and Characteristics of JFETs JFET Operating Characteristics There are three basic operating conditions for a JFET: a) VGS = 0, VDS increasing to some positive value b) VGS < 0, VDS at some positive value c) Voltage-Controlled Resistor a) VGS = 0V, VDS Increasing to Some Positive Value A positive voltage VDS is applied across the channel and gate is connected directly to the source to establish the condition VGS = 0V. The result is a gate and a source terminal at the same potential and a depletion region in the low end of each p-material similar to the distribution of no-bias conditions. The instant the voltage VDS is applied, the electrons are drawn to the drain terminal, establishing the conventional current ID with the defined direction of Figure. The path of charge flow clearly reveals that the drain and source currents are equivalent (ID = IS). a) VGS = 0V, VDS Increasing to Some Positive Value Note that the depletion region is wider near the top of both p-type materials. The reason for the change in width of the region is best described through the help of Figure. We can break down the resistance of the channel into the divisions. The current ID will establish the voltage levels through the channel. The result is that the upper region of the p-type material will be reverse biased by about 1.5V, with the lower region only reverse-biased by 0.5V. a) VGS = 0V, VDS Increasing to Some Positive Value Recall from the diode operation, greater the applied reverse bias, the wider is the depletion region. Hence, the distribution of depletion region as shown in Figure. The fact that the p-n junction is reverse biased for the length of the channel results in a gate current of zero amperes, as shown in same Figure. As voltage VDS is increased from 0V to a few volts, the current will increase as determined by Ohm’s law and the plot of ID versus VDS will appear as shown. For the region of low values of VDS, the resistance is essentially constant. a) VGS = 0V, VDS Increasing to Some Positive Value As VDS increases and approaches a level referred to as VP, the depletion region will widen, causing a noticeable reduction in the channel width. The reduced path of conduction causes the resistance to increase and the curve in the graph occurs. The more horizontal the curve, the higher the resistance, suggesting that the resistance is approaching “infinite” ohms in horizontal region. Pinch-off Voltage & Saturation If VGS = 0 and VDS is further increased to a more positive voltage, then the depletion zone gets so large that it pinches off the n-channel. This suggests that the current in the n-channel (ID) would drop to 0A, but ID maintains a saturation level defined as IDSS. The level of VDS that establishes this condition is referred to as the pinchoff voltage and is denoted by VP. In reality a very small channel still exists, with a current of very high density. Current Source Equivalent for VGS = 0V, VDS > VP In essence, once VDS > VP the JFET has the characteristics of a current source. As shown in Figure, the current is fixed at ID = IDSS, but the voltage VDS (for levels > VP) is determined by the applied load. The choice of IDSS is derived from the fact that it is the drain-tosource current with a short-circuit connection from gate to source. B) VGS < 0, VDS at some positive value VGS is the controlling voltage of JFET. As various curves for IC versus VCE were established for different levels of IB for the BJT, curves of ID versus VDS for various levels of VGS can be developed for the JFET. For the n-channel device the controlling voltage VGS is made more and more negative from its VGS = 0V level. In Figure, a negative voltage of -1V is applied between the gate and source terminals for a low level of VDS. The effect of the applied negative-bias VGS is to establish depletion regions similar to those obtained with VGS = 0V, but at lower levels of VDS. Therefore, the result of applying a negative bias to the gate is to reach saturation level at a lower level of VDS, as shown for VGS = -1V. B) VGS < 0, VDS at some positive value The resulting saturation level for ID has been reduced and in fact will continue to decrease as VGS is made more and more negative. The pinch-off voltage continues to drop in a parabolic manner as VGS becomes more and more negative. Eventually, VGS when VGS = -VP will be sufficiently negative to establish a saturation level that is essentially 0mA, and for all practical purposes the device has been “turned off.” In summary: The level of VGS that results in ID = 0mA is defined by VGS = VP, with VP being a negative voltage for n-channel and a positive voltage for pchannel JFETs. B) VGS < 0, VDS at some positive value On most specification sheets the pinch-off voltage is specified as VGS(off) rather than VP. The region to the right of the pinch-off locus of Figure is the region typically employed in linear amplifiers (amplifiers with minimum distortion of the applied signal) and is commonly referred to as the constant-current, saturation or linear amplification region. C) Voltage-Controlled Resistor The region to the left of the pinch-off locus is called the ohmic or voltage-controlled resistance region. In this region, the JFET can actually be employed as a variable resistor (possibly for an automatic gain control system) whose resistance is controlled by the applied gateto-source voltage. Note in Figure that the slope of each curve and therefore the resistance of the device between drain and source for VDS < VP are a function of the applied voltage VGS. C) Voltage-Controlled Resistor As VGS becomes more and more negative, the slope of each curve becomes more and more horizontal, corresponding to an increasing resistance level. The following equation provides a good first approximation to the resistance level in terms of the applied voltage VGS: rd ro ( 1 VGS VP )2 Where ro is the resistance with VGS = 0V and rd is the resistance at a particular level of VGS. And as Summary in Practical… p-Channel JFETs p-Channel JFET is constructed in exactly the same manner as the nchannel device but with a reversal of the p and n type materials. The defined current directions are reversed, as are the actual polarities for the voltages VGS and VDS. The channel will be constricted by increasing positive voltages from gate to source and negative voltages for VDS on the characteristics of Figure which has an IDSS of 6mA and a pinch-off voltage of VGS = +6V. Note at high levels of VDS that the curves suddenly rise to levels that seem unbounded. p-Channel JFETs The vertical rise is an indication that breakdown has occurred and the current through the channel is now limited solely by the external circuit. Although not appearing for nchannel device but they do occur for the n-channel device if sufficient voltage is applied. This region can be avoided if the level of VDSmax is noted on the specification sheet and the design is such that the actual level of VDS is less than this value for all values of VGS. JFET Symbols The arrow is pointing-in for the n-channel device to represent the direction in which IG would flow if the p-n junction were forward biased. For the p-channel device the only difference in the symbol is the direction of the arrow. Summary A few important parameters and relationships that will surface frequently in the analysis to follow in this chapter and the next for n-channel JFETs are: The maximum current is defined as IDSS and occurs when VGS = 0V and VDS ≥ |VP| For VGS less than (more negative than) the pinch off level, the drain current is ID = 0A Summary For all levels of VGS between 0V and pinch-off level, the current ID will range between IDSS and 0A, respectively. 6.3 Transfer Characteristics For BJT, the output current IC and the input controlling current IB are related by beta, which was considered to be constant. A linear relationship exists between IC and IB. Double the level of IB and IC will increase by a factor of two also. This linear relationship does not exist between the output and input quantities of a JFET. The relation between ID and VGS is defined by Shockley’s equation. The squared term results in a non-linear relationship between ID and VGS, producing a curve that grows exponentially with decreasing magnitude of VGS. 6.3 Transfer Characteristics For the dc analysis, a graphical rather than a mathematical approach will in general be more direct and easier to apply. The graphical approach will require a plot of Shockley’s equation to represent the device and a plot of the network equation relating the same variables. The solution is defined by the point of intersection of the two curves. When applying graphical approach, the device characteristics will be unaffected by the network in which the device is employed. Applying Shockley’s Equation VGS 2V , I D 2mA VGS 3V , I D 0.5mA Transfer Curve From this graph it is easy to determine the value of ID for a given value of VGS. Applying Shockley’s Equation By using basic algebra, we can find the value of VGS for a given level of ID. For ID = 4.5mA, Which is same as obtained earlier. Shorthand method Transfer curve must be plotted so frequently, it would be advantageous to have a shorthand method, while maintaining an acceptable degree of accuracy. It we specify VGS to be one-half the pinch off value VP, the resulting level of ID would be, It is general equation for any level of VP as long as VGS = VP/2. Shorthand method If we choose ID = IDSS/2 and put in equation. Additional points can be determined and the transfer curve can be sketched to a satisfactory level of accuracy by simply using the four plot points defined in table. Example 6.1 Sketch the transfer curve defined by IDSS = 12 mA and VP = -6 V. VGS 0 0.3VP = -1.8V 0.5VP = -3V ID IDSS = 12mA IDSS = 6mA IDSS = 3mA VP 0mA Example 6.2 Sketch the transfer curve defined by IDSS = 4 mA and VP = 3 V. VGS ID 0 0.3VP = 0.9V 0.5VP = 1.5V VP IDSS = 4mA IDSS/2 = 2mA IDSS/4 = 1mA 0mA 6.4 Specification Sheet (JFETs) Maximum Ratings The maximum rating list usually appears with the maximum voltages between specific terminals, maximum current levels and the maximum power dissipation level of the device. Any good design will try to avoid maximum levels by a good margin of safety. The term VGSR defines the maximum voltage with the source positive with respect to the gate before breakdown will occur. In some sheets referred as BVDSS – the breakdown voltage with the drain-source shorted (VDS = 0V). Normally designed to operate with IG = 0mA, if forced to accept a gate current, it could withstand 10mA before damage would occur. The normal power dissipation of device at 25ºC and normal operating conditions is defined as Electrical Characteristics These characteristics include the level of VP in the “off” characteristics and IDSS in the “on” characteristics. In this case typical values are shown. Both will vary from device to device. The small signal characteristics are discussed in Chapter 8. Case Construction and Terminal Identification This information is also available on the specification sheet. JFETs are also available in top-hat containers. Operating Region Ohmic region defines the minimum permissible values of VDS at each level of VGS VDSmax specifies the maximum value for this parameter. The shaded region is normal operating region for amplifier design. 6.5 Instrumentation 6.6 Important Relationships MOSFETs MOSFETs have characteristics similar to JFETs and additional characteristics that make them very useful. There are 2 types: Depletion-Type MOSFET Enhancement-Type MOSFET 6.7 Depletion-Type MOSFET Basic Construction Depletion-type MOSFET has characteristics similar to JFET between cutoff and saturation at IDSS, and also has the added feature of characteristics that extend into the region of opposite polarity for VGS. A slab of p-type material is formed from a silicon base and is referred to as substrate. It is the foundation on which the device is constructed. In some cases, the substrate is internally connected to the source terminal. 6.7 Depletion-Type MOSFET Basic Construction However, many discrete devices provide an additional terminal labeled SS, resulting in a four terminal device. The source and drain terminals are connected through metallic contacts to n-doped regions linked by an nchannel. The gate is also connected to a metal contact surface but remains insulated from the n-channel by a very thin silicon dioxide (SiO2) layer. The n-doped material lies on a pdoped substrate that may have an additional terminal connection called SS. 6.7 Depletion-Type MOSFET Basic Construction SiO2 is a type of insulator referred to as a dielectric, which sets up opposing electric fields within the dielectric when exposed to an externally applied field. SiO2 layer is an insulating layer means that there is no direct connection between the gate terminal and the channel of a MOSFET. It is the insulating layer of SiO2 in the MOSFET construction that accounts for the very desirable high input impedance of the device. Input impedance of most JFETs is high, the input impedance of MOSFET is usually higher than that of JFET. Because of very high input impedance, the gate current IG is essentially 0A for dc-biased configurations. Basic Operation and Characteristics VGS is set to 0V by the direct connection from one terminal to the other and a voltage VDS is applied across the drain-to-source terminals. The resulting current for VGS = 0V is labeled as IDSS. Basic Operation and Characteristics Then VGS is set to a negative voltage such as -1V. The negative potential at the gate will tend to pressure electrons toward the p-type substrate (like charges repel) and attract holes from the p-type substrate (opposite charges attract), as shown in Figure. A level of recombination between electrons and holes will occur that will reduce the no. of free electrons in the n-channel available for conduction. The more negative the bias, the higher is the rate of recombination. Basic Operation and Characteristics The resulting level of drain current is therefore reduced with increasing negative bias for VGS, as shown in Figure. For positive values of VGS, the positive gate will draw additional free electrons from the p-type substrate due to the reverse leakage current and establish new carriers through the collisions resulting between accelerating particles. Basic Operation and Characteristics As the VGS continues in increase in positive direction, the gate current will increase at a rapid rate. The user must be aware of the maximum drain current rating since it could be exceeded with a positive gate voltage. As the application of positive VGS has “enhanced” the level of free carriers in the channel compared to that encountered with VGS = 0V. For this reason, the region of positive gate voltages on the transfer characteristics is often referred to as the enhancement region. With the region between cutoff and the saturation level of IDSS referred to as the depletion region. Shockley’s equation will continue to apply for the depletion-type MOSFET characteristics in both the depletion and enhancement regions. For both regions, simply proper sign of VGS will be included. p-Channel Depletion-Type MOSFET The p-channel Depletion-type MOSFET is similar to the n-channel except that the voltage polarities and current directions are reversed. Symbols The symbols chosen try to reflect the actual construction of the device. The lack of direct connection due to the gate insulation between the gate and the channel is represented by a space between gate and other terminals of the symbol. The vertical line representing the channel is connected between the drain and the source and is “supported” by the substrate. Specification Sheet 6.8 Enhancement-Type MOSFET Although some similarities in construction and mode of operation between depletion and enhancement type MOSFETs. The characteristics of the enhancement type MOSFET are quite different from anything studied so far. The transfer curve is not defined by Shockley’s equation. The drain current is now cutoff until VGS reaches a specific value. Current control in an n-channel device is now effected by a positive VGS rather than the range of negative values encountered for n-channel JFETs and n-channel depletion type MOSFETs. 6.8 Enhancement-Type MOSFET Basic Construction As with depletion type MOSFET, the substrate is sometimes internally connected to the source terminal. But, note the absence of a channel between the two n-doped regions. The SiO2 layer is still present to isolate the gate metallic platform from the region between the drain and source. In summary, the construction is similar to the depletion-type MOSFET, except the absence of a channel between the drain and source terminals. 6.8 Enhancement-Type MOSFET Basic Operation and Characteristics If VGS is 0V and a voltage is applied between the drain and source, the absence of n-channel will result in a current of effectively 0A. It is quite different from the JFET and depletion type MOSFET, where ID = IDSS. With VDS some positive voltage, VGS at 0V, and terminal SS directly connected to the source, there are in fact two reverse-biased p-n junctions between the n-doped regions and the p-substrate to oppose any significant flow between the drain and source. 6.8 Enhancement-Type MOSFET Basic Operation and Characteristics Both VDS and VGS have been set at some positive voltage, establishing the drain and the gate at a positive potential with respect to the source. The positive potential at gate will pressure the holes (since like charges repel) in the p-substrate along the edge of the SiO2 layer to leave the area and enter deeper regions of the p-substrate. The result is a depletion region near the SiO2 insulating layer void of holes. Basic Operation and Characteristics However, the electrons in the psubstrate (the minority carriers of the material) will be attracted to the positive gate and accumulate in the region near the surface of SiO2 layer. The SiO2 layer and its insulating qualities will prevent the negative carriers from being absorbed at the gate terminal. As VGS increases in magnitude, the concentration of electrons near the SiO2 surface increases until eventually the induced n-type region can support a measureable flow between drain and source. Basic Operation and Characteristics The level of VGS that results in the significant increase in drain current is called the threshold voltage, VT Since, the channel is non-existent with VGS = 0V and “enhanced” by the application of a positive gateto-source voltage, this type of MOSFET is called and enhancement-type MOSFET. Both depletion and enhancement type MOSFETs have enhancement type regions, but the label was applied to latter since it is its only mode of operation. Basic Operation and Characteristics As VGS is increased beyond the threshold level, the density of free carriers in the induced channel will increase, resulting in an increased level of drain current. However, if we hold VGS constant and increase the level of VDS, the drain current will eventually reach a saturation level as occurred for JFET and depletion type MOSFET. The levelling off of ID is due to a Applying KVL to the terminal pinching-off process depicted by voltages of the MOSFET, the narrower channel at the drain VDG VDS VGS end of the induced channel. Basic Operation and Characteristics If VGS is held fixed at some value such as 8V and VDS is increased from 2V to 5V, the voltage VDG will drop from -6V to -3V and the gate will become less and less positive with respect to the drain. The reduction in VDG will in turn reduce the attractive forces for free carriers (electrons) in this region of the induced channel, causing a reduction in the effective channel width. Eventually, the channel will be reduced to the point of pinch-off and a saturation condition will be established as earlier described for JFET and depletion-type MOSFET. In other words, any further increase in VDS at the fixed level of VGS will not effect the saturation level of ID until breakdown conditions are encountered. The drain characteristics of Figure reveal that for the given device with VGS = 8V, saturation occurs at a level of VDS = 6V. In fact, the saturation level for VDS is related to the applied VGS by Basic Operation and Characteristics Hence, for fixed value of VT, higher the level of VGS, the greater the saturation level for VDS, as shown by the locus of saturation levels. For values of VGS less than the threshold level, the drain current of an enhancement type MOSFET is 0mA. Basic Operation and Characteristics For VGS > VT, the drain current is related to the applied VGS by the following non-linear relationship: I D k (VGS VT ) 2 The k term is a constant that is a function of the construction of the device. The value of k can be determined from the equation, k I D(on) (VGS(ON ) VT )2 Where ID(on) and VGS(on) are the values for each at a particular point on the characteristics of the device. Basic Operation and Characteristics Basic Operation and Characteristics For the dc analysis of enhancement-type MOSFET, the transfer characteristics will again be employed in graphical solution. In this case, ID is 0mA for VGS ≤ VT. Above this point, a measureable current for ID and will increase defined by equation I D k (VGS VT ) 2 Basic Operation and Characteristics The transfer curve is quite different from those obtained earlier. For an n-channel (induced) device, it is now totally in the positive VGS region and does not rise until VGS = VT. How to plot the transfer characteristics given the levels of k and VT as included below for a particular MOSFET: First, a horizontal line is drawn at ID = 0mA from VGS=0V to VGS =4V. Basic Operation and Characteristics Next, a level of VGS greater than VT such as 5V is chosen and substituted into the equation to determine the resulting level of ID as follows: Finally, additional levels of VGS are chosen and the resulting levels of ID are obtained. Example 6.4 Example 6.4 p-Channel Enhancement-Type MOSFET The construction is exactly the reverse of n-channel enhancement type MOSFET. All the voltage polarities and the current directions are reversed. Symbols Specification Sheet 6.9 MOSFET Handling There is often sufficient accumulation of static charge (picked up from the surroundings) to establish a potential difference across the thin layer that can break down the layer and establish conduction through it. Hence, it is imperative to leave the shorting shipping foil (or ring) connecting the leads of the device together until the device is to be inserted in the system. With the ring, the potential difference between any two terminals is maintained at 0V. There are often transients (sharp changes in current or voltage) in a network when elements are removed or inserted if the power is on. The transient levels can often be more than the device can handle. Therefore, the power should always be off when network changes are made. 6.9 MOSFET Handling One method of ensuring that maximum VGS is not exceeded (perhaps by transient effects) for either polarity is to introduce two Zener diodes. One disadvantage introduced by Zener protection is that the off resistance of a Zener diode is less than the input impedance established by the SiO2 layer. The result is a reduction in input impedance but it is still high enough for most applications. 6.10 VMOS (Vertical MOSFET) One of the disadvantages of the typical MOSFET is the reduced power handling levels (typically, less than 1W) compared to BJT transistors. This shortfall for a device with so many positive characteristics can be softened by changing the construction mode from one of a planar nature to one with a vertical structure. All elements of the planar MOSFET are present in the vertical MOS. The term vertical is due to the fact that the channel is now formed in the vertical direction rather than horizontal direction as for the planar devices. The channel also has the appearance of a “V” cut in the semiconductor base which is often used a characteristic for the memorization of the name of the device. 6.10 VMOS (Vertical MOSFET) The application of a positive voltage to the drain and a negative voltage to the source with the gate at 0V or some typical positive “on” level results in the induced n-channel in the narrower ptype region of the device. The length of the channel is now defined by the vertical height of the p-region, which can be made significantly less than that of a channel using planar construction. 6.10 VMOS (Vertical MOSFET) Since decreasing channel length results in reduced resistance levels, the power dissipation level of the device (power lost in the form of heat) at operating current levels will be reduced. In addition, the contact area between the channel and n+ region is greatly increased by the vertical mode construction, contributing to further decrease in the resistance level and an increased area for current between the doping layers. There is also the existence of two conduction paths between drain and source, to further contribute to a higher current rating. The net result is a device with drain currents that can reach the ampere levels with power levels exceeding 10W. Compared with commercially available planar MOSFETs, VMOS FETs have reduced channel resistance levels and higher current and power ratings. 6.10 VMOS (Vertical MOSFET) VMOS FETs have a positive temperature coefficient, which combats the possibility of thermal runaway. o If the temperature of the device is increased, the resistance levels will increase, causing a reduction in drain current rather than an increase as encountered for a conventional device. o Negative temperature coefficients result in decreased resistance levels with increase in temperature, which fuel the growing current levels and result in further temperature instability and thermal runaway. The reduced charge storage levels result in faster switching times for VMOS construction compared to those for conventional planar construction. o In fact, VMOS devices typically have switching times less than onehalf that encountered for the typical BJT transistor. 6.11 CMOS A very effective logic circuit can be established by constructing a pchannel and an n-channel MOSFET on the same substrate. The configuration is referred to as a complementary MOSFET arrangement (CMOS) which has extensive applications in computer logic design. The relatively high input impedance, fast switching speeds and lower operating power levels of the CMOS configuration have resulted in a whole new discipline referred to as CMOS logic design. 6.11 CMOS One very effective use of this arrangement is an inverter. An inverter is a logic element that “inverts” the applied signal. 6.12 MESFETs The production of FETs using a Schottky barrier at the gate can be done quite efficiently. Schottky barriers are barriers established by depositing a metal such as tungsten on an n-type channel. Use of Schottky barrier at the gate is the major difference from depletion and enhancement-type MOSFETs, which employs an insulating barrier between the metal contact and the n-type channel. 6.12 MESFETs The absence of an insulating layer reduces the distance between the metal contact surface of the gate and the semiconductor layer, resulting in a lower level of stray capacitance between two surfaces. The result of the lower capacitance level is a reduced sensitivity to high frequencies, which further supports the high mobility of carriers in the GaAs material. The presence of a metal-semiconductor junction is the reason such FETs are called MESFETs. 6.12 MESFETs When a negative voltage is applied, it will pressure electrons towards the p-type substrate reducing the no. of carriers in the channel. The result is a reduced drain current for increasing values of negative voltage at the gate terminal. For positive voltages at the gate, additional electrons will be attracted into the channel and the current will rise. Drain and transfer characteristics are similar to those of depletiontype MOSFET results in same analysis techniques. 6.12 MESFETs There are also the enhancement-type MESFETs with construction same as depletion-type MESFETs except that there is no initial channel between drain and source. The response and characteristics are same as enhancement-type MOSFET. 6.12 MESFETs Due to the Schottky barrier at gate, the positive threshold voltage is limited to 0V to about 0.4V. The channel must be an n-type material in a MESFET. The mobility of holes in GaAs is relatively low compared to that of negatively charged carriers, losing the advantage of using GaAs for high-speed applications. Only n-type MESFETs are commercially available. 6.13 Summary Table 6.13 Summary Table ELEC - 01211 Electronic Devices and Circuit Theory FET Biasing Department of Electronic Engineering The Islamia University of Bahawalpur, Pakistan Chapter Outline 1) Introduction 2) Fixed-Bias Configuration 3) Self-Bias Configuration 4) Voltage-Divider Biasing 5) Common Gate Configuration 6) Special Case VGSQ = 0V 7) Depletion-Type MOSFETs 8) Enhancement-Type MOSFETs 9) Summary Table 10) Combination Networks 11) Design 12) Troubleshooting 13) p-Channel FETs 14) Universal JFET Bias Curve FETs FET JFET n-channel & p-channel MOSFET Depletion-type MESFET n-channel Depletion MOSFET n-channel & p-channel MESFET Enhancement-type MESFET n-channel Enhancement MOSFET n-channel & p-channel 7.1 Introduction The BJT transistor is a current-controlled device whereas the JFET transistor is a voltage-controlled device. In other words, the current IC is a direct function of the level of IB in the case of BJT. For the FET the current ID will be a function of voltage VGS applied to the input circuit. In each case the current of the output circuit is controlled by a parameter of the input circuit – in one case a current level and in the other an applied voltage. Introduction The general relationships which can be applied to the dc analysis of all FET amplifiers are: For all FET Amplifiers: IG 0 A ID IS For enhancement-type MOSFETs and MESFETs: I D k(VGS VT ) 2 k I D(on) (VGS(ON ) VT )2 For JFETs and depletion-type MOSFETs and MESFETs: VGS I D I DSS 1 VP 2 7.2 Fixed-Bias Configuration It is one of the few FET configurations that can be solved just as directly using either mathematical or a graphical approach. Resistor RG is present to ensure that Vi appear at the input to the FET amplifier for the ac analysis (Chap # 8). For dc analysis, IG 0 A VRG I G RG (0) RG 0V The zero voltage drop across RG permits replacing RG by a short circuit equivalent. 7.2 Fixed-Bias Configuration The negative terminal of the battery is connected directly to the defined positive potential of VGS, clearly reveals that polarity of it is directly opposite to VGG. VGG VGS 0 VGS VGG Since VGG is a fixed dc supply, the voltage VGS is fixed in magnitude, resulting in the designation “fixed bias”. Since VGS is fixed in quantity for this configuration, its magnitude can be simply substituted in Shockley’s equation and level of ID is calculated. Network for dc analysis. 7.2 Fixed-Bias Configuration Plotting Shockley’s equation. Finding the solution for the fixed-bias configuration. 7.2 Fixed-Bias Configuration Drain to Source KVL Example 7.1 Determine the following for the network. a. VGSQ. b. IDQ. c. VDS. d. VD. e. VG. f. VS. Mathematical Approach Example 7.1 Graphical Approach 7.3 Self-Bias Configuration Self-bias configuration eliminate the need for two dc supplies. The controlling gate-to-source voltage is now determined by the voltage RS introduced in the source leg of the configuration. For the dc analysis, capacitors can be replaced by “open circuit” and the resistor RG replaced by shortcircuit equivalent since IG = 0A. 7.3 Self-Bias Configuration Mathematical Solution Note, VGS is the function of output current ID and not fixed in magnitude as occurred for fixed bias configuration. 7.3 Self-Bias Configuration A mathematical solution could be obtained by substituting the value of VGS in Shockley’s equation as follows: By solving, we obtain an equation of the following form: Solution of this quadratic equation will lead to appropriate ID. 7.3 Self-Bias Configuration Graphical Approach a) Plotting Shockley’s Equation b) Sketching the self-bias line, we have to identify two points on the graph and then simply draw a line between the two points. The most obvious condition to apply is ID = 0A, since it results in VGS = 0V. VGS I D RS (0 A) RS 0V 7.3 Self-Bias Configuration The second point requires that a level of VGS or ID be chosen and the corresponding level of other quantity be determined. 7.3 Self-Bias Configuration Applying KVL at the output loop Example 7.2 Determine the following for the network. a. VGSQ b. IDQ c. VDS d. VS e. VG f. VD Example 7.2 Graphical Approach Sketching the self-bias line Example 7.2 Plotting Shockley’s Equation Example 7.2 Part (a) & (b) Example 7.2 Part (c) Part (d) Part (e) Part (f) Example 7.3 Find the quiescent point for the network of Figure if: a. RS = 100Ω. b. RS = 10kΩ. VGS I D RS VGS (4mA)(100) VGS 0.4V Example 7.3 VGS I D RS VGS (4mA)(10k ) VGS 40V VGS I D RS 4V I D (10k ) I D 0.4mA 7.4 Voltage-Divider Biasing 7.4 Voltage-Divider Biasing Applying KVL in clockwise direction to the indicated loop results in: The result is an equation that continues to include the same two variables appearing in Shockley’s equation. The quantities VG and RS are fixed by the network construction. We require two points to draw a straight line, to represent the network characteristics. 7.4 Voltage-Divider Biasing If we select ID = 0mA, we can find a point at the horizontal line, For other point, we employ the fact that at any point on vertical axis VGS = 0V, and solve for ID, 7.4 Voltage-Divider Biasing Increasing values of RS result lower in quiescent values of ID and more negative values of VGS. 7.4 Voltage-Divider Biasing Once the value of VGS and ID are determined at Q-point, the remaining network analysis can be performed in usual manner. Graphical Approach Step 1 Plot a line using network equation at two points: VGS VG I D RS •If ID =0 VGS = VG •If VGS = 0 ID = VG / RS Step 2 Plot the transfer curve using shockley’s equation. ID V I DSS 1 GS VP 2 Step 3 The Q-point is located where the line intersects the transfer curve. Find IDQ and VGSQ Step 4 Use the IDQ and VGSQ to solve for the other variables. Example 7.5 Determine the following for the network. a. IDQ and VGSQ. b. VD. c. VS. d. VDS. e. VDG. Step 1 Example 7.5 Step 2 Step 3 Example 7.5 Step 4 Use the IDQ and VGSQ to solve for the other variables. 7.5 Common Gate Configuration Gate terminal is grounded, input signal is applied to the source terminal and the output signal is obtained at the drain terminal. 7.5 Common Gate Configuration The network equation can be determined by applying KVL, Applying the conditions ID = 0mA and then VGS = 0V to obtain the load line, 7.5 Common Gate Configuration The resulting intersection between the transfer curve for JFET and the load line defines the Q-point. 7.5 Common Gate Configuration Applying KVL at the entire output loop to obtain VDS, Example 7.6 Determine the following for the common gate configuration of Figure. a. VGSQ b. IDQ c. VDS d. VD e. VG f. VS For above equation, the origin is one point for the load line, the other is determined at some arbitrary point, Example 7.6 Part (a) Part (b) Example 7.6 Part (c) Part (d) Part (e) Part (f) 7.6 Special Case: 𝑽𝑮𝑺𝑸 = 0V It is a network of practical importance because of its relative simplicity. Direct connection of the gate and source terminals to ground results in VGS = 0V. This will result in a vertical load line at VGSQ = 0V as shown. 7.6 Special Case: 𝑽𝑮𝑺𝑸 = 0V Since the transfer curve of JFET will cross the vertical axis at IDSS, Applying KVL at the output loop, 7.7 Depletion-Type MOSFETs The similarities in appearance between the transfer curves of JFETs and depletion type MOSFETs permit a similar analysis of each in the dc domain. The primary difference is that depletion-type MOSFETs permit operating points will positive values of VGS and levels of ID that exceed IDSS. For all configurations discussed so far, the analysis is same if the JFET is replaced by depletion-type MOSFET. The only undefined part is how to plot Shockley’s equation for positive values of VGS. This required positive value will be already defined by the MOSFET parameters. A few examples will reveal the effect of change in device on the resulting analysis. Example 7.7 For the n-channel depletion-type MOSFET of Figure, determine: a. IDQ and VGSQ b. VDS VGS ID 0 IDSS = 6mA 0.3VP = -1V IDSS/2 = 3mA 0.5VP = -1.5V IDSS/4 = 1.5mA VP = -3V 0mA Defining a plot point at VGS = +1V by using Shockley’s equation, Example 7.7 Proceeding as described for voltage divider bias JFET configuration, Example 7.8 Repeat example 7.7 with RS = 150Ω. The plot points are the same for the transfer curve. For bias line, Part (a) Example 7.8 Part (b) Example 7.9 Determine the following for the network of Figure: a. IDQ and VGSQ b. VD For VGS < 0V, VGS ID 0 0.3VP = -2.4V 0.5VP = -4V IDSS = 8mA IDSS/2 = 4mA IDSS/4 = 2mA VP = -8V 0mA Example 7.9 For the network bias line, one point is located at the origin. The second point is plotted by choosing VGS = -6V. Example 7.9 Part (a) Part (b) Example 7.10 Determine VDS for the network of Figure: 7.8 Enhancement-Type MOSFETs The transfer characteristics are quite different from those encountered for the JFET and depletion-type MOSFET. For an n-channel enhancement-type MOSFET, the drain current is zero for all levels of VGS less than threshold level VGS(Th). For levels of VGS greater than VGS(Th), the drain current is, Since data sheet provide the threshold voltage and a level of drain current ID(on) and its corresponding level of VGS(on), two points are defined immediately as shown. 7.8 Enhancement-Type MOSFETs To complete the curve, the constant k must be determined from the specification sheet data and solving for k : Once k is defined, other levels of ID can be determined for chosen values of VGS. Typically, a point between VGS(Th) and VGS(on), and one just greater than VGS(on) will provide a sufficient no. of points to plot. 7.8 Enhancement-Type MOSFETs Feedback Biasing Arrangement The resistor RG brings a suitably large voltage to the gate to drive the MOSFET “on”. Since IG = 0mA and 𝑉𝑅𝐺 = 0V, the dc equivalent network appears as shown. 7.8 Enhancement-Type MOSFETs Feedback Biasing Arrangement A direct connection now exists between drain and gate, resulting in Example 7.11 Determine 𝑽𝑫𝑺𝑸 and 𝑰𝑫𝑸 for the enhancement-type MOSFET of Figure. Example 7.11 For VGS = 10V (slightly greater than VGS(Th)), Example 7.11 7.8 Enhancement-Type MOSFETs Voltage Divider Biasing Arrangement Example 7.12 Determine 𝑽𝑫𝑺𝑸 , 𝑰𝑫𝑸 and VDS for the network of Figure. Example 7.12 Example 7.12 7.9 Summary Table 7.9 Summary Table 7.9 Summary Table 7.10 Combination Networks Example 7.13 Determine the levels of VD and VC for the network of Figure. VGS is an important quantity to determine or write an equation for when analyzing JFET networks. Since VGS is a level for which an immediate solution is not obvious, we turn our attention to transistor configuration. Recognizing voltage divider configuration where approximate technique can be applied, permitting determination of VB using VDR on the input circuit. RE 10 R2 288k 240k ( Satisfied ) Example 7.13 Example 7.13 How to determine VC? Both VCE and VDS are unknown quantities, preventing us from establishing a link between VD and VC or from VE to VD. More careful examination reveals that VC is linked to VB by VGS (assuming 𝑉𝑅𝐺 = 0𝑉). Since we know VB if VGS is found, VC can be determined from, The value of VGS can be found from Shockley’s equation, Example 7.13 The JFET transfer characteristics are first sketched. The level of 𝐼𝐷𝑄 is then established by a horizontal line. 𝑉𝐺𝑆𝑄 is then determined by dropping a line down from the operating point to the horizontal axis, resulting in Example 7.14 Determine VD for the network of Figure. For the self-biased JFET, we can derive an equation for VGS and determine the resulting Q-point using graphical technique. That is, VGS 0V I D 0 mA I D 1.67 mA V GS VP 4V Example 7.14 7.11 Design Requirement for designing is not limited only to dc conditions. The area of application, level of amplification desired, signal strength, and operating conditions are just few of the conditions that enter into the total design process. For example, if the levels of VD and ID are specified for the network of Figure, the level of 𝑉𝐺𝑆𝑄 can be determined from the plot of transfer curve and RS can be determined from, VGS I D RS If VDD is specified, the level of RD can then be calculated from, VDD VD RD ID 7.11 Design It is possible that only VDD and RD are specified together with the level of VDS. The device to be employed may have to be specified along with the level of RS. It appears logical that the device chosen should have a maximum VDS greater than the specified value by a safe margin. In general, it is good design practice for linear amplifiers to choose operating points that don’t crowd the saturation level (IDSS) or cutoff (VP) regions. Levels of 𝑉𝐺𝑆𝑄 close to VP/2 or levels of 𝐼𝐷𝑄 near IDSS/2 are certainly reasonable starting points in the design. In particular, if resistive elements are requested, the result is often obtained simply by applying Ohm’s law in the following form: Example 7.15 For the given network the levels of 𝑽𝑫𝑸 and 𝑰𝑫𝑸 are specified. Determine the required values of RD and RS. What are the closest standard commercial values? Example 7.15 Plotting the transfer curve and drawing a horizontal line at 𝐼𝐷𝑄 = 2.5𝑚𝐴 results in 𝑉𝐺𝑆𝑄 = −1𝑉, applying VGSQ I D RS Example 7.16 For the voltage divider bias configuration given, if VD = 12 V and VGSQ = -2 V, determine the value of RS. Example 7.17 The levels of VDS and ID are specified as VDS = 0.5VDD and ID = ID(on) for the network of Figure. Determine the levels of VDD and RD. 7.12 Troubleshooting In general, the troubleshooting process begins with a rechecking of the network construction and terminal connections. This is usually followed by the checking of voltage levels between specific terminals and ground or between terminals of the network. Current levels are seldom measured. For n-channel JFET amplifier, it is clearly understood that the value of VGS at Q-point is limited to 0V or a negative value as shown. The level of VDS is typically between 25% and 75% of VDD. A reading of 0V for VDS clearly indicates that either the output circuit has an “open” or the JFET is internally short-circuited between drain and source. 7.12 Troubleshooting If VD is VDD volts, there is no drop across RD, due to the lack of current through RD, and connections should be checked for continuity. If the level of VDS seems inappropriate, the continuity of output circuit can easily be checked by grounding the negative lead of the voltmeter and measuring the voltage levels from VDD to ground using the positive lead. If VD = VDD, the current through RD may be zero, but there is continuity between VD and VDD. If VS = VD, the device is not open between drain and source, but it is also not “on”. The continuity through to VS is confirmed, however. In this case, it is possible that poor ground connection exists between RS and ground that may not be obvious. 7.12 Troubleshooting The troubleshooter will simply have to narrow down the possible causes of malfunction. The continuity of a network can also be checked simply by measuring the voltage across any resistor of the network (except for RG in the JFET configuration). An indication of 0V reveals the lack of current through the element due to an open circuit in the network. The most sensitive element in the amplifier is BJT and FET itself. The application of excessive voltage during the construction or testing phase or the use of incorrect resistor values resulting in high current levels can destroy the device. In summary, the development of good troubleshooting technique comes from experience and a level of confidence in what to expect and why. 7.13 p-Channel FETs 7.13 p-Channel FETs Example 7.18 Determine IDQ, VGSQ and VDS for the p-channel JFET. Example 7.18 For VDS, KVL results in, 7.14 Universal JFET Bias Curve The dc solution of a FET configuration requires drawing the transfer curve for each analysis, a universal curve was developed that can be used for any level of IDSS and VP. The horizontal and vertical scales are normalized. The |VP| indicate that only the magnitude of VP is to be employed, not its sign. The vertical scale label m can be used to find the solution to fixed bias configurations. The other scale labeled M, is employed along with the m scale to find the solution to voltage divider configurations. The equations for m and M are: 7.14 Universal JFET Bias Curve 7.14 Universal JFET Bias Curve The scaling for m and M comes from mathematical development involving the network equations and normalized scaling. The description will not concentrate on why m scale extends from 0 to 5 at VGS/|VP| = -0.2 and the M scale ranges from 0 to 1 at VGS/|VP| = 0. But rather how to use the resulting scales to obtain a solution for the configuration. The beauty of this approach is the elimination of the need to sketch the transfer curve for each analysis, that the superposition of bias line is a great deal easier, and that the calculations are easier. Example 7.19 Determine the quiescent values of ID and VGS for the network of Figure. The self bias line defined by RS is plotted by drawing a straight line form the origin through a point defined by m = 0.31 as shown in Figure. Example 7.19 Example 7.19 Example 7.20 Determine the quiescent values of ID and VGS for the network of Figure. Example 7.20 Example 7.20 Example 7.20 Even the levels of IDSS and VP are different for the two networks, the same universal curve can be employed. ELEC - 01211 Electronic Circuit Design FET Amplifiers Department of Electronic Engineering The Islamia University of Bahawalpur, Pakistan Chapter Outline 1. 2. 3. 4. 5. 6. 7. Introduction JFET Small-Signal Model Fixed-Bias Configuration Self-Bias Configuration Voltage-Divider Configuration Common-Gate Configuration Source-Follower (CommonDrain) Configuration 8. Depletion-Type MOSFETs 9. Enhancement-Type MOSFETs 10. E-MOSFET Drain-Feedback Configuration 11. E-MOSFET Voltage-Divider Configuration 12. Designing FET Amplifier Networks 13. Summary Table 14. Effect of RL and Rsig 15. Cascade Configuration 1 – Introduction FETs provide: • • • • • Excellent voltage gain High input impedance Low-power consumption Good frequency range Minimum size and weight 1 – Introduction BJTs vs FETs : BJT device controls a large output (collector) current by means of a small input (base) current. i.e., BJT is a currentcontrolled device. FET device control an output (drain) current by means of a relatively small input (gate-voltage) voltage i.e., FET is voltage-controlled device. BJT has an amplification factor β. FET has a transconductance factor gm. Voltage gain of FET amplifier is generally less than that of BJT amplifier but FET amplifier provides a much higher input impedance than that of a BJT configuration. Output impedance values are comparable for FET and BJT. 1 – Introduction FETs Common-source configuration provides an inverted, amplified signal Common-drain (source-follower) circuit provides unity gain with no inversion Common-gate circuit provides gain with no inversion 2 – JFET Small-Signal Model The gate-to-source voltage controls the drain-to-source (channel) current of a JFET. The change in drain current that will result from a change in gate-tosource voltage can be determined using the transconductance factor gm in the following manner: The prefix trans- in the terminology applied to gm reveals that it establishes a relationship between an output and input quantity. The root word conductance was chosen because gm is determined by a current-to-voltage ratio similar to the relation that defines the conductance of a resistor, G = 1/R = I/V. 2 – JFET Small-Signal Model Outlines: 1. Graphical Determination of gm 2. Mathematical Definition of gm 3. Plotting gm versus VGS 4. Effect of ID on gm 5. JFET Input Impedance Zi 6. JFET Output Impedance Zo 7. JFET AC Equivalent Circuit 2 – JFET Small-Signal Model Graphical Determination of gm Examining the transfer characteristics, we find that gm is actually the slope of the characteristics at the point of operation. That is, The slope and, therefore, gm increases as we progress from VP to IDSS. In other words, as VGS approaches 0V, the magnitude of gm increases. Example 8.1 Determine the magnitude of gm for a JFET with IDSS = 8mA and VP = -4V at the following dc bias points: a. VGS = -0.5 V. b. VGS = -1.5 V. c. VGS = -2.5 V. Calculating gm at various bias points. 2 – JFET Small-Signal Model Mathematical Definition of gm Graphical procedure is limited by the accuracy of transfer plot and the care with which the changes in each quantity can be determined. An alternative approach to determining gm employs the approach used to find the ac resistance of a diode, where it states that: “The derivative of a function at a point is equal to the slope of the tangent line drawn at that point.” VGS I D I DSS 1 VP 2 2 – JFET Small-Signal Model 2 – JFET Small-Signal Model The slope of transfer curve is maximum at VGS = 0. It results in the equation for the maximum value of gm for a JFET. On specification sheets, gm is often provided as gfs or yfs. Where “y” indicates it is part of an admittance equivalent circuit. “f” signifies forward transfer conductance. “s” indicates that it is connected to the source terminal. Example 8.2 For the JFET having the transfer characteristics of example 8.1. a. Find the maximum value of gm. b. Find the value of gm at each operating point of example 8.1 and compare with the graphical results. Example 8.2 2 – JFET Small-Signal Model Plotting gm versus VGS Since the factor (1-VGS/VP) is less than 1 for any value of VGS other than 0V. The maximum value of gm occurs where VGS = 0V and the minimum value at VGS = VP . The more negative the value of VGS the less the value of gm. Example 8.3 Plot gm versus VGS for the JFET of example 8.1 and 8.2. Plot of gm versus VGS for a JFET with IDSS = 8mA and VP = -4 V. 2 – JFET Small-Signal Model Effect of ID on gm Relation between gm and the dc bias current ID can be derived by using Shockley’s equation. V I D I DSS 1 GS VP 2 Example 8.4 Plot gm versus ID for the JFET of example 8.1 through 8.3. I D I DSS , g m g m 0 4mS I D I DSS / 2, g m 0.707 g m 0 2.83mS I D I DSS / 4, g m 0.5 g m 0 2mS The highest values of gm are obtained when VGS approaches 0V and ID approaches its maximum value of IDSS. Plot of gm versus ID for a JFET with IDSS = 8mA and VGS = -4V. 2 – JFET Small-Signal Model JFET Input Impedance, Zi The input impedance of all commercially available JFETs is sufficiently large to assume that the input terminals approximate an open circuit. In equation form, For JFET a practical value of 109Ω (1000 MΩ) is typical, whereas a value of 1012Ω to 1015Ω is typical for MOSFETs and MESFETs. 2 – JFET Small-Signal Model JFET Output Impedance, Zo On JFET specification sheets, the output impedance will typically appear as gos or yos with the units of μS. The parameter “yos” is a component of an admittance equivalent circuit. The subscript “o” signifying an output network parameter and “s” is the terminal (source) to which it is attached in the model. 2 – JFET Small-Signal Model The output impedance is also defined on the characteristics as the slope of the horizontal characteristic curve at the point of operation. The more horizontal the curve, the greater is the output impedance. Example 8.5 Determine the output impedance for the FET of Fig. for VGS = 0V and VGS = -2 V at VDS = 8 V. Plot of gm versus ID for a JFET with IDSS = 8mA and VGS = -4V. Example 8.5 Plot of gm versus ID for a JFET with IDSS = 8mA and VGS = -4V. 2 – JFET Small-Signal Model JFET AC Equivalent Circuit The control of Id by Vgs is included as a current source gmVgs connected from drain to source. The current source has its arrow pointing from drain to source to establish a 1800 phase shift between output and input voltages as will occur in actual operation. The input impedance is represented by open circuit at input terminals and the output impedance by the resistor rd from drain to source. 2 – JFET Small-Signal Model In addition, note that the source is common to both input and output circuits. The gate and drain terminals are only in “touch” through the controlled current source gmVgs. In situations where rd is ignored (assumed sufficiently large in relation to other elements of the network to be approximated by an open circuit). The equivalent circuit is simply a current source whose magnitude is controlled by the signal Vgs and parameter gm - clearly a voltagecontrolled current source. Example 8.6 Given gfs= 3.8 mS and gos = 20 μS, sketch the FET ac equivalent model. FET ac equivalent model. 3 – Fixed-Bias Configuration The fixed-bias configuration includes the coupling capacitors C1 and C2, which isolate the dc biasing arrangement from the applied signal and load. Both capacitors have the short-circuit equivalent for the ac analysis because the reactance is sufficiently small compared to other impedance levels of the network. 1 XC 2fC 3 – Fixed-Bias Configuration Zi Zo Setting Vi = 0V as required by the definition of Zo will establish Vgs as 0V also. 3 – Fixed-Bias Configuration AV Phase Relation 180o phase shift between V0 and Vi. Example 8.7 The fixed-bias configuration of example 7.1 had an operating point defined by VGSQ = -2V and IDQ = 5.625mA, with IDSS =10mA and VP = 8V. The network is redrawn as in Figure with an applied signal Vi. The value of yos is provided as 40 μS. a. Determine gm. b. Find rd. c. Determine Zi. d. Calculate Zo. e. Determine the voltage gain Av. f. Determine Av ignoring the effect of rd. Example 8.7 4 – Self-Bias Configuration Bypassed RS The fixed-bias configuration has the distinct disadvantage of requiring two dc voltage sources. The self-bias configuration requires only one dc supply to establish the desired operating point. 4 – Self-Bias Configuration Zi Zo AV Phase Relation 180o phase shift between V0 and Vi. 4 – Self-Bias Configuration Un-bypassed RS without rd Zi Zo KVL with RG shorted-out, 4 – Self-Bias Configuration 4 – Self-Bias Configuration Zo including the effect of rd Vrd VRS Vo 0 (VRS Vgs ) 4 – Self-Bias Configuration 4 – Self-Bias Configuration 4 – Self-Bias Configuration AV Application of KVL to the input circuit results in, I D g mVgs I 4 – Self-Bias Configuration 4 – Self-Bias Configuration Phase Relation 180o phase shift between V0 and Vi. Example 8.8 The self-bias configuration of example 7.2 has an operating point defined by VGSQ = -2.6 V and IDQ = 2.6 mA, with IDSS = 8 mA and VP = -6 V. The network is redrawn as in Figure with an applied signal Vi. The value of gos is given as 20 μS. a. Determine gm. b. Find rd. c. Find Zi. d. Calculate Zo with and without the effects of rd. Compare the results. e. Calculate Av with and without the effects of rd. Compare the results. Example 8.8 Example 8.8 5 – Voltage-Divider Configuration 5 – Voltage-Divider Configuration Zi Zo AV 6 – Common-Gate Configuration 6 – Common-Gate Configuration Zi 6 – Common-Gate Configuration 6 – Common-Gate Configuration 6 – Common-Gate Configuration Zo Setting Vi = 0V, will short-out the effects of Rs and set Vgs to 0V. The result is gmVgs= 0, rd and RD will be parallel. 6 – Common-Gate Configuration AV 6 – Common-Gate Configuration Phase Relation Vi and V0 are in phase. Example 8.9 Although the network of Figure may not initially appear to be of the common-gate variety, a close examination will reveal that it has all the characteristics of CB. If VGSQ = -2.2 V and IDQ = 2.03 mA: a) Determine gm. b) Find rd. c) Calculate Zi with and without rd. Compare results. d) Find Zo with and without rd. Compare results. e) Determine Vo with and without rd. Compare results. Example 8.9 Example 8.9 Example 8.9 Example 8.9 demonstrates that even though the condition rd ≥ 10RD was not satisfied, the results for the parameters given were not significantly different using the exact and approximate equations. In fact, in most cases, the approximate equations can be used to find a reasonable idea of particular levels with a reduced amount of effort. 7 – Source-Follower (Common-Drain) Configuration 7 – Source-Follower (Common-Drain) Configuration Zi 7 – Source-Follower (Common-Drain) Configuration Zo 7 – Source-Follower (Common-Drain) Configuration 7 – Source-Follower (Common-Drain) Configuration AV Phase Relation Vi and V0 are in phase. 7 – Source-Follower (Common-Drain) Configuration Source Follower Emitter Follower Vo RE Av Vi RE re Vo Av 1 Vi R E re , RE re RE Example 8.10 A dc analysis of the source-follower network as in Figure results in VGSQ= -2.86V and IDQ= 4.56mA. a. Determine gm. b. Find rd. c. Determine Zi. d. Calculate Zo with and without the effect of rd. Compare results. e. Determine Av with and without the effects of rd. Compare results. Example 8.10 Example 8.10 8 – Depletion-Type MOSFETs Shockley’s equation is also applicable to depletion-type MOSFETs results in the same equation for gm. The ac equivalent model for D-MOSFETs is exactly same as that employed for JFETs. Only difference offered by D-MOSFETs is that VGSQ can be positive for n-channel devices and negative for p-channel units. Example 8.11 The network was analyzed as example 7.7, resulting in VGSQ= 0.35V and IDQ = 7.6mA. a. Determine gm and compare to gm0. b. Find rd. c. Sketch the equivalent network for Figure. d. Find Zi. e. Calculate Zo. f. Find Av. Example 8.11 9 – Enhancement-Type MOSFETs Enhancement-type MOSFET can be either an n-channel (nMOS) or pchannel (pMOS) devices. For E-MOSFETs, the relationship between output current and controlling voltage is defined by 9 – Enhancement-Type MOSFETs “k” can be determined from, 10 – E-MOSFET Drain-Feedback Configuration Zi KCL at node “D” 10 – E-MOSFET Drain-Feedback Configuration 10 – E-MOSFET Drain-Feedback Configuration Zo 10 – E-MOSFET Drain-Feedback Configuration AV KCL at node “D” Phase Relation Vi and V0 are out of phase by 180o. Example 8.12 The E-MOSFET of Figure was analyzed in example 7.11, with the result that k = 0.24×10-3 A/V2, VGSQ = -6.4 V and IDQ= 2.75 mA. a. Determine gm. b. Find rd. c. Determine Zi with and without rd. Compare results. d. Calculate Zo with and without rd. Compare results. e. Determine Av with and without rd. Compare results. Example 8.12 Example 8.12 11 – E-MOSFET Voltage-Divider Configuration Zi Zo AV 12 – Designing FET Amplifier Networks Design problems at this stage are limited to obtaining a desired dc bias condition or ac voltage gain. In most cases, the various equations developed are used “in reverse” to define the parameters necessary to obtain the desired gain, input impedance, or output impedance. To avoid unnecessary complexity, the approximate equations are often employed because some variation will occur when calculated resistors are replaced by standard values. Be aware that although superposition permits a separate analysis and design of the network from a dc and an ac viewpoint, a parameter chosen in the dc environment will often play an important role in the ac response. In particular, recall that the resistance RG could be replaced by a shortcircuit equivalent in the feedback configuration because IG = 0A for dc conditions, but for the ac analysis, it presents an important highimpedance path between Vo and Vi. 12 – Designing FET Amplifier Networks Example 8.13 Design the fixed-bias network of Figure to have an ac gain of 10. That is, determine the value of RD. Example 8.13 Example 8.13 Example 8.14 Choose the values of RD and RS for the network of Figure that will result in a gain of 8 using a relatively high level of gm for this device defined at VGSQ =1/4VP. Example 8.14 Example 8.14 Example 8.14 Example 8.15 Determine RD and RS for the network of Figure to establish a gain of 8 if the bypass capacitor CS is removed. Example 8.15 13 – Summary Table 13 – Summary Table 13 – Summary Table 13 – Summary Table 14 – Effect of RL and RSIG All two-port equations developed for the BJT transistor apply to FET network also because the quantities of interest are defined at the input and output terminals and not the components of the system. The greatest gain of an amplifier is the no-load gain. The loaded gain is always less than the no-load gain. A source impedance will always reduce the overall gain below the noload or loaded level. 14 – Effect of RL and RSIG Self Bias Configuration 14 – Effect of RL and RSIG 14 – Effect of RL and RSIG 14 – Effect of RL and RSIG 15 – Cascade Configuration The total gain is the product of the gain of each stage including the loading effects of the following stage. 15 – Cascade Configuration Example 8.16 Calculate the dc bias, voltage gain, input impedance, output impedance, and resulting output voltage for the cascade amplifier shown in Figure. Example 8.16 Example 8.16 Example 8.17 For the cascade amplifier of Figure, use the dc bias calculated in Examples 5.15 and 8.16 to calculate input impedance, output impedance, voltage gain, and resulting output voltage. Example 8.17 Example 8.17