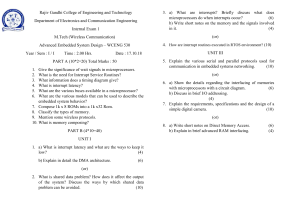

Interrupts In Micro Controller PIC 24 Family

Prepared by : EMAD MOHAMMED

Note: Most of the contents of this slides are supplied by the authors of the book:

MICROCONTROLLERS From Assembly Language to C using PIC24 Family

Lecture Objectives

Polling vs. Interrupts

How Interrupt Executed?

What we need to program interrupt?

1.Knowing the source of interrupt.

2.Interrupt priority.

3.Activate the interrupt

Explain in details a few type of interrupt.

1. External Interrupt.

2. Timer Interrupt.

Traps vs. Interrupts.

What are the sources of Interrupte?

Polled IO versus Interrupt Driven IO

Polled INPUT/OUTPUT (IO)

- processor continually checks IO device to see if it is

ready for data transfer.

It is inefficient way due to:

1. Processor wastes time checking for ready Condition.

2. Either checks too often or not often enough.

Interrupt Driven IO

– IO

device interrupts processor when it is ready for data

transfer.

It is very efficient way due to:

1. Processor can be doing other tasks while waiting for

last data transfer to complete.

Note that : All IO in modern computers is interrupt driven.

PIC24 μC Interrupt Operation

How Interrupt Executed?

Next Slide

The normal program flow (main) is referred to as the foreground code.

The Interrupt Service Routine ( _ISR) is referred to as the background

code.

Interrupt Vector Table

This table contains the starting

address of the ISR for each

interrupt source in Pic24 family.

Interrupt Sources PIC24HJ32GP202

External Interrupt

Change Notification

Timers

INT0

T1

T2

Serial Communication

T3

INT1

INT2

Fig.3

Interrupt Priorities

Interrupt Priority:

- It is an important condition one can see that it is the most important

condition during programming the interrupt, so that we have to take in account

the following notes:

1. Normal instruction execution is priority 0.

2. Assigning a priority of 0 to an interrupt masks (disables) that

interrupt

3. An interrupt MUST have a higher priority than 0 to interrupt

normal execution.

4. An interrupt can be assigned a priority from 0 to 7.

Which one will executed?

I.

II.

An interrupt with a higher priority can interrupt currently

executing ISR with a lower priority.

If simultaneous interrupts of the SAME priority occur, then

the interrupt with the LOWER VECTOR NUMBER (is first

in the interrupt vector table) has the higher natural priority.

For example, the INT0 interrupt has a higher natural priority than INT1.

Activate the Interrupt

Enabling an Interrupt.

- Each interrupt source generally has the following:

1.

2.

3.

4.

FLAG bit.

PRIORITY bits.

ENBLE bit.

Remap the pin (Some types need this).

The flag bit:

- is set by the interrupt whenever the flag condition of this interrupt is

true.

(NOTE: One of the things that must be done by the ISR is to clear the flag

bit, or else the ISR will get stuck in an infinite loop).

The priority bits:

-set the interrupt priority as we said from 0 to 7.

The enable bit:

-must be ‘1’ for the ISR to be executed.

(NOTE: The enable bit does not have to be a ‘1’ for the flag bit to be set!!!!).

By default, all priority bits and enable bits are ‘0’, so interrupt ISRs are

disabled from execution.

Remap Pins:

-Some inputs/outputs for internal modules must be mapped to RPx

pins (remappable pins) if they are to be used.

a) Mapping Input to RPx:

Fig.4

Remap Pins (Cont.):

b) Mapping Outputs to RPx:

External Interrupts (INT0, INT1, INT2 Interrupts )

These are input interrupt sources (INTx) can be any input device sensor or switch

based on your application.

What we need to configuration these interrupts?

1. The INTxEP bit: used to configure these interrupts as rising/falling-edge

triggered by put it ‘1’ for falling edge, ‘0’ for rising edge.

2. On the PIC24HJ32GP202, INT1 and INT2 must be brought out to

remappable pins (RPx);

1. INT0 is assigned a fixed pin location as shown below.

2. _INT1R=n; for INT1, ‘n’ can be value from (0:15) as shown below.

3. _INT2R=n; for INT2, ‘n’ can be value from (0:15) as shown below.

3. General bits:

1. _INTxIF ‘Flag’ we just clear it.

2. _INTxIP ‘Priority 1:7’

3. _INTxIE ‘Enable ‘1’’

Example(1):

Try to Scrolling an 8 led connected to (RB0:RB7) right or left every time you press an

external switch connected to RB8 as shown in the figure below, use external interrupt

INT1and clock Fosc=40MHZ.

RB8

#define Shift_Right 0

#define Shift_Left 1

Unit8 Leds_State;

int main(void) {

Config_Leds_Out(); // already built

_INT1R=8; // Assign INT1 to a remappable pin RP8

_INT1IF =0 ;

_INT1IP = 2; //choose a priority

_INT1IE = 1; //enable the interrupt

_INT1EP = 1; // Edge selection

while (1);

}

void _ISRFAST _INT1Interrupt (void) {

_INT1IF = 0; //clear the interrupt flag bit

Delay_ms(15);

Switch (Leds_State){

Case Shift_Right: if (portb&0x0001)

{Leds_State=Shift_Left;

LATB=LATB<<1;}

else

LATB=LATB>>1;

break;

Case Shift_Left: if (portb&0x0080)

{Leds_State=Shift_Right;

LATB=LATB>>1;}

else

LATB=LATB<<1;

break;

}

}

Hardware Timers

We have three timers T1,T2,T3 that can be used to

generate interrupt for a periodic duration.

Recall that a Timer is just a counter. Time can be

converted from elapsed Timer Ticks (Ticks) by

multiplying by the clock period (Ttmr) of the timer:

Time = Ticks x Ttmr

Ex. If a timer is a 16-bit timer, and it is clocked at the

FCY = 40 MHz, then will count from

0x0000 to 0xFFFF (65536 ticks) in:

Time = 65536 x (1/40 MHz) = 65536 x 25 ns = 1638400

ns = 1638.4 us = 1.6384 ms

Timer 2 Block Diagram

Ton un TSIDL

0

0

0

un

Tgate

000000

0

Tckps T32 un Tcs un

xx

0

0

0

0

T2CON=0x00x0

T2IF Period

After finding the value of T2CON ,as first step in configuration

timer2 as interrupt, we have to find value of PR2 ,where the T2IF

flag is set at the following period (Tt2if):

Tt2if = (PR2+1) x PRE x Tcy = (PR2+1) x PRE/Fcy

Observe that because Timer2 is a 16-bit timer, if PR2 is its

maximum value of 0xFFFF (65535), and the prescaler is ‘1’,

this is just:

Tt2if = 65536 x 1/Fcy

We typically want to solve for Tt2if, given a PRE value:

PR2 = (Tt2if x Fcy /PRE ) − 1 ‘as second step’

General bits:

1. _TxIF ‘Flag’ we just clear it.

2. _TxIP ‘Priority 1:7’

3. _TxIE ‘Enable ‘1’’

Traps vs. Interrupts

A Trap is a special type of interrupt, is non-maskable, has

two important characteristics which are:

1. Higher priority than normal interrupts.

2. Are always enabled!

What are types of trap?

Hard trap

- CPU stops after instruction at which trap occurs

Soft trap

-CPU continues executing instructions as trap is sampled

and acknowledged