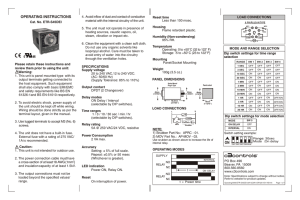

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 53, NO. 3, JUNE 2006 727 Simple Passive Lossless Snubber for High-Power Multilevel Inverters Xiangning He, Senior Member, IEEE, Alian Chen, Hongyang Wu, Yan Deng, and Rongxiang Zhao Abstract—A passive lossless snubber circuit for multilevel inverters is proposed in this paper. The topology is simple and requires no extra control circuit. In order to reduce the high-voltage stress on power switches with this snubber circuit, an improved snubber circuit is presented by adding separate low-power direct current voltage sources into the original one. The operating principles and design considerations are described in detail in this paper. A prototype of a three-phase three-level diode-clamped inverter with the improved passive lossless snubber is built and tested. The simulation and experimental results indicate that not only can it realize the soft switching operation of the three-level inverter with low-voltage stress but also the topology and the control are simple. Index Terms—Inverters, lossless circuits, multilevel systems, snubbers. I. I NTRODUCTION M ULTILEVEL inverters are suitable for high-voltage and high-power applications because they can reduce voltage stresses on power switches, harmonic content, and electromagnetic interference (EMI) noise of the output voltage. However, in order to improve the security and reliability of the system, the proper snubber circuits for power switches are also required in these applications. Furthermore, to further reduce switching losses and serious EMI, it is expected that these adopted snubber circuits can make the power switches work under soft-switching conditions. Based on these considerations, a number of soft-switching topologies [1], [2] for multilevel inverters have been proposed during the past two decades. Summarily, all of them belong to active soft-switching techniques. In the techniques, some auxiliary circuit configurations with active switching devices are added into the original main circuit, and the soft switching of main power switches can be realized by detecting and timing the control of the auxiliary circuit properly. Because the topology and control of multilevel inverters are fairly complicated, the topology and control of the soft switching circuit derived from this technique will be more complicated. However, passive soft switching techniques, i.e., passive lossless snubber techniques, show superiority over Manuscript received February 5, 2004; revised February 15, 2005. Abstract published on the Internet March 18, 2006. This work was supported by the National Nature Science Foundation of China under Grants 59947006 and 50277035. This paper was presented in part at the 2002 IEEE Applied Power Electronics Conference and Exposition, Dallas, TX, March 2002. X. He, A. Chen, Y. Deng, and R. Zhao are with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China (e-mail: hxn@zju. edu.cn; chenalian@zju.edu.cn; dengyan@zju.edu.cn; rongxiang@zju.edu.cn). H. Wu is with the Delta Power Electronics Center, Shanghai 201209, China (e-mail: ocean_w@163.com). Digital Object Identifier 10.1109/TIE.2006.874422 the active one, in which some auxiliary circuit configurations consisting of passive components, such as inductor, capacitor, diode and transformer, etc., are added into the original main circuit. Through the resonance process of these passive components, the switching processes of main power switches are improved, and soft-switching operation using them is realized. Obviously, the passive soft switching techniques require no extra active devices, detection, or special timing and control so that the reliability of the system is high and the control is simple. However, due to the difficulties and challenges of designing a passive lossless snubber for the inverter bridge leg, only several multilevel passive low-loss snubber circuits derived from that of the two-level one were proposed. Until now, no passive lossless snubber circuit for multilevel inverters is proposed. Thus, this paper focuses on the passive lossless snubber techniques for multilevel inverters and proposes a novel passive lossless snubber circuit for multilevel inverters. In addition, some new results are attained. II. D ERIVATION OF THE T HREE -L EVEL P ASSIVE L OSSLESS S NUBBER T OPOLOGY As to the existing snubber configurations for multilevel inverters, they are usually extended from the two-level passive low-loss snubber configurations. Among them, the snubber configuration of [3] is the extension and improvement of the resistor–capacitor–diode (RCD) snubber for two-level inverters. The snubber configuration of [4] is the extension and improvement of the Undeland snubber for two-level inverters, whereas the snubber configuration of [5] is the extension and improvement of the McMurry snubber for two-level inverters. All of them are lossy and do not belong to passive soft switching techniques, i.e., the passive lossless snubber techniques defined in this paper. The difficulties of designing multilevel passive lossless snubber circuits lie in that not only should the special topology of multilevel inverters be considered but also the snubber circuits should be designed as simple as possible; otherwise, the practicability of the snubber circuits would be doubtable. The passive lossless snubber circuit for multilevel inverters can be designed using the following two methods. The first method is designing the multilevel passive lowloss snubber circuit at first. In the snubber circuit, the resistors should be as few as possible. Then, these resistors are replaced by other passive components (usually capacitors) that can store snubber energy temporarily. At last, an energy recovery path, through which the energy stored in the passive components is gathered and fed back to the power source or load, is 0278-0046/$20.00 © 2006 IEEE 728 Fig. 1. Passive lossless snubber cell for two-level inverters. constructed so that the power switches of the main circuit can work under the soft switching conditions. Sung and Nam [5] made some attempts to design a multilevel passive lossless snubber circuit by using this method. The second method is constructing a multilevel passive lossless snubber cell at first. Then, apply the snubber cell properly revised into the multilevel inverters. The key of this method is the design of the snubber cell. It should have a simple structure and easy extension. As far as the two methods are concerned, it is relatively easy to design snubber circuits by using the first method. However, its idea is not flexible enough. Moreover, because its energy recovery path is usually constructed by a transformer, this will result in high-voltage stress on some devices, high losses, and magnetic resetting problems. However, the design idea of the second method is more reasonable and active. The key of this method is the design of the snubber cell, whose performance will determine whether the design is successful or not. In this paper, the second method is adopted to design the multilevel passive lossless snubber. Fig. 1 shows a passive lossless snubber configuration proposed by our laboratory for two-level inverter bridge legs [6], [7], which is one of the simplest existing passive lossless snubber topologies for two-level inverter bridge legs. The snubber cell consists of one snubber inductor Ls , one energy buffer capacitor Cb , one snubber capacitor Cs , one energy recovery path that consists of Dr and Lr , and two diodes Ds1 and Ds2 , which limit the direction of the current. This snubber cell is derived from the graph theory in [6], [7], so that it has the properties of simple structure and easy extension. In the following paragraph, the possibility of extending the snubber cell from a two-level inverter to a three-level inverter is discussed. One bridge leg of the diode-clamped three-level inverter is shown in Fig. 2. It is obvious that its structure is similar to that of a two-level inverter. Because of its working characteristics, the bridge leg of a three-level inverter can only work under three switching-state combinations, namely: 1) state a: S1 and S2 switched on, S3 and S4 switched off; 2) state b: S2 and S3 switched on, S1 and S4 switched off; and 3) state c: S3 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 53, NO. 3, JUNE 2006 Fig. 2. Topology of three-level inverters. Fig. 3. Passive lossless snubber cell for three-level inverters. and S4 switched on, S1 and S2 switched off. Unlike in the two-level inverter, during the commutation process from state a (state c) to state b (state b) in the three-level inverter, there is no commutation between S1 (S4 ) and D3 (D2 ) but the commutation between S1 (S4 ) and clamp diodes Dc1 (Dc2 ). According to the preceding analysis, there are three key points when the snubber cell shown in Fig. 1 is used in three-level inverters. 1) The basic principle of designing passive lossless snubber is unchangeable, i.e., the snubber inductor should be in series with the main power switches and the snubber capacitor should be in parallel with the main power switches. 2) There are two pairs of switches working complementarily in one three-level inverter HE et al.: SIMPLE PASSIVE LOSSLESS SNUBBER FOR HIGH-POWER MULTILEVEL INVERTERS Fig. 4. Commutation processes between state a and state b. (a) Stage 1. (b) Stage 2. (c) Stage 3. (d) Stage 4. (e) Stage 5. (f) Stage 6. (g) Stage 7. 729 730 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 53, NO. 3, JUNE 2006 Fig. 5. Commutation waveforms of S1 . bridge leg (S1 and S3 , and S2 and S4 ), so two snubber cells are needed. 3) Due to the change of the commutation object, the connection point of energy recovery path should be adjusted. Based on these principles, the passive lossless snubber for a three-level inverter bridge leg is attained and shown in Fig. 3. III. O PERATION P RINCIPLE AND M ATHEMATICAL A NALYSIS A. Operation Principle In the following analysis, several assumptions are employed. 1) Ideal power switches, diodes, inductors, and capacitors are used. 2) The current of the load is constant during commutation (the time constant of the load is far larger than the switching transient time of the power switches). 3) The dead time in the control signals for the switching pairs in the same leg is ignored. 4) Cb is large enough to keep the voltage stable within one period; thus, it can be considered as a voltage source E in analysis. 5) Ls is equal to Lr in inductance for analysis simplification. The commutation process is analyzed by taking the commutation process between state a and state b as an example here. Assume S1 and Dc1 carry the load current in the stable state a and state b, respectively. S1 and S2 forward carrying the load current is set as the initial state of analysis, and the initial voltage of Cs1 is −E. The operating stages within a switching period can be attained and shown in Fig. 4. The corresponding commutation waveforms are shown in Fig. 5. Stage 1—t < t0 : iLs1 = Iload , uCs1 = −E. It is the stable state a that S1 and S2 carry load current. Fig. 6. Simulated waveforms of the passive lossless snubber. (a) Turn-off waveforms of S1 . (b) Turn-on waveforms of S1 . Stage 2—t0 < t < t1 : S1 turns off as soon as S3 turns on at t0 . The current formerly carried by S1 is shunted by the capacitor path consisting of Cb1 , DS11 , CS1 , and S1 is zero-voltage switched off. S3 is zero-current switched on because of the existence of LS1 and Lr1 . Ud , E, LS1 , CS1 , and Lr1 take part in resonance until the voltage across Cs1 reaches Ud iLs1 = uCs1 = r1 +E Ud LLS1 ω1 (Lr1 + LS1 ) sin ω1 (t − t0 ) + Lr1 Iload cos ω1 (t − t0 ) LS1 + Lr1 + LS1 Ud − E (t − t0 ) + Iload LS1 + Lr1 LS1 + Lr1 (1) (Ud − E)Lr1 [1 − cos ω1 (t − t0 )] LS1 + Lr1 + Iload Z1 sin ω1 (t − t0 ) − E cos ω1 (t − t0 ). (2) HE et al.: SIMPLE PASSIVE LOSSLESS SNUBBER FOR HIGH-POWER MULTILEVEL INVERTERS Fig. 7. 731 Topology of the improved three-level passive lossless snubber. The duration of this stage is determined by (2) and can be expressed by the following equation: t1 − t 0 < π − arccos Ud LS1 +ELr1 Ud Lr1 +ELS1 ωr < π . ωr (3) Here, set Fig. 8. Simulated waveforms of the improved passive lossless snubber. (a) Turn-off waveforms of S1 . (b) Turn-on waveforms of S1 . L1 = Lr1 Ls1 Ls1 + Lr1 (4) The stage ends after the current of Ls1 comes back to zero and then the corresponding resonance frequency can be expressed as 1 ω1 = √ . CS1 L1 (6) During this stage, the voltage across S1 is Ud + E constantly, and the load is freewheeled by Dc1 as iDc1 = Iload . ILs1(t2) LS1 . E (8) (5) Stage 3—t1 < t < t2 : After the voltage across Cs1 is charged to Ud , the current of Ls1 flows through the path consisting of Cb1 , Ds11 , and Ds12 , and through the path, the energy is transferred into Cb1 E diLs1 =− . dt LS1 t2 − t 1 = (7) Stage 4—t2 < t < t3 : The transient process completes after the current of Ls1 comes back to zero. Then, another steady stage of Dc1 carrying the load current starts, in which the voltage across S1 is Ud . Stage 5—t3 < t < t4 : When S1 turns on and S3 turns off at the same time at t3 , the circuit enters another transient commutation process. Ls1 and Lr1 undertake voltage Ud and E, respectively, so that the current of S1 increases linearly and the current of Dc1 decreases linearly accordingly, which ensures the soft turn-on of S1 and reduces di/dt in Dc1 turn-off. During this stage iLs1 = Ud (t − t3 ). LS1 (9) 732 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 53, NO. 3, JUNE 2006 Fig. 9. Topology of three-phase three-level inverter with the improved passive lossless snubber. This stage ends when the current of Dc1 is equal to zero. The initial currents of Ls1 and Lr1 for the next stage are Iload 1 + LLr1s1UEd (10) Iload = . 1 + LLr1s1UEd (11) ILs1(t4) = ILr1(t4) Stage 6—t4 < t < t5 : S3 begins to stand the voltage from t4 . Ls1 , Cs1 , Lr1 , Ud , and Cb1 resonate Ud − E Ud − E uCs1 = Ls1 + Lr1 + E cos ω1 (t − t4 ). Ls1 + Lr1 Ls1 +Lr1 (12) This stage ends when the voltage across Cs1 is equal to −E t5 − t4 = π/ω1. (13) Stage 7—t5 < t < t6 : The two inductors of Ls1 and Lr1 share the load current and have the same voltages of 1/2(Ud − E). The two currents go to the steady state (iLs1 = Iload , iLr1 = 0) with the same absolute value of di/dt. The duration of the stage is t6 − t5 = Iload LS1 + Lr1 . 2 Ud − E (14) From the circuit configuration, it is known that E < Ud in steady state and the current in Ls1 is larger than the current in Lr1 in the end of the last stage, i.e., iLr1 (t5 ) < 0.5Iload , so (14) gives the maximum duration of this stage. When iLr1 decreases to zero, this stage ends, and the circuit goes back to stage 1 and waits for the next switching period. There are four kinds of commutation processes when the three-level inverter bridge leg with inductive loads operates under the space-vector pulsewidth-modulation (SVPWM) control method. In addition, there are three other commutation processes of S2 and D4 , S3 and D1 , and S4 and Dc2 . They can be analyzed easily according to the similar method. B. Parameter Design and Discussion Because inductors of Ls1 and Lr1 have effects on the turn-on process of power switches simultaneously, i.e., in the turn-on process of switches, the two inductors operate in parallel. So in order to make best use of the inductors, their values should be equal. The value of Cb1 (Cb2 ) should be far greater than that of Cs1 (Cs2 ) so that their voltages are invariable during the commutation process. Additional electric stresses, load dependence, and duty cycle losses are the most concerned factors to snubber performance. Just as mentioned, the analytical solutions of those equations do not exist. So numerical analysis is an effective way by using simulation tools. Here, the conditions Ud = 300 V, Iload = 15 A, fs = 3 kHz, Ls1 (Ls2 ) = Lr1 (Lr2 ) = 15 µH, Cb1 (Cb2 ) = 1 µF, and Cs1 (Cs2 ) = 37 nF are set as the simulation basic analysis point, and PSPICE 8.0 is used. By changing the parameters of the components around the basic point, the following conclusions can be obtained. 1) E decreases with an increase of Iload . 2) E is not sensitive to a change of Ls . 3) E is not sensitive to a change of Cs . 4) Duty cycle losses increase with an increase of Iload . 5) Duty cycle losses increase with an increase of Ls . 6) Duty cycle losses increase with an increase of Cs . Finally, the simulation circuit parameters are Ud = 300 V, Iload = 15 A, fs = 3 kHz, Ls1 (Ls2 ) = Lr1 (Lr2 ) = 20 µH, Cb1 (Cb2 ) = 1.5 µF, Cs1 (Cs2 ) = 33 nF. The turn-off/turn-on voltage/current waveforms of S1 are shown in Fig. 6. It is obvious from the simulation results that both the turn-on and turn-off of S1 are realized soft switching. The design rules of snubber inductor Ls and snubber capacitor Cs are based on the conventional method used in [6], [7]. The equations of stage 6 determine the current stress of Ls1 (Ls2 ), Lr1 (Lr2 ) and S1 and also provide the reference for their parameter design. Similarly, HE et al.: SIMPLE PASSIVE LOSSLESS SNUBBER FOR HIGH-POWER MULTILEVEL INVERTERS 733 the duty cycle losses, which are caused by the resonance, can be obtained by synthesizing (3), (8), (13), and (14). This gives the universal tolerance that may be employed in engineering design. Theoretically, no-load dependence exists in the proposed soft switching realization. In practice, setting of a dead time may interfere with the three-level SPWM commutation process at light load. Properly increasing the value of Ls1 will reduce the effect of dead time. IV. I MPROVEMENT OF T HREE -L EVEL P ASSIVE L OSSLESS S NUBBER C IRCUIT Just as the simulation results shown in Fig. 6, the voltage stress across S1 is about 1.8Ud . This is not reasonable for multilevel inverters because the object of adopting multilevel inverter topologies is to reduce the voltage stresses of main power switches in high-voltage applications. For this reason, an improved snubber is proposed as shown in Fig. 7. Two low-power auxiliary dc sources are added into the original snubber. The improvement can be explained as follows: The turn-off voltage stress of main switches equals to the sum of Ud and E so in order to reduce the voltage stress of main switches, the only method is to reduce E. To reduce E, two separated low-power dc sources Vdc1 and Vdc2 are added into the original snubber circuit. Using the commutation process aforementioned as an example, the additional Vdc1 changes the equations of resonance process of stages 2, 5, 6, and 7, such that (2) will be (other equations will change analogously) uCs1 = (Ud − E)Lr1 + Ls1 Vdc1 [1 − cos ω1 (t − t0 )] LS1 + Lr1 + Iload Z1 sin ω1 (t − t0 ) − E cos ω1 (t − t0 ). (15) The reason that the additional dc sources can reduce E and further reduce turn-off voltage stress on main switches can be given by the intuitionistic explanation from its physical meaning. In stages 2, 5, 6, and 7, the external excitation source in the resonant path consisting of Ls1 , Cb1 , Dr1 , and Lr1 changes from Ud to Ud − Vdc1 , which results in the reduction of E. Due to the same reason, it is difficult to gain the analytical solution. Fig. 8 gives the simulated turn-on and turn-off voltage/current waveforms of S1 with the improved snubber, where simulation parameters are the same as that in Fig. 6. Obviously, not only can the soft switching of S1 be realized through the improved snubber but also the overvoltage stress is reduced greatly and limited within the reasonable range of engineering design. The simulation results confirm the correctness of the aforementioned theory analysis. It should be pointed out that the energy of the additional dc sources can only be transferred in one direction due to the existence of Dr1 and Dr2 . Moreover, the current passing through the additional dc sources is about equal to the current of Lr1 (Lr2 ) in the case without additional dc sources, which is quite small. Thus, theoretically, there is no loss in the improved snubber. In practice, the low-power dc sources can be constructed by a circuit consisting of a lowpower 50-Hz transformer, a rectifier, and a filter. Because there Fig. 10. Experimental waveforms of the passive lossless snubber. (a) Turn-off waveforms of S1 . (b) Turn-on waveforms of S1 . are no lossy components in this circuit, the energy passing through the dc sources recovers to the power source or loads at last. The simulation and experimental results indicate that its effect on efficiency can be ignored. Certainly, the additional dc sources will bring some disadvantages in cost, volume, and weight. Compared with the advantage of reducing the overvoltages, the disadvantages are not obvious because of their low power. The proposed three-level passive lossless snubber cell can be extended to three-phase systems and more voltage-level topologies. In these applications, the circuit can be simplified because some of the snubber components can be shared by different bridge legs. Fig. 9 shows a three-phase three-level topology with the proposed passive lossless snubber. 734 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 53, NO. 3, JUNE 2006 Fig. 12. Efficiency curves of three-level hard/soft switching. The efficiency curves of the three-phase three-level inverter without the snubber and with the proposed improved snubber are shown in Fig. 12 (under the same experimental conditions). VI. C ONCLUSION Fig. 11. Experimental waveforms of the improved passive lossless snubber. (a) Turn-off waveforms of S1 . (b) Turn-on waveforms of S1 . This paper has focused on the passive soft switching techniques for multilevel inverters and presents a novel multilevel passive lossless snubber cell. To reduce the high overvoltage stress on power switches resulting from the snubber, an improved snubber cell with low overvoltage stress, which is formed by adding two low-power separate dc sources into the original one, is proposed. Theoretically, the proposed snubber cell can be used in three-phase systems or more voltage-level topologies. A prototype of a three-phase three-level diodeclamped inverter with the proposed improved snubber is built. The simulation and experimental results indicate that not only can the soft switching of power switches with low overvoltage stress be realized by using the proposed snubber but also the topology and the control are simple. R EFERENCES V. E XPERIMENTAL R ESULTS In order to verify the correctness of the aforementioned analysis and simulation results, a prototype of the diodeclamped three-phase three-level inverter with the proposed passive lossless snubber is built. The experimental parameters are UE = 2Ud = 400 V, fs = 3 kHz, Ls1 (Ls2 ) = Lr1 (Lr2 ) = 18 µH, Cb1 (Cb2 ) = 1.5 µF, and Cs1 (Cs2 ) = 33 nF. Fig. 10 shows the turn-on and turn-off experimental waveforms of S1 with the original snubber. Fig. 11 shows the turn-on and turn-off experimental waveforms of S1 with the improved snubber. It is evident that the waveforms are identical with the simulation waveforms of Figs. 6 and 8, respectively. The overvoltages in the original circuit are greatly reduced in the improved circuit, which confirms the theoretical analysis again. [1] X. Yuan, H. Stemmler, and I. Barbi, “Evaluation of soft switching techniques for the neutral-point-clamped (NPC) inverter,” in Proc. IEEE PESC, 1999, pp. 659–664. [2] J. Chang, J. Hu, and F. Z. Peng, “Modular, pinched DC-Link and soft commutated three-level inverter,” in Proc. IEEE PESC, 1999, pp. 1065– 1070. [3] B. S. Suh, D. S. Hyun, and H. K. Choi, “A circuit design for clamping an over-voltage,” in Proc. Int. Conf. Ind. Electron., Control Instrum., 1994, pp. 651–656. [4] I.-D. Kim, E. C. Nho, and B. K. Bose, “A new snubber circuit for multilevel inverter and converter,” in Proc. IEEE IAS Annu. Meeting, 1999, pp. 1432–1439. [5] J. H. Sung and K. Nam, “A simple snubber configuration for three-level GTO inverters,” IEEE Trans. Power Electron., vol. 14, no. 2, pp. 246–257, Mar. 1999. [6] Y. Deng, H. Y. Ye, and X. N. He, “Unified passive circuit for snubber energy recovery in UPS inverters,” in Proc. IEEE Telecommun. Energy Conf., 2000, pp. 119–124. [7] X. N. He and Y. Deng, “A passive lossless snubber circuit for inverters,” China Patent ZL99213490.0, Oct. 1999. HE et al.: SIMPLE PASSIVE LOSSLESS SNUBBER FOR HIGH-POWER MULTILEVEL INVERTERS 735 Xiangning He (M’95–SM’96) received the B.Sc. and M.Sc. degrees in electrical engineering from Nanjing University of Aeronautical and Astronautical, Nanjing, China, in 1982 and 1985, respectively, and the Ph.D. degree in power electronics from Zhejiang University, Hangzhou, China, in 1989. From 1985 to 1986, he was an Assistant Engineer at the 608 Institute of Aeronautical Industrial General Company, China. From 1989 to 1991, he was a Lecturer at Zhejiang University. In 1991, he obtained a Fellowship from the Royal Society of U.K., and conducted research in the Department of Computing and Electrical Engineering, Heriot-Watt University, Edinburgh, U.K., as a Postdoctoral Research Fellow for two years. He joined Zhejiang University as an Associate Professor in 1994 and has been a Full Professor in the Department of Electrical Engineering since 1996. He is also the Director of the Power Electronics Research Institute, Zhejiang University. His research interests are power electronics and their industrial applications. Dr. He received the 1989 Excellent Ph.D. Graduate Award, the 1995 Elite Prize Excellence Award, and the 1996 Outstanding Young Staff Member Award from Zhejiang University for his teaching and research contributions. He received three Scientific and Technological Progress Awards (two in 1998 and one in 2002) from the Zhejiang Provincial Government and the State Educational Ministry of China, respectively, and four Excellent Paper Awards. He is a Fellow of the Institution of Electrical Engineers, U.K. Hongyang Wu was born in Anhui Province, China, in 1971. He received the B.Sc. degree from Anhui Mechanical and Electrical College, Wuhu, China, in 1993, and the M.Sc. degree from Hefei University of Technology, Hefei, China, in 1998, both in electrical engineering, and the Ph.D. degree in power electronics from Zhejiang University, Hangzhou, China, in 2002. From 1993 to 1995, he was an Assistant Engineer with Anhui Iron and Steel Corporation. He is currently a Senior Engineer with the Delta Power Electronics Center, Shanghai, China. His research interests include topology, control, and soft-switching techniques of high-power converters. Alian Chen was born in Shandong Province, China, in 1976. She received the B.Sc. degree in applied electronics and the M.Sc. degree in power electronics from Shandong University, Jinan, China, in 1998, and 2000, respectively. She is currently working toward the Ph.D. degree in power electronics at Zhejiang University, Hangzhou, China. Her research interests are power electronics and their industrial applications. Rongxiang Zhao received the M.Sc. and Ph.D. degrees in electrical machines and control from Zhejiang University, Hangzhou, China, in 1987 and 1991, respectively. He is currently a Professor in the Department of Electrical Engineering, Zhejiang University. He is also the Director of the National Engineering Research Center for Applied Power Electronics at Zhejiang University. His research interests are power converters, induction heating, and motor drives. Yan Deng was born in Sichuan, China, in 1973. He received the B.E.E. degree from the Department of Electrical Engineering, Zhejiang University, Hangzhou, China, in 1994, and the Ph.D. degree in power electronics and electric drives from the College of Electrical Engineering, Zhejiang University, in 2000. Since 2000, he has been a Faculty Member at Zhejiang University, where he is currently an Associate Professor, teaching and conducting research on power electronics. He is the author of more than 20 papers published in international and domestic conference proceedings/transactions. His research interests are topologies and control for switchmode power conversion.