DG526, DG527 DG528, DG529

advertisement

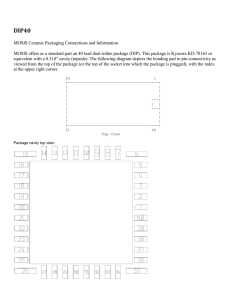

DG526, DG527 DG528, DG529 S E M I C O N D U C T O R Analog CMOS Latchable Multiplexers December 1993 Features Description • Direct RESET The DG526, DG527, DG528, and DG529 are CMOS monolithic 16 channel/dual 4 channel analog multiplexers. Each device has on-chip address and control latches to simplify design in microprocessor based applications. The DG526 uses 4 address lines to control its 16 channels; the DG527, DG528 both use 3 address lines to control their 8 channels; and the DG529 uses 2 address lines to control its 4 channels. The enable pin is used to enable the address latches during the WR pulse. It can be hard wired to the logic supply if one of the channels will always be used (except during a reset) or it can be tied to address decoding circuitry for memory mapped operation. The RS pin is used to clear all latches regardless of the state of any other latch or control line. The WR pin is used to transfer the state of the address control lines to their latches, except during a reset or when EN is low. • TTL and CMOS Compatible Address and Enable Inputs • 44V Maximum Power Supply Rating • Break-Before-Make Switching • Alternate Source Applications • Data Acquisition Systems • Communication Systems • Automatic Test Equipment A channel in the ON state conducts signals equally well in both directions. In the OFF state each channel blocks voltages up to the supply rails. The address inputs, WR, RS and the enable input are TTL and CMOS compatible over the full specified operation temperature range. • Microprocessor Controlled System Ordering Information PART NUMBER TEMPERATURE PART NUMBER PACKAGE TEMPERATURE PACKAGE DG526AK -55oC to +125oC 28 Lead Ceramic DIP DG528AK -55oC to +125oC 18 Lead Ceramic DIP DG526AK/883B -55oC to +125oC 28 Lead Ceramic DIP DG528AK/883B -55oC to +125oC 18 Lead Ceramic DIP DG526BK o o o o -25 C to +85 C DG526BY -25 C to +85 C DG526CJ DG526CK DG526CY 28 Lead Ceramic DIP DG528BK o o 18 Lead Ceramic DIP o o 18 Lead Plastic SOIC -25 C to +85 C 28 Lead Plastic SOIC DG528BY -25 C to +85 C 0oC to +70oC 28 Lead Plastic DIP DG528CJ 0oC to +70oC 18 Lead Plastic DIP 0oC to +70oC 28 Lead Ceramic DIP DG528CK 0oC to +70oC 18 Lead Ceramic DIP o o 0 C to +70 C o o 28 Lead Plastic SOIC DG528CY o o 0 C to +70 C o o 18 Lead Plastic SOIC DG527AK -55 C to +125 C 28 Lead Ceramic DIP DG529AK -55 C to +125 C 18 Lead Ceramic DIP DG527AK/883B -55oC to +125oC 28 Lead Ceramic DIP DG529AK/883B -55oC to +125oC 18 Lead Ceramic DIP DG527BK -25oC to +85oC 28 Lead Ceramic DIP DG529BK -25oC to +85oC 18 Lead Ceramic DIP DG527BY o o -25 C to +85 C o o 28 Lead Plastic SOIC DG529BY o o -25 C to +85 C o o 18 Lead Plastic SOIC DG527CJ 0 C to +70 C 28 Lead Plastic DIP DG529CJ 0 C to +70 C 18 Lead Plastic DIP DG527CK 0oC to +70oC 28 Lead Ceramic DIP DG529CK 0oC to +70oC 18 Lead Ceramic DIP DG527CY 0oC to +70oC 28 Lead Plastic SOIC DG529CY 0oC to +70oC 18 Lead Plastic SOIC CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper I.C. Handling Procedures. Copyright © Harris Corporation 1993 10-54 File Number 3139 DG526, DG527, DG528, DG529 Pinouts DG526 (PDIP, SOIC) TOP VIEW DG527 (PDIP, SOIC) TOP VIEW V+ 1 28 D V+ 1 28 DB NC 2 27 V- DB 2 27 V- RS 3 26 S8 RS 3 26 S8A S16 4 25 S7 S8B 4 25 S7A S15 5 24 S6 S7B 5 24 S6A S14 6 23 S5 S6B 6 23 S5A S13 7 22 S4 S5B 7 22 S4A S12 8 21 S3 S4B 8 21 S3A S11 9 20 S2 S3B 9 20 S2A S10 10 19 S1 S2B 10 19 S1A S9 11 18 EN S1B 11 18 EN GND 12 17 A0 GND 12 17 A0 WR 13 16 A1 WR 13 16 A1 A3 14 15 A2 NC 14 15 A2 DG528 (PDIP, SOIC) TOP VIEW DG529 (PDIP, SOIC) TOP VIEW WR 1 18 RS A0 2 EN 3 V- 4 WR 1 18 RS 17 A1 A0 2 17 A1 16 A2 EN 3 16 GND V- 4 15 GND 15 V+ 14 V+ S1A 5 14 S1B S2 6 13 S5 S2A 6 13 S2B S3 7 12 S6 S3A 7 12 S3B S4 8 11 S7 S4A 8 11 S4B D 9 10 S8 DA 9 10 DB S1 5 10-55 DG526, DG527, DG528, DG529 Functional Diagrams DG526 16 CHANNEL SINGLE ENDED MULTIPLEXER V+ V- DG527 DIFFERENTIAL 8 CHANNEL MULTIPLEXER GND V+ S1 S1A S2 S2A S3 S3A S4 S4A S5 S5A S6 S6A S7 S7A S8 V- GND DA S8A S9 D S1B S10 S2B S11 S3B S12 S4B S13 S5B S14 S6B S15 S7B S16 S8B DB RS WR DECODER LOGIC AND LATCHES A3 A2 A1 A0 RS WR EN A2 DG528 8 CHANNEL SINGLE ENDED MULTIPLEXER V+ V- DECODER LOGIC AND LATCHES A1 A0 DG529 DUAL 4 CHANNEL MULTIPLEXER GND V+ S1 S1A S2 S2A S3 S3A S4 D V- GND DA S4A S5 S1B S6 S2B S7 S3B S8 S4B DECODER LOGIC AND LATCHES DB DECODER LOGIC AND LATCHES DECODER LOGIC LATCHES LATCHES RS WR RS WR A2 A1 EN A0 EN A0 10-56 A0 EN DG526, DG527, DG528, DG529 Schematic Diagrams LOGIC INTERFACE AND LEVEL SHIFTER V+ + LOGIC TRIP POINT REF - TO DECODER GND AX, EN, RS, WR V- DECODER AND SWITCH V+ SX AX‘ EN‘ RS‘ V+ DECODER WR‘ DX V- 10-57 Specifications DG526, DG527, DG528, DG529 Absolute Maximum Ratings Thermal Information V+ to V-. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +44V V- to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-25V VIN to Ground (Note 1) . . . . . . . . . . . . . . . . . . . . (V- - 2V), (V+ + 2V) VS or VD to V+ (Note 1) . . . . . . . . . . . . . . . . . . . . . . . .+2V, (V- - 2V) VS or VD to V- (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . -2V, (V+ + 2V) Current, Any Terminal Except S or D . . . . . . . . . . . . . . . . . . . . 30mA Continuous Current, S or D . . . . . . . . . . . . . . . . . . . . . . . . . . . 20mA Peak Current, S or D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40mA (Pulsed at 1ms, 10% Duty Cycle Max) Storage Temperature Range C Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -65oC to +125oC A and B Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . -65oC to +150oC Lead Temperature (Soldering 10s) . . . . . . . . . . . . . . . . . . . . +300oC Thermal Resistance θJA θJC 18 Lead Plastic DIP Package . . . . . . . . . 90oC/W 18 Lead Ceramic DIP Package . . . . . . . . 75oC/W 22oC/W 18 Lead SOIC Package. . . . . . . . . . . . . . 95oC/W 28 Lead Plastic DIP Package . . . . . . . . . 60oC/W 28 Lead Ceramic DIP Package . . . . . . . . 55oC/W 17oC/W 28 Lead SOIC Package. . . . . . . . . . . . . . 70oC/W Operating Temperature C Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to +70oC B Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -25oC to +85oC A Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to +125oC Junction Temperature Ceramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC Plastic Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +150oC CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Electrical Specifications (Note 3) V+ = +15V, V- = -15V, GND = 0V, WR = 0V, RS = 2.4V, EN = 2.4V, TA = +25oC, Unless Otherwise Specified A SUFFIX (NOTE 6) TEST CONDITIONS PARAMETER B AND C SUFFIX MIN (NOTE 2) TYP MAX MIN (NOTE 2) TYP MAX UNITS DYNAMIC Switching Time DG526, of Multiplexer, DG527 tTRANSITION DG528, DG529 See Figure 3 (Note 7) - 0.65 1 - 0.65 - µs See Figure 3 - 0.6 1 - 0.6 - µs Break-BeforeMake Interval, tOPEN DG526, DG527 See Figure 4 - 0.2 - - 0.2 - µs - 0.2 - - 0.2 - µs Enable and Write Turn-ON Time, tON (EN, WR) DG526, DG527 See Figures 1, 6 (Note 7) - 0.7 1.5 - 0.7 - µs DG528, DG529 See Figures 5, 6 (Note 7) - 1 1.5 - 1 - µs Enable and DG526, Reset Turn DG527 OFF Time, tOFF DG528, (EN, RS) DG529 See Figures 2, 7 (Note 7) - 0.4 1 - 0.4 - µs See Figures 5, 6 (Note 7) - 0.4 1 - 0.4 - µs Off Isolation, OIRR VEN = 0V, R = 1kΩ, CL = 15pF, VS = 7VRMS, f = 500kHz (Note 4) - 55 - - 55 - dB - 68 - - 68 - dB - 6 - - 6 - pF - 2.5 - - 2.5 - pF - 10 - - 10 - pF - 5 - - 5 - pF DG528, DG529 DG526, DG527 DG528, DG529 Logic Input Capacitance, CIN DG526, DG527 Source OFF Capacitance, CS(OFF) DG526, DG527 f = 1MHz DG528, DG529 DG528, DG529 VS = 0V VEN = 0V, f = 140kHz 10-58 Specifications DG526, DG527, DG528, DG529 Electrical Specifications (Note 3) V+ = +15V, V- = -15V, GND = 0V, WR = 0V, RS = 2.4V, EN = 2.4V, TA = +25oC, Unless Otherwise Specified (Continued) A SUFFIX (NOTE 6) TEST CONDITIONS MIN (NOTE 2) TYP MAX MIN (NOTE 2) TYP MAX UNITS - 65 - - 65 - pF - 35 - - 35 - pF DG528 - 25 - - 25 - pF DG529 - 12 - - 12 - pF - 6 - - 6 - pC - 4 - - 4 - pC PARAMETER Drain OFF Capacitance, CD(OFF)T Charge Injection, Q B AND C SUFFIX DG526 VD = 0V DG527 DG526, DG527 VEN = 0V, f = 140kHz See Figure 8 DG528, DG529 INPUT Address Input Current, Input Voltage High, IAH DG526, DG527 VA = 2.4V -10 0.02 - -10 0.02 - µA VA = 15V - 0.02 10 - 0.02 10 µA DG528, DG529 VA = 2.4V -10 -0.002 - -10 -0.002 - µA Address Input Current, Input Voltage Low, IAL DG526 DG527 VEN = 2.4V - 0.006 10 - 0.006 10 µA -10 0.01 - -10 0.01 - µA -10 0.01 - -10 0.01 - µA VEN = 2.4V -10 -0.002 - -10 -0.002 - µA VEN = 0V -10 -0.002 - -10 -0.002 - µA Analog Signal Range, VANA:LOG (Note 7) -15 - +15 -15 - +15 V Drain Source ON Resistance, RDS(ON) VD = ± 10V, VAL = 0.8V, VAH = 2.4V, IL = -200µA Sequence Each Switch ON - 270 400 - 270 450 Ω Greatest Change in Drain -10V ≤ VS ≤ 10V Source ON Resistance - RDS(ON)MIN R ∆RDS(ON) = DS(ON)MAX Between Channels, RDS(ON)AVG. ∆RDS(ON) - 6 - - 6 - % VS = ±10V, VD = 10V -1 0.02 1 - 0.02 - nA VS = ±10V, VD = 10V -1 -0.005 1 -5 -0.005 5 nA VS = ±10V, VD = 10V -10 0.2 10 - 0.2 - nA DG527 VS = ±10V, VD = 10V -5 0.2 5 - 0.2 - nA DG528 VS = ±10V, VD = 10V -10 -0.015 10 -20 0.015 20 nA DG529 VS = ±10V, VD = 10V -10 -0.008 10 -20 0.008 20 nA VD = VS(ALL) = ±10V -10 0.2 10 - 0.2 - nA VD = VS(ALL) = ±10V -5 0.2 5 - 0.2 - nA DG528 DG529 VA = 15V VEN = 0V All VA = 0V, RS = 0V, WR = 0V SWITCH VEN = 0V Drain OFF Leakage Current, ID(OFF) VEN = 0V ± ± DG526 ± Source OFF DG526, Leakage DG527 Current, IS(OFF) DG528, DG529 ± ± ± Drain ON Leakage Current, ID(ON) DG526 DG527 Sequence Each Switch On VAL = 0.8V and VAH = 2.4V (Note 5) 10-59 Specifications DG526, DG527, DG528, DG529 Electrical Specifications (Note 3) V+ = +15V, V- = -15V, GND = 0V, WR = 0V, RS = 2.4V, EN = 2.4V, TA = +25oC, Unless Otherwise Specified (Continued) A SUFFIX (NOTE 6) TEST CONDITIONS PARAMETER Drain ON Leakage Current, ID(ON) (Continued) DG528 DG529 B AND C SUFFIX MIN (NOTE 2) TYP MAX MIN (NOTE 2) TYP MAX UNITS Sequence Each Switch On VAL = 0.8V and VAH = 2.4V (Note 5) VD = VS(ALL) = ±10V -10 -0.03 10 -20 -0.03 20 nA VD = VS(ALL) = ±10V -10 -0.015 10 -20 -0.015 20 nA VEN = 0V All VA = 0V - 2.0 3.0 - 2.0 - mA - - 2.5 - - -2.5 mA -2.0 -1.2 - - -1.2 - mA -1.5 - - -1.5 - - mA SUPPLY Positive Supply Current, I+ DG526, DG527 Positive Supply Current, I- DG526, DG527 DG528, DG529 VEN = 0V All VA = 0V DG528, DG529 Electrical Specifications TA = Over Operating Temperature Range, V+ = +15V, V- = -15V, GND = 0V, WR = 0V, RS = 2.4V, EN = 2.4V Unless Otherwise Specified A SUFFIX (NOTE 6) TEST CONDITIONS PARAMETER B AND C SUFFIX MIN (NOTE 2) TYP MAX MIN (NOTE 2) TYP MAX UNITS -30 - - -30 - - µA INPUT Address Input Current Input Voltage High, IAH VA = 2.4V Address Input Current, Input Voltage Low, IAL VA = 2.4V - - 30 - - 30 µA -10 - - - - - µA -10 - - - - - µA -30 - - -30 - - µA VA = 0V -30 - - -30 - - µA Analog Signal Range, VANALOG Note 7 -15 - +15 - - - % Drain Source ON Resistance, RDS(ON) VD = ±10V, VAL = 0.8V, VAH = 2.4V, IS = -200µA, Sequence Each Switch ON - - 500 - - 500 Ω Source Off Leakage Current, IS(OFF) VEN = 0V VS = ±10V, VD = 10V -50 - 50 - - - nA Drain OFF Leakage Current, ID(OFF) VEN = 0V VS = ±10V, VD = 10V -300 - 300 -300 - 300 nA ± -200 - 200 -200 - 200 nA VS = 1 0V, VD = ±10V ± -200 - 200 -200 - 200 nA -100 - 100 -100 - 100 nA VD = VS(ALL) = ±10V -300 - 300 -300 - 300 nA -200 - 200 -200 - 200 nA -200 - 200 -200 - 200 nA -100 - 100 -100 - 100 nA DG526, DG527 DG528, DG529 VA = 15V VA = 0V VA(ALL) = 0V, RS = 0V, WR = 0V SWITCH DG528 DG529 Drain ON Leakage Current, ID(ON) DG526 DG527 DG528 DG529 Sequence Each Switch On, VAL = 0.8V, VAH = 2.4V (Note 5) ± DG526 DG527 10-60 Specifications DG526, DG527, DG528, DG529 Minimum Input Timing Requirements Over Full Temperature Range PARAMETER MEASURED TERMINAL MIN UNITS WRITE Pulse Width, tWW WR, See Figure 1 300 ns A, EN Data Valid After WRITE (Stabilization Time), tDW A0, A1, (A2), EN, WR; See Figure 1 180 ns A, EN Data Valid After WRITE (Hold Time), tWD A0, A1, (A2), EN, WR; See Figure 1 30 ns RESET Pulse Width, tRS RS, (Note 6), VS = 5V, See Figure 2 500 ns NOTES: 1. Signals on VS, VD or VIN exceeding V+ or V- will be clamped by internal diodes. Limit diode forward current to maximum current ratings. 2. Typical values are for design aid only, not guaranteed and not subject to production testing. 3. The algebraic convention whereby the most negative value is a minimum, and most positive value is a maximum, is used in this datasheet. 4. OFFisolation = 20 V V S , where VS = input to OFF switch, and VD = output due to VS. D 5. ID(ON) is leakage from driver into “ON” switch. 6. Period of Reset (RS) pulse must be at least 50µs during or after power ON. 7. Parameter not tested. Parameter guaranteed by design or characterization. Waveforms and Test Circuits 3V WR 3V 1.5V 1.5V RS 0 0 tRS tWW tWD tDW tOFF(RS) 3V VO 2.0V A0, A1, (A2) EN 0 0.8V SWITCH OUTPUT 0.8VO 0V FIGURE 1. WR TIMING WAVEFORMS FIGURE 2. RS TIMING WAVEFORMS 10-61 DG526, DG527, DG528, DG529 Waveforms and Test Circuits (Continued) +15V +15V +2.4V V+ EN V+ ±10V S1 DG528* EN DG529* RS RS S2 THRU S7 S2A THRU S4A, DA S2B, AND S3B A0 A2 LOGIC INPUT ± S8 A1 WR A0 SWITCH OUTPUT VD V1MΩ 50Ω S4B 10V D GND ±10V S1B A1 LOGIC INPUT 10V SWITCH OUTPUT VDB DB WR GND 35pF ± +2.4V V- 50Ω 1MΩ -15V 35pF -15V FIGURE 3A. tTRANSITION SWITCHING TIME TEST CIRCUIT FIGURE 3B. tTRANSITION SWITCHING TIME TEST CIRCUIT * Similar connections for DG526 * Similar connections for DG527 3V 50% 0 VS1 0.8VS1 SWITCH OUTPUT VD 0 0.8VS8 VS8 S8 ON TRANSITION S1 ON TRANSITION LOGIC INPUT tR < 20ns tF < 20ns FIGURE 3C. tTRANSITION SWITCHING TIME WAVEFORM +15V +2.4V 3V V+ 50% EN 0 RS SWITCH OUTPUT VD DG528* DG529 ALL S AND DA +5V VS 80% A0 A1, (A2) LOGIC INPUT 0V GND tOPEN WR V- 50Ω LOGIC INPUT tR < 20ns tF < 20ns SWITCH OUTPUT VD DB (D) 1kΩ 35pF -15V FIGURE 4A. tOPEN (BREAK-BEFORE-MAKE) SWITCHING TIME WAVEFORM FIGURE 4B. tOPEN (BREAK-BEFORE-MAKE) SWITCHING TIME TEST CIRCUIT * Similar connections for DG526, DG527 10-62 DG526, DG527, DG528, DG529 Waveforms and Test Circuits (Continued) V+ RS EN DG528* S1 +15V +2.4V +15V +2.4V V+ RS -5V EN DG529* -5V S1B S1A THRU S4A, DA, S2B, S3B, S4B S2 THRU S7 A0 A0 A1 A2 EN 50Ω GND SWITCH OUTPUT VD D WR A1 V- EN 1kΩ GND 50Ω SWITCH OUTPUT VDB DB WR V1kΩ 35pF 35pF -15V -15V FIGURE 5A. ENABLE tON AND tOFF SWITCHING TIME TEST CIRCUIT FIGURE 5B. ENABLE tON AND tOFF SWITCHING TIME TEST CIRCUIT * Similar connections for DG526 * Similar connections for DG527 3V 50% 0 tON (EN) tOFF (EN) SWITCH OUTPUT 0 VD 0.1VO 0.9VO VO VS EN tR < 20ns tF < 20ns FIGURE 5C. ENABLE tON AND tOFF SWITCHING TIME WAVEFORMS +15V +2.4V tR < 20ns tF < 20ns V+ EN 3V 1.5V 50% 0V SWITCH OUTPUT VO +5V S1 OR S1B DG528 DG529* A0, A1, (A2) REMAINING SWITCHES tON (WR) RS 0V 0.2VO RS WR DB (D) GND V- SWITCH OUTPUT VO 1kΩ Device must be reset prior to applying WR pulse. WR FIGURE 6A. WRITE tON SWITCHING TIME WAVEFORMS LOGIC INPUT 35pF -15V FIGURE 6B. WRITE tON SWITCHING TIME TEST CIRCUIT * Similar connections for DG526, DG527 10-63 DG526, DG527, DG528, DG529 Waveforms and Test Circuits (Continued) +15V +2.4V tR < 20ns tF < 20ns EN 3V DG528 DG529* +5V A0 A1, (A2) 50% 1.5V RS V+ S1 OR S1B REMAINING SWITCHES 0V tOFF (RS) DB (D) RS SWITCH OUTPUT VO GND 0.8VO SWITCH OUTPUT VO WR V1kΩ RS 35pF -15V FIGURE 7B. RESET tOFF SWITCHING TIME TEST CIRCUIT FIGURE 7A. RESET tOFF SWITCHING TIME WAVEFORMS * Similar connections for DG526, DG527 +15V V+ A0 A1, (A2) 3V +2.4V RS DG528 DG529* EN D Sx 0 VO ∆VO VO WR GND CL = 1000pF V- EN ∆VO is the measured voltage error due to charge injection. The error voltage in Coulombs is Q = CL x ∆VO. -15V FIGURE 8A. CHARGE INJECTION WAVEFORMS FIGURE 8B. CHARGE INJECTION TEST CIRCUIT * Similar connections for DG526, DG527 550 500 400 (D) IO = -200µA VEN = +5V 360 450 320 (C) (B) 300 (A) 250 200 150 100 50 +10V SIGNALS 280 350 RDS(ON) (Ω) RDS (ON) (Ω) 400 V+ = +15V V- = -15V VEN = 2.4V IO = -200µA (A) (B) (C) (D) +10V SIGNALS 240 200 160 120 V+ = +15V, V- = -15V V+ = +12V, V- = -12V V+ = +10V, V- = -10V V+ = +7.5V, V- = -7.5V 80 40 0 -55 0 -15 -13 -11 -9 -7 -5 -3 -1 0 +1 +3 +5 +7 +9 +11 +13 +15 ANALOG SIGNAL VOLTAGE (V) FIGURE 9. RDS(ON) vs ANALOG SIGNAL VOLTAGE vs SUPPLY VOLTAGE -25 0 +25 +45 +70 TEMPERATURE (oC) +100 +125 FIGURE 10. TYPICAL RDS(ON) VARIATION WITH TEMPERATURE 10-64 DG526, DG527, DG528, DG529 Truth Tables DG526 DG527 A3 A2 A1 A0 EN Latching X X X X X Reset X X X X X Transparent Operation X X X X 0 0 0 0 0 0 WR RS ON SWITCH A2 A1 A0 EN 1 Maintains Previous Switch State Latching X X X X X 0 None (Latches Cleared) Reset X X X X 0 0 1 None Transparent Operation X X X 0 1 0 1 1 0 0 0 1 1 0 1 2 0 0 1 0 1 0 1 3 0 0 1 1 1 0 1 0 1 0 0 1 0 0 1 0 1 1 0 1 1 0 0 1 1 1 0 1 WR RS ON SWITCH 1 Maintains Previous Switch State X 0 None (Latches Cleared) 0 0 1 None 0 1 0 1 1 0 1 1 0 1 2 0 1 0 1 0 1 3 4 0 1 1 1 0 1 4 1 5 1 0 0 1 0 1 5 0 1 6 1 0 1 1 0 1 6 1 0 1 7 1 1 0 1 0 1 7 1 1 0 1 8 1 1 1 1 0 1 8 0 0 1 0 1 9 Logic “1” = VAH, VENH ≥ 2.4V 0 0 1 1 0 1 10 1 0 1 0 1 0 1 11 1 0 1 1 1 0 1 12 1 1 0 0 1 0 1 13 1 1 0 1 1 0 1 14 1 1 1 0 1 0 1 15 1 1 1 1 1 0 1 16 Logic “0” = VAL, VENL ≤ 0.8V DG528 A2 A1 A0 EN X X X X X X X X X X X 0 0 0 WR RS DG529 ON SWITCH A1 A0 EN 1 Maintains Previous Switch Condition X X X X 0 None (Latches Cleared) X X X 0 0 1 None X X 0 1 0 1 1 0 0 1 1 0 1 2 0 1 0 1 0 1 3 0 1 1 1 0 1 4 1 0 0 1 0 1 5 1 0 1 1 0 1 6 1 1 0 1 0 1 7 1 1 1 1 0 1 8 RS ON SWITCH 1 Maintains Previous Switch Condition X 0 None (Latches Cleared) 0 0 1 None 0 1 0 1 1 0 1 1 0 1 2 1 0 1 0 1 3 1 1 1 0 1 4 Logic “1”: VAH ≥ 2.4V Logic “0”: VAL ≤ 0.8V 10-65 WR DG526 Die Characteristics DIE DIMENSIONS: 3810µm x 2769µm METALLIZATION: Type: Al Thickness: 10kÅ ± 1kÅ GLASSIVATION: Type: PSG Over Nitride PSG Thickness: 7kÅ ± 1.4kÅ Nitride Thickness: 8kÅ ± 1.2kÅ WORST CASE CURRENT DENSITY: 9.1 x 104 A/cm2 Metallization Mask Layout DG526 PIN 11 S9 PIN 10 S10 PIN 9 S11 PIN 8 S12 PIN 7 S13 PIN 6 S14 PIN 5 S15 PIN 4 S16 PIN 12 GND PIN 3 RS PIN 13 WR PIN 14 A3 PIN 2 NC PIN 15 A2 PIN 1 V+ PIN 16 A1 PIN 28 D PIN 17 A0 PIN 27 V- PIN18 EN PIN 19 S1 PIN 20 PIN 21 S2 S3 10-66 PIN 22 PIN 23 S4 S5 PIN 24 S6 PIN 25 S7 PIN 26 S8 DG527 Die Characteristics DIE DIMENSIONS: 3810µm x 2769µm METALLIZATION: Type: Al Thickness: 10kÅ ± 1kÅ GLASSIVATION: Type: PSG Over Nitride PSG Thickness: 7kÅ ± 1.4kÅ Nitride Thickness: 8kÅ ± 1.2kÅ WORST CASE CURRENT DENSITY: 9.1 x 104 A/cm2 Metallization Mask Layout DG527 PIN 11 S1B PIN 10 S2B PIN 9 S3B PIN 8 S4B PIN 7 S5B PIN 6 S6B PIN 5 S7B PIN 4 S8B PIN 12 GND PIN 3 RS PIN 13 WR PIN 14 NC PIN 2 DB PIN 15 A2 PIN 1 V+ PIN 16 A1 PIN 28 DA PIN 17 A0 PIN 27 V- PIN18 EN PIN 19 S1A PIN 20 PIN 21 S2A S3A 10-67 PIN 22 PIN 23 S4A S5A PIN 24 S6A PIN 25 S7A PIN 26 S8A DG528 Die Characteristics DIE DIMENSIONS: 3100µm x 2083µm METALLIZATION: Type: Al Thickness: 10kÅ ± 1kÅ GLASSIVATION: Type: PSG Over Nitride PSG Thickness: 7kÅ ± 1.4kÅ Nitride Thickness: 8kÅ ± 1.2kÅ WORST CASE CURRENT DENSITY: 9.1 x 104 A/cm2 Metallization Mask Layout DG528 PIN 15 GND PIN 14 V+ PIN 13 S5 PIN 12 S6 PIN 11 S7 PIN 16 A2 PIN 17 A1 PIN 18 RS PIN 10 S8 PIN 1 WR PIN 9 D PIN 2 A0 PIN 8 S4 PIN 3 EN PIN 4 V- 10-68 PIN 5 S1 PIN 6 S2 PIN 7 S3 DG529 Die Characteristics DIE DIMENSIONS: 3100µm x 2083µm METALLIZATION: Type: Al Thickness: 10kÅ ± 1kÅ GLASSIVATION: Type: PSG Over Nitride PSG Thickness: 7kÅ ± 1.4kÅ Nitride Thickness: 8kÅ ± 1.2kÅ WORST CASE CURRENT DENSITY: 9.1 x 104 A/cm2 Metallization Mask Layout DG529 PIN 15 V+ PIN 14 S1G PIN 13 S2B PIN 12 S3B PIN 11 S4B PIN 16 GND PIN 17 A1 PIN 18 RS PIN 10 S8A PIN 1 WR PIN 9 DA PIN 2 A0 PIN 8 S4A PIN 3 EN PIN 4 V- 10-69 PIN 5 S1A PIN 6 S2A PIN 7 S3A