DIP40

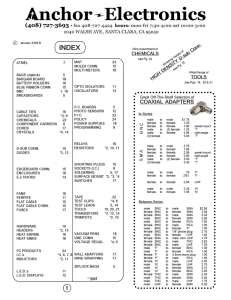

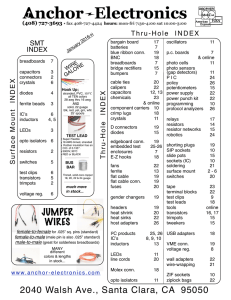

advertisement

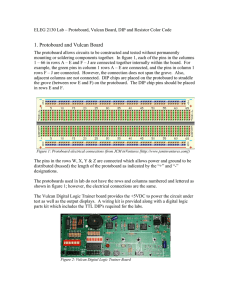

DIP40 MOSIS Ceramic Packaging Connections and Information MOSIS offers as a standard part an 40 lead dual-inline package (DIP). This package is Kyocera KD-78163 or equivalent with a 0.310" cavity (topside). The following diagram depicts the bonding pad to pin connectivity as viewed from the top of the package (or the top of the socket into which the package is plugged), with the index at the upper right corner. 20 1 +----------------------------------------+ | | | | | | | ---| | | | | ---| | | | | | | +----------------------------------------+ 21 40 Top View Package cavity top view: Top view chip placement in 40 pin dip package: Top view finished chip placed in 40 pin dip package: 20 1 +----------------------------------------+ | | | | | | | ---| | | | | ---| | | | | | | +----------------------------------------+ 21 40 Top View 1 pin Signal name for each pin of the 40 pin dip package, example of intel 80C51 microcontroller: