Thin Solid Films 369 (2000) 387±389

www.elsevier.com/locate/tsf

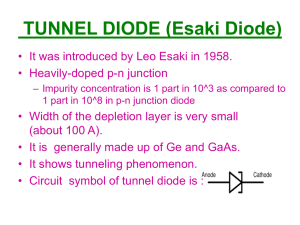

A vertical MOS-gated Esaki tunneling transistor in silicon

t

d

te gh

i

ec yr

ot p

pr co

by

W. Hansch*, C. Fink, J. Schulze, I. Eisele

UniversitaÈt der Bundeswehr MuÈnchen, Institut fuÈr Physik, D-85577 Neubiberg, Germany

Abstract

For the ®rst time a vertical, MOS gated tunneling transistor in silicon is fabricated. The necessary sharp doping pro®le structure is created

by means of MBE. Pronounced transistor action due to Esaki tunneling is demonstrated at room temperature. At a low supply voltage of 20.2

V a current gain of three magnitudes with saturation behaviour is achieved. MOS-gate, low supply voltage and exponential current increase

make this device attractive for ULSI applications. q 2000 Elsevier Science S.A. All rights reserved.

Keywords: Molecular beam epitaxy; Vertical tunneling device; Esaki diode

1. Introduction

Tunneling devices are thought to be possible candidates

for post silicon MOSFETs. Increase in speed by quantummechanical tunneling is one bene®t, but also higher functionality of quantum devices is an advantage. A rich spectra

of possible tunneling transistors is proposed and fabricated

in various materials and heterostructures [1]. Although

some of these devices are quite successful according to

some (but not all) benchmarks, none has found large-scale

commercial application for general-purpose digital and

analog electronics to date. High volume production should

be based on silicon to integrate well with existing conventional logic circuitry. Based on our vertical MOSFET technology [2,3] we modi®ed the fabrication process to establish

gate-controlled Esaki tunneling for transistor action in a

silicon device.

2. Device structure

The device structure consists of a MOS-gated pin diode

and was proposed by Quinn et al. [4] to study the physics of

a two-dimensional electron channel. Koga and Toriumi [5]

fabricated such a device in planar technology on SIMOX

wafers and were focused on the demonstration of a negative

differential conductance (NDC) in forward direction at

room temperature. To achieve good transistor action with

* Corresponding author. Present address: Technische Universitaet

Muenchen, LS Technische Elektronik, D-80290 Muenchen, Germany.

Tel.: 149-89-6004-4037; fax: 149-89-6004-3877.

E-mail address: walter.hansch@unibw-muenchen.de (W. Hansch).

high tunneling performance we fabricated a vertical, MOSgated pin structure by means of MBE as depicted in Fig. 1.

On a highly n 1-doped silicon substrate (0.015 V cm,

(100), acting as the source electrode) 100 nm intrinsic silicon was grown in an ultra-high vacuum multichamber

system. The top region (acting as the drain electrode) was

formed by the deposition of a highly-doped boron deltalayer and 300 nm p 1-contact region. The delta-layer [6]

consists of a peak doping amount around 10 20 cm 23 and a

1/10th width of 3 nm. This delta-layer provides the necessary abrupt p±n-junction for Esaki-tunneling [7] and transistor action. The grown layer system was mesa-etched for

device patterning and isolation. On the vertical side walls a

gate oxide with a thickness of 20 nm was grown and covered

with n 1 poly-silicon. The gates were patterned and isolated

with a low-pressure chemical vapor deposited (LPCVD)

nitride. Finally the contact holes were opened in the nitride

and a double layer of Ti/W and Pt was used for metallization.

3. Device operation

Without an applied gate voltage the vertical structure acts

as a pin diode where the p 1 and n 1 region are separated by

100 nm intrinsic silicon. This I±V characteristics is indicated

in the simulation (Fig. 2) by open squares.

The simulation was performed by using the theoretical

equations for thermal emission of electrons over a p±n-junction, excess and tunneling current. By applying a positive

gate voltage an electron channel is in¯uenced beneath the

gate oxide as in a conventional MOSFET. The contact

region between the n 1-channel and the p 1 drain now

forms the tunneling barrier. The amount of electrons

0040-6090/00/$ - see front matter q 2000 Elsevier Science S.A. All rights reserved.

PII: S 0040-609 0(00)00896-8

388

W. Hansch et al. / Thin Solid Films 369 (2000) 387±389

t

d

te gh

i

ec yr

ot p

pr co

by

Fig. 3. Experimental I±V output characteristics of an Esaki-FET.

Fig. 1. Schematic view of the vertical Esaki-tunneling ®eld-effect transistor

(Esaki-FET).

supported by the channel and the electrical ®eld strength of

the tunneling region can be controlled by the MOS gate

®eld. Due to the silicon band structure the change in I±V

characteristics from pin-characteristics to tunneling characteristics is expected to be small in forward direction, theoretically a peak-valley ratio of two may be achievable.

Anyhow, in the reverse direction a signi®cant change in

current from the very low reverse current of the pin-diode

to the exponential increasing current of a tunneling diode

can be expected when varying the gate voltage.

4. Electrical measurement and discussion

Experimental I±V characteristics are shown in Figs. 3 and

4. In forward direction a possible regime of NDC can not be

detected (Fig. 3).

Fig. 2. Simulation of an ideal tunneling diode, including the contributions

of thermal pin-current and excess current.

The reason is that the same Ti/W metallization was used

for the n 1 source and p 1 -drain. The advantage of a one

step metallization is compromised by the formation of a

serial Schottky diode at the p 1-Ti/W junction, which limits

the current ¯ow in forward direction.

In reverse direction the predicted change from pin-diode

to tunneling characteristics by the MOS gate bias can be

seen. The high gate voltages, which can be applied show

the good quality and homogeneity of the gate oxide grown

at the vertical, etched mesa side wall.

The input I±V characteristics is shown in Fig. 4.

For low values of supply voltage (V SD # 20:2 V) a

remarkable current gain of three magnitudes is achieved.

The `threshold voltage' for tunneling is about V G , 3 V,

which is expected to be dependent on the doping of the

intrinsic layer, the oxide thickness and the actual electric

®eld in the tunnel region. The saturation behavior is clearly

seen. The value of the leakage current is about 4 £ 10 212 A/

mm gate width at a projected supply voltage of 0.2 V. In

comparison to a MOSFET with identical channel length

(from the SIA-roadmap [8] a leakage current of a few nA/

mm is acceptable for ULSI sub-100 nm MOSFETs at 1 V

supply voltage), the leakage current at 21 V bias is about

Fig. 4. Experimental input I±V characteristics of an Esaki-FET.

W. Hansch et al. / Thin Solid Films 369 (2000) 387±389

one magnitude lower. In principle, a much smaller leakage

current can be expected over an n 1±p 1-barrier in an EsakiFET than over the lower n 1±p±n 1 barrier of a MOSFET.

Currently we are investigating whether a further reduction

of the leakage current can be achieved. Anyhow, the high

reduction of the leakage current due to the tunneling barrier

is an additional advantage for future ULSI low power applications.

characteristics on device layout, oxide thickness, doping

pro®les and electric ®elds need further investigations.

References

[1] For an overview see for example: S. Luryi, A. Zaslavsky, Quantum

effect and hot-electron devices, in: S.M. Sze (Ed.), Modern Semiconductor Device Physics, Wiley, New York, 1998.

[2] W. Hansch, V.R. Rao, C. Fink, F. Kaesen, I. Eisele, Thin Solid Films

321 (1998) 206.

[3] V.R. Rao, W. Hansch, I. Eisele. IEDM' 97, Tech. Dig, p. 811

[4] J.J. Quinn, G. Kawamoto, B.D. McCombe, Surf. Sci. 73 (1978) 190.

[5] J. Koga, A. Toriumi. IEDM'96, Tech. Dig, p. 265

[6] See for example: H. BaumgaÈrtner, W. Hansch, F. Wittmann, I. Eisele,

Molecular beam epitaxy for silicon nanoelectronics, in: S.G. Pandalai

(Ed.), Current Topics in Crystal Growth Research, Vol. 2, 1995, p. 283.

[7] L. Esaki, Phys. Rev. 109 (1958) 603.

[8] The National Technology Roadmap for Semiconductors, SIA Semiconductor Industry Association, 1997, Santa Clara, CA.

t

d

te gh

i

ec yr

ot p

pr co

by

5. Conclusion

First measurements on the fabricated vertical Esakitunneling transistors exhibit several advantages for future

ULSI, combining the advantages of bipolar and MOS

devices: fast switching due to an exponential increase in

current with gate voltage, safe on/off switching at very

low voltage levels and MOS gate control without steadystate current consumption. The dependence of tunneling

389