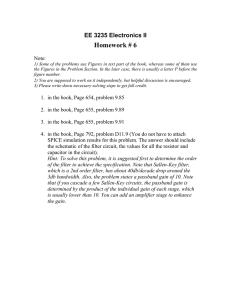

CMOS INTEGRATED LC Q-ENHANCED RF FILTERS FOR

advertisement