Compact Modeling of SOI-LDMOS Transistor including Impact

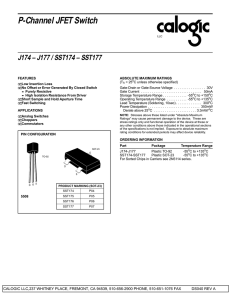

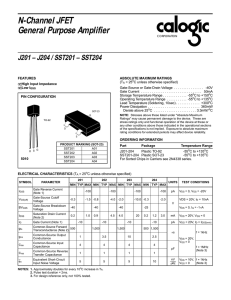

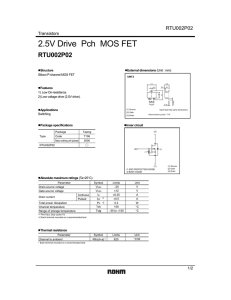

advertisement