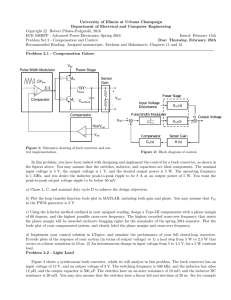

Master`s Thesis:

advertisement