Heat and Power Management for High Performance Integrated

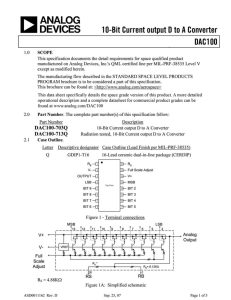

advertisement